## Robust Design of Low-voltage OTFT Circuits for Flexible Electronic Systems

Zhaoxing Qin

## Abstract

Flexible electronics have attracted significant attention as an emerging technology for use in a wide range of internet-of-things (IoT) applications. In particular, organic thin-film transistors (OTFTs) have attracted great attention and are the subject of intense research due to their appealing properties such as flexibility, biocompatibility, and low supply voltage. In addition, OTFTs can be fabricated through low-cost and low-temperature printing processes. With the printing process, OTFT circuits can be fabricated on various substrates, such as flexible plastic film. As a result of intensive research efforts, considerable improvements have been made to the performance of OTFTs. Various applications that use OTFTs as principal active device components have been reported.

Although OTFT applications such as flexible sensors or smart labels are being studied, most of the current researches focus on the materials and the structure of the sensors that perform signal detection. Meanwhile, how to treat the data in these systems is also an essential issue. For instance, in a flexible sensor, after the data are detected, memory is needed to save these data. It should also be considered how to protect these data. Thus, the circuits used to control and compute the data in these systems are required. At present, most of these functions rely on external silicon devices. However, the data transmission between the OTFTs and silicon devices requires additional time and power. Implementing a OTFTs and silicon hybrid system also decreases the advantage of OTFTs low-cost fabrication process. Therefore, the OTFT circuitry considering treatments of local signal data is required.

This dissertation is devoted to use OTFT circuits to realize the local treatments of data in organic systems from three aspects, security, storage, and processing. However, being fundamentally different from silicon technologies, traditional silicon circuit design topology is not suitable for OTFTs. The OTFTs are unipolar, in which p-type transistors are much stronger than n-type transistors. In addition, OTFTs, especially n-type transistors, are sensitive to bias-stress and humidity in the air, resulting in a temporal reduction of mobility. Hence, in this dissertation, several circuit design typologies are also proposed to deal with these intrinsic detects of OTFTs.

In the first part of this dissertation, an OTFT physical unclonable function (PUF) is proposed for hardware security. The OTFT PUF can be used for privacy protection for the information collected by flexible sensors, or smart packaging to ensure the authenticity of products. A current mirror array is used for the proposed OTFT PUF. The current mirror can achieve self-compensation for the unavoidable degradation of OTFTs. In this part, two types of PUFs are proposed; one pursues area efficiency and the other aims for improved robustness. Through fabrication and measurement of the two OTFT PUFs, it demonstrates that the fabricated OCM-PUFs achieved 95% reliability, showing that the proposed PUFs achieve a high tolerance against response changes caused by device aging.

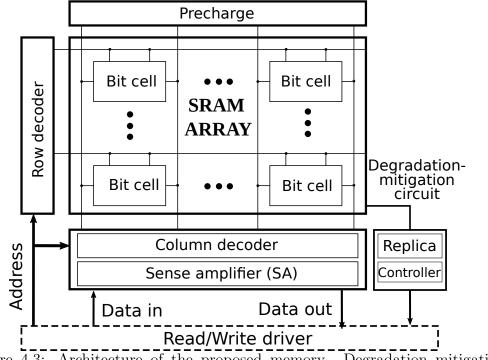

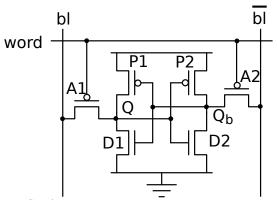

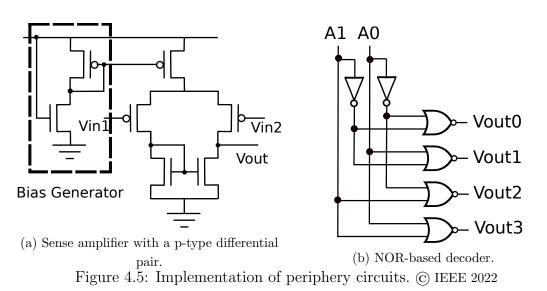

The second part of this dissertation focuses on an OTFT SRAM used for data storage. In traditional silicon CMOS SRAM construction, the pull down n-type transistors need to be designed strongest to sustain a stable operation, which is difficult for unipolar OTFTs. The general OTFT-based SRAM construction uses a pseudo-CMOS structure with only p-type transistors. However, the pseudo-CMOS topology decreases the stability and area efficiency of circuits. In this part, a CMOS design using p-type access transistors is adapted for SRAM cells to gain high stability and area efficiency. Then, the periphery circuits, decoder, and sense amplifier, for the SRAM array are designed. Moreover, to extend retention time, a degradation-mitigation circuit, based on a pseudo-CMOS design, is proposed. This circuit can self-detect degradation and automatically perform a process to mitigate device degradation at the necessary time periods. Through test chip measurements, the proposed SRAM cell achieves 50% area reduction and 2.5x static noise margin improvement compared to existing OTFT SRAM cells. The retention time of SRAM memory can be extended to at least 3x via the proposed degradation-mitigation circuit.

The ability of data processing is discussed in the last part of this dissertation. As demonstrated above, for general logic circuits, traditional CMOS design is not suitable for OTFTs, due to the unbalance of n-type transistors and p-type transistors. An alternative design topology, pass transistor logic (PTL), is proposed in this part. The PTL decreases the transistor counts and mainly depends on the strong p-type transistors. A full adder, which is the essential unit in logic circuits, is used as an example to demonstrate the construction of a PTL circuits. Compared to a traditional CMOS full adder, the transistor counts of PTL adder can be reduced by 50%. Furthermore, for full data processing, a processor based on PTL is discussed in this part. The processor uses one instruction set computer (OISC) architecture. The OISC uses only one instruction to execute all operations, hence the circuit is extremely simple and lightweight. The operation of each component in the OISC processor is

confirmed through test chip measurements, presenting the feasibility of the OTFT OISC processor.

ABSTRACT

## Acknowledgments

Undertaking this Ph.D. has been a truly life-challenging experience for me. I express my gratitude to all people who helped me.

First and foremost, I would like to express my sincere gratitude to my advisor Prof. Takashi Sato for his consistent support and guidance during the running of my Ph.D. study. His immense knowledge and plentiful experience have encouraged me in all the time of my academic research and daily life. It was a great privilege and honor to work and study under his guidance. Without his assistance and inspiration, I would not have completed this challenging project.

Second, I would like to express my deep gratitude to the rest of my dissertation committee, Prof. Masanori Hashimoto and Prof. Kiichi Niitsu for their precious reviews and comments in examining this dissertation. Their harsh questions and generous advice have polished this dissertation into a much better shape.

Next, I would like to express my gratitude to previous and current lab members at Integrated Systems Engineering Laboratory. Prof. Michihiro Shintani and Ms. Shuko Nishiyama are the primary figures in helping with my personal and academic lives. Discussions with Prof. Hiromitsu Awano and Prof. Ryo Shirai helped me to learn a lot about research methodology and various interdisciplinary knowledge. I also thank all students in my lab for their kind help and support that have made my study and life in Japan a wonderful time.

I would like to appreciate Dr. Kazunori Kuribara and Dr. Yasuhiro Ogasahara of National Institute of Advanced Industrial Science and Technology (AIST). Collaboration with them is a wonderful experience. Their vast wisdom and wealth of experience have inspired me throughout my study.

Additionally, I acknowledge support from the Japan Society for the Promotion and Science (JSPS) for their financial support as a Fellowship for Young Scientists (DC2).

Last but not least, I am truly grateful to my parents, Xiaotie Qin and Hong Yu, for their unfailing support and continuous encouragement throughout my long student time.

ACKNOWLEDGMENTS

## Contents

| A                      | bstra  | let                                                | i   |

|------------------------|--------|----------------------------------------------------|-----|

| A                      | ckno   | wledgments                                         | v   |

| С                      | onter  | nts                                                | vii |

| $\mathbf{L}\mathbf{i}$ | ist of | Figures                                            | xi  |

| $\mathbf{L}\mathbf{i}$ | ist of | Tables                                             | xv  |

| 1                      | Intr   | roduction                                          | 1   |

|                        | 1.1    | Flexible Electronics                               | 1   |

|                        | 1.2    | Motivation                                         | 2   |

|                        | 1.3    | Approaches                                         | 4   |

|                        |        | 1.3.1 OTFT PUF for Data Security                   | 4   |

|                        |        | 1.3.2 OTFT SRAM for Data Storage                   | 5   |

|                        |        | 1.3.3 OTFT Arithmetic Circuits for Data Processing | 5   |

|                        | 1.4    | Organization                                       | 6   |

| <b>2</b>               | Pre    | liminaries of Organic thin film transistors        | 9   |

|                        | 2.1    | OTFTs structure                                    | 9   |

|                        | 2.2    | Fabrication process of OTFTs                       | 11  |

|                        | 2.3    | Operation principle and device model of OTFTs      | 14  |

|                        | 2.4    | Electronic characteristic of OTFTs                 | 16  |

| 3                      | Phy    | vsical Unclonable Function using OTFTs             | 19  |

|                        | 3.1    | Introduction                                       | 19  |

|                        | 3.2    | Background                                         | 21  |

|                        |        | 3.2.1 Physically unclonable function               | 21  |

|                        |        | 3.2.2 Organic thin-film transistor PUF             | 22  |

|                        | 3.3    | Organic current mirror array                       | 24  |

|                        |        | 3.3.1 Circuit architecture                         | 24  |

|          |     | 3.3.2 Operation as a PUF                                                                                                                                           |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.4 | Experimental Results of OCM-array                                                                                                                                  |

|          | 0.1 | 3.4.1 Current mirror                                                                                                                                               |

|          |     | 3.4.2 OCM-array                                                                                                                                                    |

|          |     | 3.4.3 Resistance to degradation                                                                                                                                    |

|          | 3.5 | The evaluation of OCM-PUF                                                                                                                                          |

|          | 0.0 | 3.5.1 Randomness                                                                                                                                                   |

|          |     | 3.5.2 Reliability                                                                                                                                                  |

|          |     | 3.5.3 Reference current                                                                                                                                            |

|          |     | 3.5.4 Comparison                                                                                                                                                   |

|          | 3.6 | Summary                                                                                                                                                            |

|          | 0.0 | Summary                                                                                                                                                            |

| <b>4</b> | Sta | tic Random Access Memory using OTFTs 41                                                                                                                            |

|          | 4.1 | Introduction                                                                                                                                                       |

|          | 4.2 | Background and prior art                                                                                                                                           |

|          |     | 4.2.1 Memory in sensor systems                                                                                                                                     |

|          |     | 4.2.2 Standard SRAM cell                                                                                                                                           |

|          |     | $4.2.3  \text{Cell stability}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                    |

|          |     | 4.2.4 Conventional SRAM circuits                                                                                                                                   |

|          | 4.3 | Hybrid CMOS and pseudo-CMOS Organic Memory Architecture 44                                                                                                         |

|          |     | 4.3.1 Memory cell                                                                                                                                                  |

|          |     | 4.3.2 Periphery circuits                                                                                                                                           |

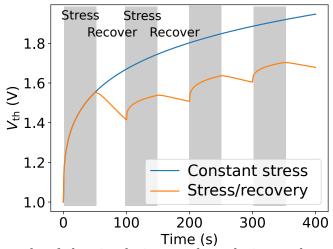

|          |     | 4.3.3 Degradation mitigation circuit                                                                                                                               |

|          | 4.4 | Transistor Size Optimization through Simulation                                                                                                                    |

|          | 4.5 | Experimental Validation                                                                                                                                            |

|          |     | 4.5.1 SRAM memory cell                                                                                                                                             |

|          |     | 4.5.2 SRAM array operation                                                                                                                                         |

|          |     | 4.5.3 Degradation-mitigation circuit                                                                                                                               |

|          | 4.6 | Summary                                                                                                                                                            |

|          |     |                                                                                                                                                                    |

| <b>5</b> |     | s Transistor Logic using OTFTs 65                                                                                                                                  |

|          | 5.1 | Introduction                                                                                                                                                       |

|          | 5.2 | Background                                                                                                                                                         |

|          |     | 5.2.1 Conventional OTFT logic gate 6'                                                                                                                              |

|          |     | 5.2.2 Pass transistor logic $\ldots \ldots \ldots$ |

|          |     | 5.2.3 One Instruction Set Computer                                                                                                                                 |

|          | 5.3 | Pass Transistor Logic Architecture                                                                                                                                 |

|          |     | 5.3.1 Pass transistor logic tree                                                                                                                                   |

|          |     | 5.3.2 Gain stage $\ldots \ldots \ldots$            |

|          | 5.4 | PTL-based OISC Processor                                                                                                                                           |

|          |     | 5.4.1 Architecture                                                                                                                                                 |

|    |       | 5.4.2 Circuit construction                          | '5 |

|----|-------|-----------------------------------------------------|----|

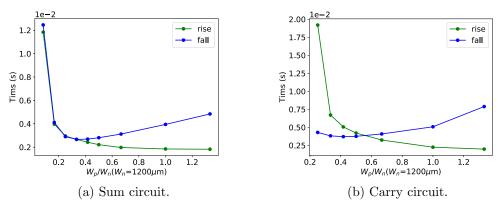

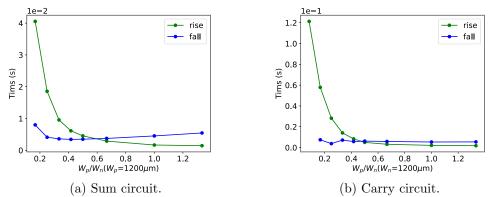

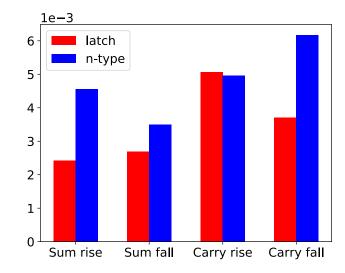

|    | 5.5   | Transistor Size Optimization                        | 7  |

|    | 5.6   | Experimental results                                | '8 |

|    |       | 5.6.1 PTL-based full adder                          | '9 |

|    |       | 5.6.2 OISC processor                                | 60 |

|    | 5.7   | Summary                                             | 54 |

| 6  |       | nclusion8Summary of this dissertation8Future works8 | 87 |

| Bi | bliog | graphy 9                                            | 1  |

| Li | st of | Publications                                        | 1  |

CONTENTS

# List of Figures

| 1.1  | Conceptual illustration of a flexible system                                                                | 3  |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Structure of low voltage organic thin-film transistor. © IEEE 2020                                          | 10 |

| 2.2  | Structures of low voltage organic thin-film transistors                                                     | 11 |

| 2.3  | Fabrication process of OTFTs                                                                                | 13 |

| 2.4  | Photo of a fabricated OTFTs chip. Substrate is a $5 \text{ cm} \times 5 \text{ cm}$                         |    |

|      | glass. A flexible film substrate can also be used                                                           | 14 |

| 2.5  | Drain current characteristics of p- and n-type OTFTs with a size                                            |    |

|      | of W/L=1200 $\mu$ m/50 $\mu$ m. $V_{ds}$ =3.0 V. © IEEE 2022                                                | 17 |

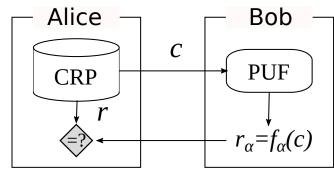

| 3.1  | OCM-array as an OCM-PUF, and its use model. $\bigodot$ IEEE 2020 $% = 100000000000000000000000000000000000$ | 20 |

| 3.2  | Typical use of PUFs. © IEEE 2020                                                                            | 23 |

| 3.3  | Example PUF-based authentication. © IEEE 2020                                                               | 23 |

| 3.4  | Construction of ring oscillator PUF [1]                                                                     | 24 |

| 3.5  | Cell of Buskeeper-PUF [2]                                                                                   | 24 |

| 3.6  | Schematic diagram of OCM-PUF1. © IEEE 2020                                                                  | 25 |

| 3.7  | Schematic diagram of OCM-PUF2. © IEEE 2020                                                                  | 25 |

| 3.8  | Current compensation in the current mirror circuit. © IEEE 2020                                             | 27 |

| 3.9  | The measurement environment. © IEEE 2020                                                                    | 28 |

| 3.10 | Measurement results of n-type current mirrors. © IEEE 2020                                                  | 29 |

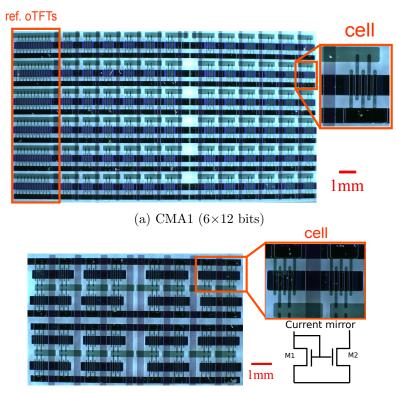

| 3.11 | Microphotographs of the two types of OCM-PUF fabricated. $\bigodot$                                         |    |

|      | IEEE 2020                                                                                                   | 30 |

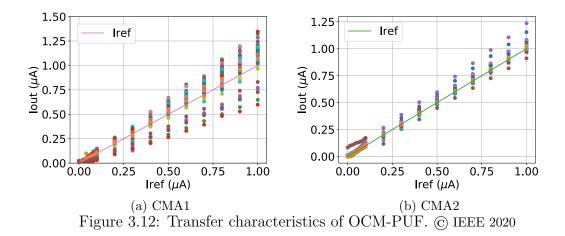

| 3.12 | Transfer characteristics of OCM-PUF. © IEEE 2020                                                            | 30 |

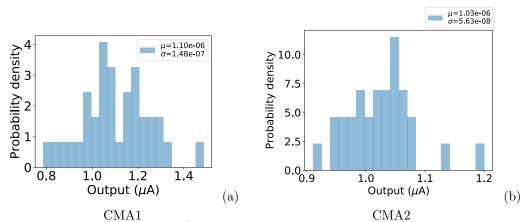

| 3.13 | Variation of output current when $I_{\text{ref}} = 1 \mu\text{A}$ . © IEEE 2020                             | 31 |

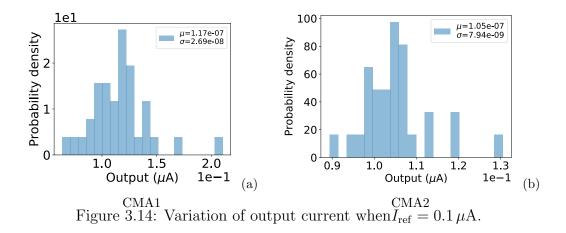

| 3.14 | Variation of output current when $I_{ref} = 0.1 \mu A.$                                                     | 31 |

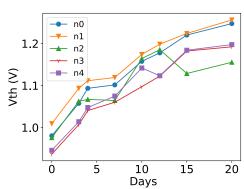

| 3.15 | Temporal threshold voltage change of OTFTs in CMA1. © IEEE                                                  |    |

|      | 2020                                                                                                        | 32 |

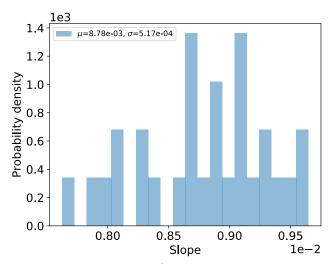

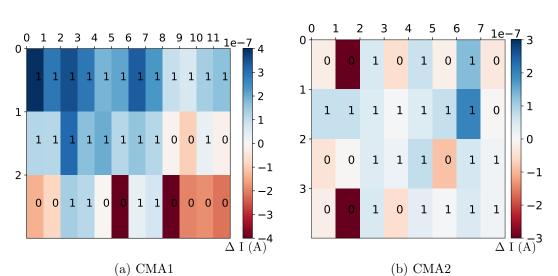

| 3.16 | Temporal mobility change of OTFTs in CMA1. $\bigodot$ IEEE 2020 $$                                          | 32 |

| 3.17 | Temporal gate voltage change of current mirrors in CMA2. $\bigodot$                                         |    |

|      | IEEE 2020                                                                                                   | 32 |

| 3.18  | Temporal output current change of current mirrors in CMA2. $\bigcirc$ IEEE 2020                                       | <sup>32</sup> |

|-------|-----------------------------------------------------------------------------------------------------------------------|---------------|

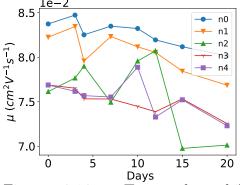

| 3.19  |                                                                                                                       | 33            |

|       |                                                                                                                       | <b>3</b> 4    |

|       |                                                                                                                       | 35            |

|       |                                                                                                                       | 86            |

|       | 1 0 0                                                                                                                 | <b>8</b> 6    |

|       |                                                                                                                       | 57<br>137     |

|       |                                                                                                                       | 88            |

|       | ĕ                                                                                                                     | <b>3</b> 9    |

| 0.20  | TOM as a function of aging. (C) TEEE 2020                                                                             | 9             |

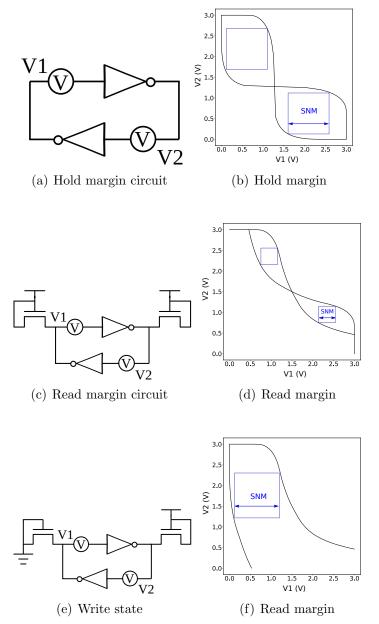

| 4.1   | The test circuits and bufferfly diagram indicating static noise                                                       | . 4           |

| 4.0   |                                                                                                                       | 4             |

| 4.2   | $rac{1}{2}$                                                                                                           | 5             |

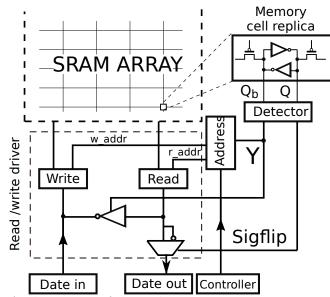

| 4.3   | Architecture of the proposed memory. Degradation mitigation                                                           |               |

|       | circuit is added to enhance lifetime of the memory array. © IEEE                                                      | C             |

| 4 4   |                                                                                                                       | 6             |

| 4.4   |                                                                                                                       | 17            |

| 4.5   |                                                                                                                       | 8             |

| 4.6   | Example of the simulation on degradation and recovery of $V_{\rm th}$ . ©                                             | 0             |

| 4 🗁   |                                                                                                                       | 9             |

| 4.7   | 0 0                                                                                                                   | 51            |

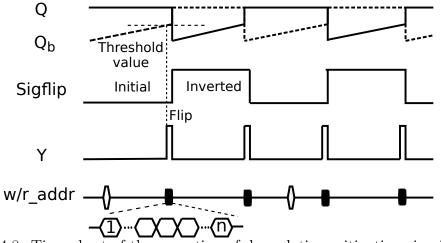

| 4.8   | Time chart of the operation of degradation-mitigation circuit for                                                     | 1             |

| 1.0   |                                                                                                                       | 51            |

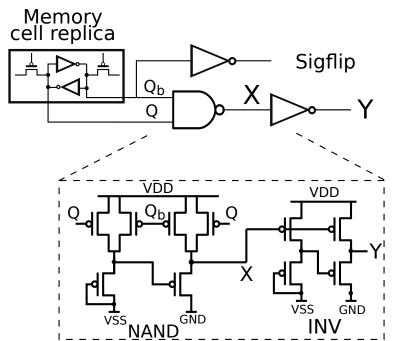

| 4.9   | Degradation mitigation circuit with pseudo-CMOS design. ©                                                             |               |

| 4 1 0 |                                                                                                                       | 52            |

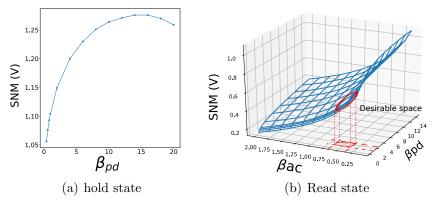

| 4.10  | Simulation results of SNM in hold and read states at 3 V supply                                                       | · ∩           |

| 1 1 1 |                                                                                                                       | 53            |

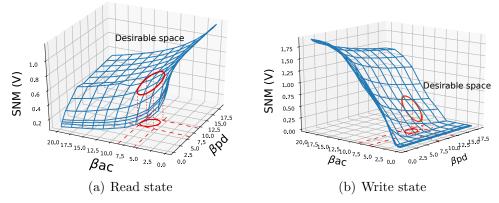

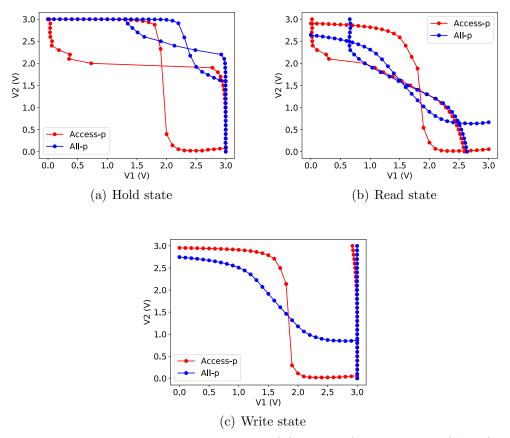

| 4.11  | 8                                                                                                                     |               |

|       | optimal transistor sizes in read and write SNM at 3 V supply                                                          | 1             |

| 4 1 9 |                                                                                                                       | 64            |

| 4.12  | Simulation results for All-p SRAM structure for finding optimal                                                       |               |

|       | transistor sizes in read and write SNM at 3V supply volt-                                                             | 5             |

| 1 19  |                                                                                                                       | 55<br>.c      |

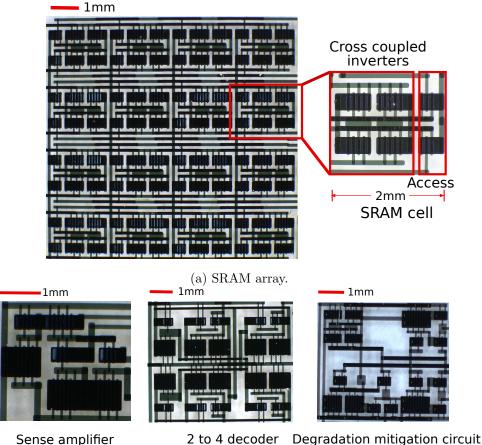

|       |                                                                                                                       | 66            |

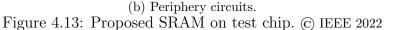

| 4.14  | The measurement results of SNM in Access-p and All-p SRAM                                                             |               |

|       | cells at 3 V supply voltage. (Copyright (2021) The Japan Society of                                                   | 57            |

| 115   |                                                                                                                       | 1             |

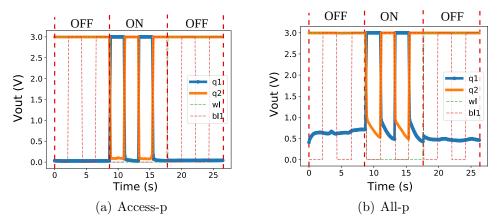

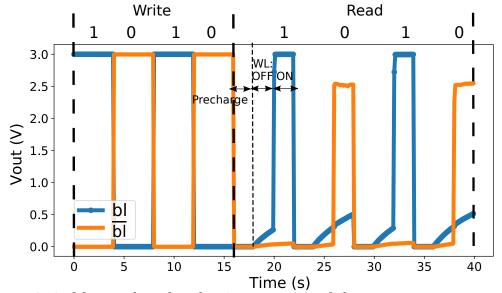

| 4.10  | The write operation of Access-p and All-p SRAM cells. ( <i>Copyright</i> (2021) The Japan Society of Amplied Physics) | 58            |

|       | (2021) The Japan Society of Applied Physics)                                                                          | 0             |

| 4.16         | Write and read operations of the proposed SRAM cell. ( <i>Copyright</i> (2021) The Japan Society of Applied Physics)              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

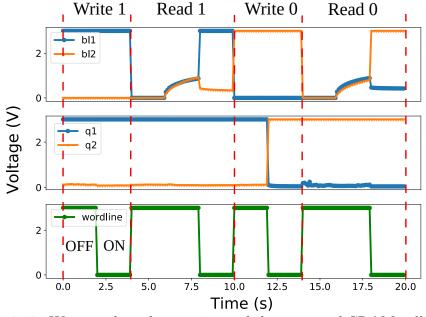

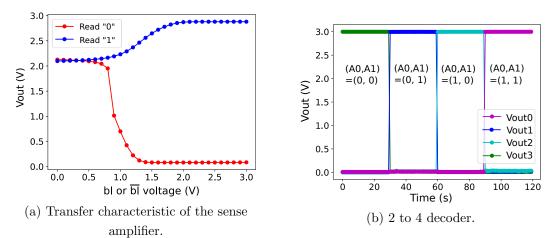

| 4.17         | Measurement results of periphery circuits. © IEEE 2022 6                                                                          |

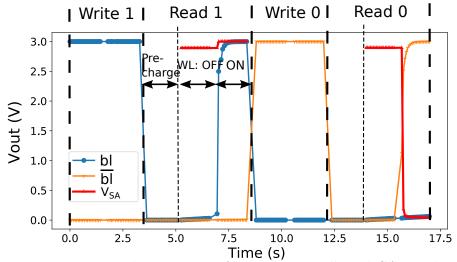

|              | Measured operation of a memory cell and SA in the memory                                                                          |

|              | array. © IEEE 2022                                                                                                                |

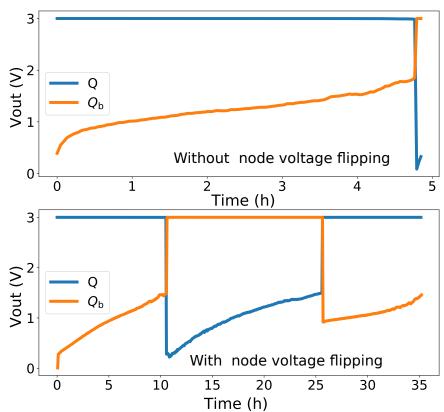

| 4.19         |                                                                                                                                   |

|              | $2022 \dots \dots$                |

| 4.20         | Temporal change in internal node voltages of a memory cell. The stored value flips due to device degradation (top). The retention |

|              | time can be extended significantly through the preventive node                                                                    |

| 4.21         | flipping (bottom). © IEEE 2022                                                                                                    |

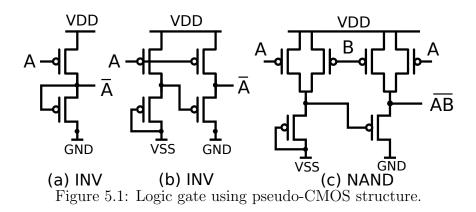

| 5.1          | Logic gate using pseudo-CMOS structure.                                                                                           |

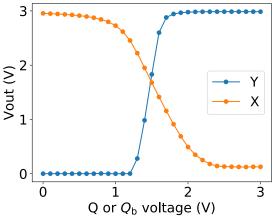

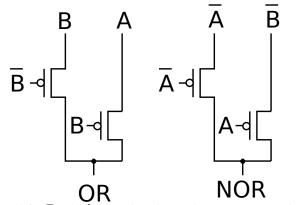

| $5.1 \\ 5.2$ | Basic logic circuits using pass transistor.                                                                                       |

| 5.2          | Output levels of basic pass transistor logic in Fig. 5.2.                                                                         |

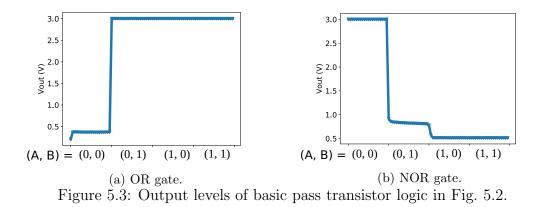

| $5.3 \\ 5.4$ | Architecture of pass transistor logic                                                                                             |

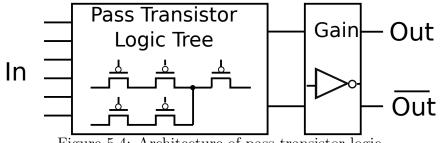

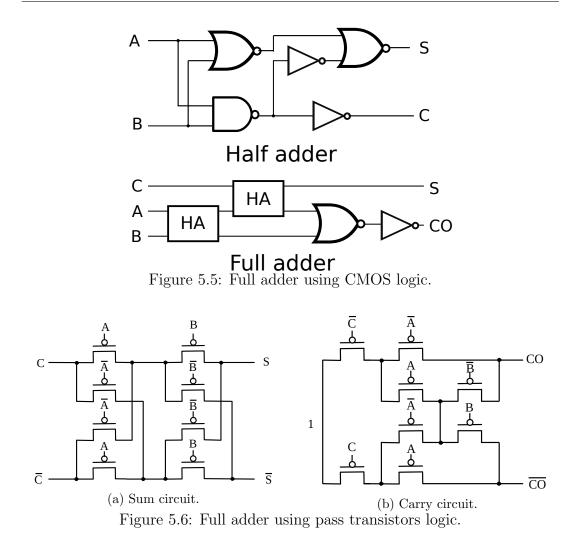

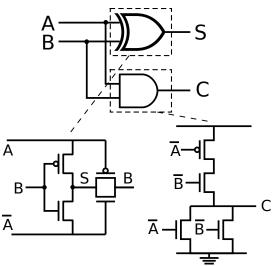

| $5.4 \\ 5.5$ | Full adder using CMOS logic.                                                                                                      |

| 5.6          | Full adder using pass transistors logic.       ••••••••••••••••••••••••••••••••••••                                               |

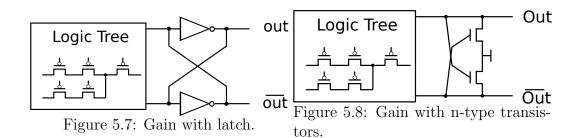

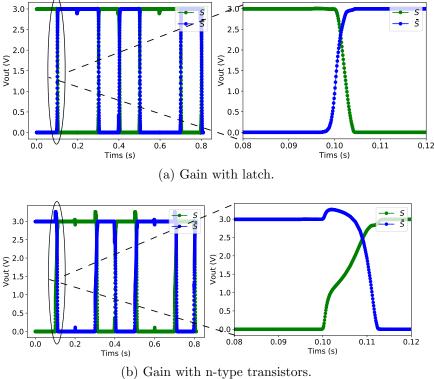

| $5.0 \\ 5.7$ | Gain with latch.                                                                                                                  |

| 5.8          | Gain with n-type transistors.                                                                                                     |

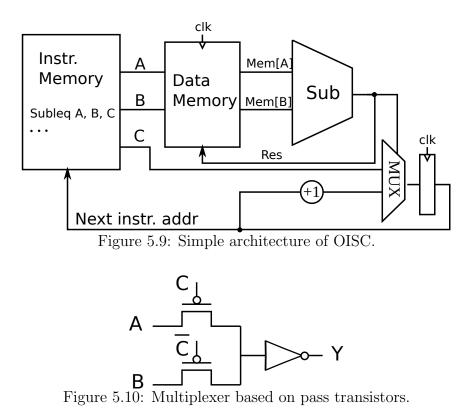

| 5.9          | Simple architecture of OISC.                                                                                                      |

| 5.10         | Multiplexer based on pass transistors.                                                                                            |

|              | Construction of half adder.                                                                                                       |

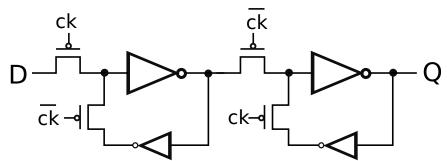

|              | Latch based flipflop with weak feed back invert.                                                                                  |

|              | Transient simulation waveform of sum circuits.                                                                                    |

|              | Simulation results of rise and fall time with latch gain stage                                                                    |

|              | Simulation results of rise and fall time with n-type gain stage.                                                                  |

|              | Comparison of operation time at optimal size                                                                                      |

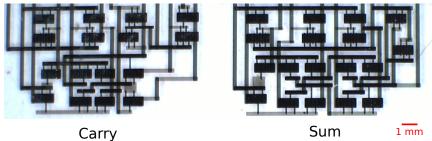

|              | Microphoto of proposed full adder on test chip                                                                                    |

|              | Measurement result of PTL full adder                                                                                              |

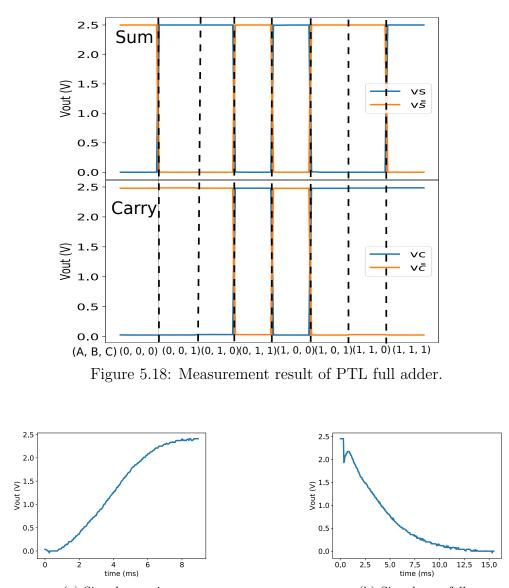

| 5.19         |                                                                                                                                   |

| 5.20         |                                                                                                                                   |

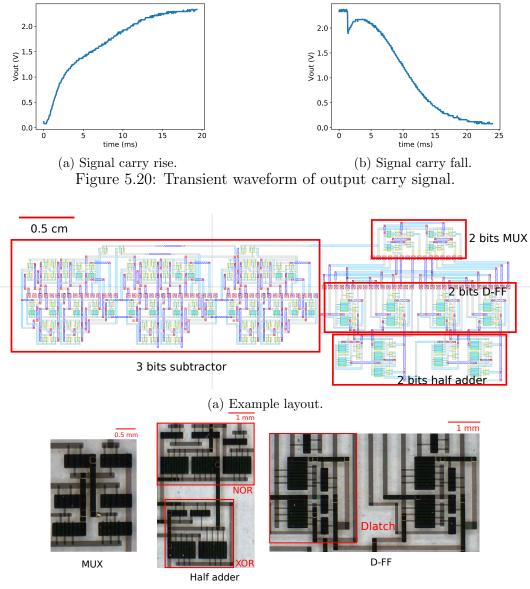

|              | A proposed 2 bits OISC processor.                                                                                                 |

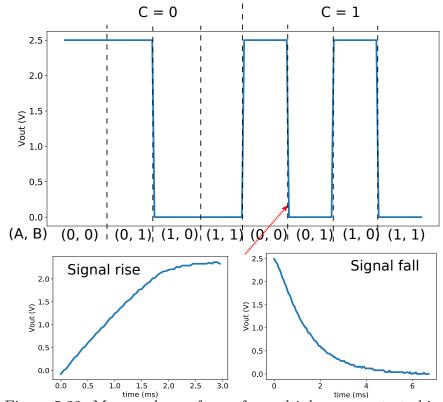

|              | Measured waveform of a multiplexer on a test-chip                                                                                 |

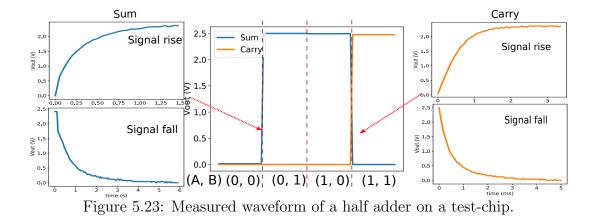

|              | Measured waveform of a half adder on a test-chip.                                                                                 |

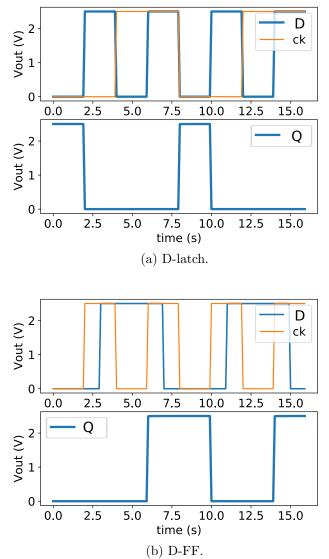

|              | Dynamic characteristics of D-latch and D-FF.                                                                                      |

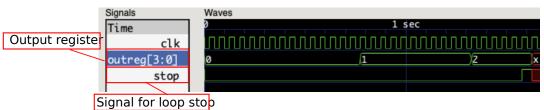

|              | Example OISC simulation output of loop program.                                                                                   |

### LIST OF FIGURES

## List of Tables

| $2.1 \\ 2.2$ | Explanation of each parameter in OTFTs device model Parameters of the degradation model of OTFTs in Eq. 2.8,                       | 15       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | Eq. 2.9, and Eq. 2.10                                                                                                              | 17       |

|              | Randomness of the digital signature $\bigcirc$ IEEE 2020 Required bit and area for different sizes of PUFs. $\bigcirc$ IEEE 2020 . | 34<br>39 |

| 4.1          | Comparison table for thin-film SRAM designs $\ . \ . \ . \ .$                                                                      | 61       |

|              | Device counts of full adder                                                                                                        |          |

## Chapter 1

## Introduction

### **1.1** Flexible Electronics

With the development of IoT society, the amount of information being processed is exploding. The IoT device has emerged as an indispensable infrastructure for our daily lives. As these IoT devices are used in various situations, the demand for a wide range of materials, from traditional hard silicon to soft materials, is required according to the IoT applications. In response to such requirements, organic thin-film transistors (OTFTs) have attracted great attention and are the subject of intense research due to their appealing properties, such as flexibility, lightness, and biocompatibility [3–5]. Owing to their low cost and low temperature process, the OTFTs can be fabricated on various materials, such as flexible plastic films [6, 7]. Additionally, OTFTs can operate at a low supply voltage. Furthermore, in recent years, intensive research efforts significantly improved the performance of OTFTs [8–11]. As a result, various applications that use OTFTs as principal active device components have been reported. Examples include analog-to-digital (A/D) [12] or digital-to-analog (D/A) converters [13], RFID tags [4], microprocessors [14, 15], and flexible sensors [5].

Compared to other flexible thin-film transistors, such as IGZO TFT or ZnO TFT which need high supply voltage, such as 20 V [16, 17], the OTFTs used in this dissertation are driven by a low voltage of 3 V or lower. A simple external power supply such as coin batteries can be the energy source of the OTFTs. Thus, OTFT-based applications can be integrated more easily and safely. Moreover, through the printing process in the fabrication of OTFTs, it is possible to manufacture integrated circuits on a variety of objects. Consequently, everything around us has the ability to process information. For example, a smart label could be printed on a product package with an organic

sensor circuit. Smart labels not only store product information but also detect and store information of surrounding environments during transportation and storage. They also can be disposable with the product package due to the low fabrication cost of the organic circuits. Additionally, in the medical healthcare field, the organic flexible sensor can be used as an active sensor that adheres to the skin to improve sensitivity in detecting biometric information. The sensor can be easily customized by adjusting the position of the electrodes and printing on-demand according to the patient's body shape.

### 1.2 Motivation

At present, researches on organic transistors focus on the materials or structures of sensors for signal detection [8–11]. The processing or control of the signal generally relies on conventional silicon circuits. This results in the loss of the greatest advantage of organic transistors, which is that the entire system can be fabricated in a low cost printing process. Moreover, the power and time required to transmit the sensor signal to the silicon circuitry reduce energy efficiency [18, 19]. For a practical application of organic electronics, circuitry considering treatments of local signal data is required.

In an example of smart labels, owing to the low cost fabrication process, the smart label can be easily fabricated on the packaging material of merchandise, typically on plastic films. The smart label has the ability to store the information about the merchandise, including production date, place of production, lot number, serial number, etc. Additionally, for environmentally sensitive products, such as fresh vegetables, fish, meat, or wines, the recording of the environmental conditions is significantly useful. By storing environmental information such as temperature, humidity, and sunlight exposure, the products can be protected during delivery and storage. In addition, security functions are also important, such as authenticating the products or protecting stored information from malicious attacks. Then, a microprocessor is required to perform simple data processing and control data flow in those systems.

However, OTFT technology is fundamentally different from conventional silicon technology. There are several challenges that OTFT circuits are encountering. The OTFTs are unipolar devices, in which p-type transistors are much stronger than n-type. Compared with n-type transistors, p-type transistors exhibit more than 10x higher on-current and a significantly better on-off current ratio. Device degradation is also a negative feature of OTFTs. The OTFTs are sensitive to bias-stress and the reaction of organic semiconductor and humidity in the air reduces the mobility and on-current [20]. Furthermore, although OTFTs derive benefits from low cost fabrication processes, the defective rate of

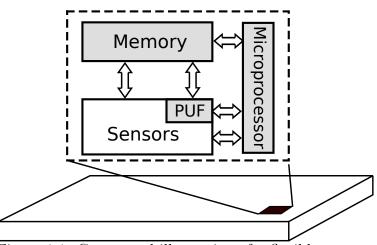

Figure 1.1: Conceptual illustration of a flexible system.

OTFTs is relatively high. Thus, traditional silicon circuit design is not suitable for designing OTFT circuits. For example, the performance of the circuits designed using the conventional CMOS style is considered to be low in the case of OTFTs, due to the performance unbalance between p-type and n-type transistors. The topology used to mitigate the effect of device degradation is required and additional efforts are required to enhance the operation of the OTFT circuits.

In this dissertation, the local treatments of data in organic systems are discussed from three aspects: security, storage, and processing. Additionally, several circuit design typologies are proposed to deal with the above-mentioned challenges in OTFTs. The conceptual illustration of the flexible system considered in this study is shown in Fig. 1.1. First, a hardware security circuit called physically uncloable functions (PUF) used for data security is proposed. OTFT PUF can be implemented in flexible sensors to improve the security of the communication that those devices establish. Moreover, it can also be printed on the packaging of merchandise for authenticating the merchandise. The proposed PUF achieves self-compensation against device degradation for a stable operation. Second, an OTFT memory is proposed for data storage. The OTFT memory can store data generated from the OTFT sensor shown in Fig 1.1 or the security data from PUF. The proposed memory achieves high stability and area efficiency. Based on a traditional memory architecture, a degradation-mitigation circuit is added to extend the retention time of the OTFT memory. Finally, the arithmetic circuits suitable for OTFT implementation are presented. These circuits enable the entire OTFT system to have the ability to compute and control the data. A feasibility of a Turning complete OTFT processor is presented in this dissertation.

### **1.3** Approaches

In this section, details of the aforementioned issues and the methods proposed to counterpart the issues in this dissertation are provided.

#### **1.3.1 OTFT PUF for Data Security**

As applications for OTFTs, such as flexible sensors or smart labels are developed, information leakage from these IoT devices has become a serious problem. In particular, attacks on medical equipment or social infrastructure devices pose a major threat to social systems. The information security and authorization of hardware devices have become crucial. For that reason, PUFs used to enhance hardware security are of high interest [21–24]. Based on physical variations caused during the manufacturing process, PUFs generate random, unclonable, unique identification information for each chip. The traditional silicon PUFs are generally used for authentication of the hardware devices. Through the implementation of OTFTs, the application of PUFs can be broadened, such as smart packaging to the authenticity of products or privacy protection for the information collected by organic sensors.

However, compared with silicon devices that can typically operate stably for more than ten years, degradation of OTFTs is observed on the scale of a few days. The reaction of moisture and organic semiconductor, as well as bias-voltage stress, increase the threshold voltage of the device and decrease the carrier mobility, resulting in a decrease in source-drain current. In PUF circuits, it is difficult to use it for authentication if PUF output change over time due to the degradation of OTFTs. Considering applications such as the authenticity of products for smart packaging, circuit life should be at least several weeks.

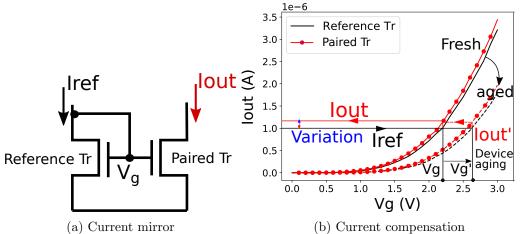

In this dissertation, organic current mirror PUF (OCM-PUF), a PUF structure resistant to the degradation of OTFTs is proposed. In the current mirror, the reference current is copied to obtain the output current. However, due to device variations, there are slight differences in the output current. This difference is used to generate a unique response. The circuit structure of the proposed PUF is simple, hence a stable circuit operation is expected even if the circuit is designed using OTFTs. Despite its simplicity, the proposed PUF achieves self-compensation against device degradation by utilizing the current mirror structure. Moreover, two types of OCM-PUF are proposed. One pursues area efficiency and the other aims for improved robustness. The PUF metrics of the two proposed PUFs are evaluated and compared through measurement.

#### **1.3.2 OTFT SRAM for Data Storage**

In order to implement more advanced functions into flexible IoT systems, local data storage is also indispensable. As the concept of the Turing machine suggests, the essence of computing is the operation on the memory value. Accordingly, for data processing in flexible systems, such as wearable sensors, it is desirable to integrate a flexible memory using the same process as the sensors. Storing the data locally can save transmit power and time [18]. Moreover, the manufacturing cost can be reduced significantly if the fabrication process of the memory is fully compatible with that of the sensors. To guarantee the access speed and stability of data storage, static random access memory (SRAM) is adopted in this dissertation, which can achieve stable operation with fast access time.

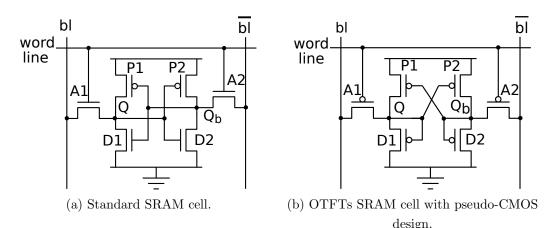

Different from traditional silicon technology, OTFTs are unipolar devices. P-type is much stronger than n-type and OTFTs are sensitive to bias stress degradation. Hence traditional silicon SRAM using CMOS structure is not suitable for the OTFTs. In conventional SRAM construction using OTFTs, a pseudo CMOS design that uses only p-type transistors is adopted. However, compared with the traditional CMOS designs, the circuits based on pseudo-CMOS design occupy a larger area and full swing outputs are hardly possible.

In this dissertation, a CMOS and pseudo-CMOS hybrid organic SRAM with enhanced stability is proposed. A CMOS design is utilized in SRAM cell to achieve high area efficiency and stable operation. The proposed SRAM cell using p-type access transistors realizes sufficient static noise margin (SNM) for stable operation despite the use of weak n-type transistors. Along with the SRAM cell, the specific implementation of the periphery circuit used in the SRAM array is explained. Moreover, a degradation-mitigation circuit using a pseudo-CMOS design is proposed. The pseudo-CMOS design is used for the purpose of stable performance and reliability for a long period. This circuit can self detect degradation and automatically perform a process to mitigate device degradation at required time periods.

#### **1.3.3 OTFT Arithmetic Circuits for Data Processing**

Besides data security and storage, the ability of data processing is indispensable for organic systems. Similar to the OTFTs memory, the near-sensor computing of the system data can also reduce the integration cost. As mentioned above, the OTFTs are unipolar and tend to degrade fast. The current low cost fabrication process leads to a relatively high defective rate. Several design typologies for data processing circuits are discussed to solve these issues of OTFTs [25, 26].

In this dissertation, OTFT circuit design based on pass transistor logic

(PTL) is proposed. PTL is a widely discussed logic family used as an alternative design topology to traditional CMOS [27]. The PTL proposed in this dissertation is designed to reduce the number of required transistors, leading to a high area efficiency. PTL also relies on strong p-type transistors, avoiding the use of n-type as much as possible. The p-type based circuitry guarantees high stability. Two types of PTL circuits are discussed and compared through simulation. A full adder, which is the most widely used logic circuit, is used as an example to confirm the operation of a PTL-based arithmetic circuit.

Furthermore, as an example of a PTL circuit, a PTL-based OTFT processor is studied in this dissertation. The proposed processor is based on one instruction set computer (OISC) architecture and it is Turning complete. OISC structure uses only one instruction to execute any program at the expense of operation time and memory space. The architecture is extremely simple and lightweight since it only has one instruction. The component circuits mainly depend on PTL, which is suitable for OTFTs implementation. To confirm the feasibility of the proposed OISC processor, typical operations in an organic system are performed by the proposed processors.

### **1.4** Organization

The organization of this dissertation is summarized as follows. In Chapter 2, preliminaries of OTFTs are provided. The device structure, specific fabrication process, and device model used for the simulations are presented. The chip fabrication, circuit simulation, and degradation evaluation discussed in this dissertation are based on the preliminaries in this chapter.

In Chapter 3, the implementation of OTFT PUFs for hardware authentication is discussed. To achieve self-compensation of the device performance degradation, OTFT PUFs use the current mirror structure. Then, two types of current mirror PUFs are demonstrated; one aiming for area efficiency and the other pursuing improved robustness. Through test chip measurements, the metrics of two proposed OTFT PUFs are compared and evaluated. The ability to resist device degradation is also confirmed through a long period of measurement.

Chapter 4 proposes OTFT SRAM circuits. Firstly, the architecture of the SRAM array is introduced. A degradation mitigation circuit is added to extend retention time. A new design topology in SRAM cell is proposed to increase the stability and area efficiency. Then, specific circuit structures in the SRAM array are designed. The transistor sizes of the SRAM cell are optimized through simulation. Finally, the operations of the SRAM cell, periphery circuits, and SRAM array are confirmed through test chip measurements. Additionally, the

effectiveness of the degradation mitigation circuit is verified.

Chapter 5 discusses the data processing in the OTFT system. For the logic circuit, a design topology using PTL is proposed. A full adder using PTL is used as an example. Through simulation and measurements, this design topology is proven to be suitable for logic circuit implementation using OTFTs. Based on the PTL, Chapter 5 also demonstrates an OTFT processor. The proposed processor using OISC simplifies architecture and the construction is lightweight. The OISC processor intensively uses the pass transistors and mainly depends on the proposed PTL adder. A feasibility of the proposed processor is again confirmed through simulation and measurements.

In Chapter 6, a summary of this dissertation and future works are discussed.

### 1.4. ORGANIZATION

## Chapter 2

## Preliminaries of Organic thin film transistors

The OTFTs are a type of thin-film transistors (TFTs) in which the semiconductor is made of organic materials. Similar to silicon transistors, OTFTs have three terminals, gate, source, and drain and they operate as switches in logic circuits. While their fabrication processes are much less complex than conventional silicon technology. OTFTs can be fabricated in low temperature and low cost deposition or printing processes. In addition, the mechanical flexibility of organic materials enables OTFTs compatible with flexible substrates. In this chapter, detailed background knowledge about OTFTs used in this dissertation is provided. The device structure and fabrication process are introduced in Section 2.1 and Section 2.2. Section 2.3 provides the device model for OTFTs used for SPICE simulation. The OTFTs characteristic, especially device degradation, is explained in Section 2.4

### 2.1 OTFTs structure

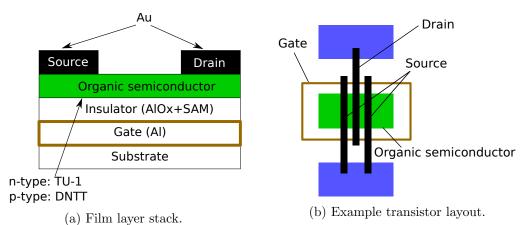

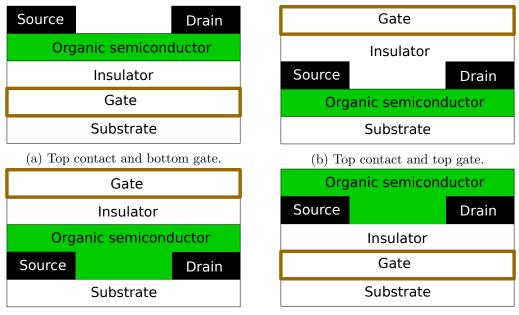

The OTFTs considered in this dissertation exhibit a top contact and bottom gate structure with a minimum feature size of  $50 \,\mu$ m. A simplified crosssectional structure showing a film layer stack is illustrated in Fig. 2.1(a). Depending on the relative position (top/bottom) of contact, gate electrodes, and organic semiconductor, there are four types of device structures which are shown in Fig. 2.2. The structure in which the gate electrode is located below the semiconductor layer is called the "bottom gate" type and the structure in which the gate electrode is placed above the semiconductor layer is called the "top gate." Similarly, by the position of contact and semiconductor, there are "top contact" and "bottom contact" structures.

Figure 2.1: Structure of low voltage organic thin-film transistor. © IEEE 2020

In the bottom contact structure, the contact electrode is fabricated first, and then the organic semiconductor is fabricated on the contact electrode. It is hard for the organic semiconductor to form a uniform surface between the contact layer and the organic semiconductor layer. Hence, the bottom contact structure shows higher contact resistance than the top contact structure [28,29]. Regarding the gate position, in the bottom gate structure, the gate insulator layer is formed before the organic semiconductor. Metal oxides with high dielectric constant, such as aluminum oxide that can be formed by treatment such as oxygen plasma, can be used for forming an insulator film [30–32]. Moreover, by adding additional surface treatments on insulator film such as self-assembled monolayer (SAM) [29], the characteristics and stability of OTFTs can be further improved.

The stacking of film layers, from the bottom to top, for fabricating an OTFT is as follows: gate metal (Al), insulator  $(AlO_x)$  and selfassembled monolayer (SAM), organic semiconductor, source-drain metal (Au), and passivation on a substrate material. The semiconductor materials are dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) [33, 34] for p-type and 4,8-Bis[5-[3-(trifluoromethoxy)phenyl]-2-thienyl]- $2\lambda^4\delta^2$ -benzo[1, 2c:4,5-c']bis[1,2,5]thiadiazole (TU-1) [35] for n-type.

The OTFTs with the multifinger layout shown in Fig. 2.1(b) are used in this work. Since the feature size of OTFTs is relatively large, the transistor area should be as small as possible. Compared with the one finger layout, the transistor area and diffusion capacitance are reduced while maintaining the dimensions (channel width/ channel length) of the transistor [27,36]. Moreover, the channel width can be easily increased by adding the drain and source electrodes.

CHAPTER 2. PRELIMINARIES OF ORGANIC THIN FILM TRANSISTORS

(a) Bottom contact and top gate.(b) Bottom contact and bottom gate.Figure 2.2: Structures of low voltage organic thin-film transistors.

### 2.2 Fabrication process of OTFTs

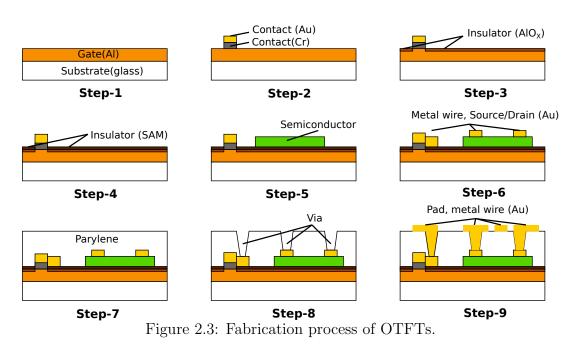

The fabrication process of the OTFTs used in this dissertation is introduced below, and a cross-sectional view of a device in each step is shown in Fig. 2.3. Although a printing process can be used for OTFTs fabrication, to maximize the performance of OTFTs circuits, more stable processes mainly depending on physical vapor deposition (PVD) are currently used. It takes about three days to complete the process.

Step-1 Gate electrode (Al) deposition

In a vacuum of about  $5 \times 10^{-4}$  Pa, Tungsten is used for the support of solid Al, and solid Al is heated and deposited by applying a 25 A current to Tungsten. After the deposition is finished, the Al is cooled in a vacuum for 30 minutes. The thickness of the deposited Al film is about 20 nm.

Step-2 Contact layer (Cr and Au) deposition

Since the gate electrode is at the bottom of the OTFTs, a contact layer is needed to connect the gate with the upper layer. Cr is used to improve the contact between Al and Au. In a vacuum of about  $5 \times 10^{-4}$  Pa, Cr and Au are deposited in that order with a current of 7 A. The thickness of the contact layer is about 40 nm.

#### **Step-3** $O_2$ plasma oxidation of Al

Oxidation treatment with oxygen plasma for 30 minutes while supplying 0.2 L/min of oxygen. The gate electrode (Al) other than Via is oxidized to form  $\text{AlO}_x$ , which will be the insulator of the OTFTs.

#### Step-4 Self-assembled monolayer (SAM) generation

SAM is used to modify the dielectric interfaces to improve the characteristics of OTFTs. It can be produced by immersing the substrate in a solution of 33.4 mg Octadecylphosphonic acid (ODPA) [37] dissolved in 20 ml propanol for 2 hours. SAM is formed only on  $AlO_x$  by neutralization reaction. After SAM generation, the substrate is washed with propanol to remove excess ODPA and then heated to 120 °C to evaporate the moisture produced by the neutralization reaction during the SAM generation. The  $AlO_x$  and SAM operate as the insulator of OTFTs which is extremely thin, about 5 nm in total.

Step-5 Organic semiconductor deposition.

In a vacuum of about  $1 \times 10^{-3}$  Pa, semiconductor materials contained in the test cube are gradually heated and deposited. The deposition rate of semiconductors is important because it involves the formation of crystals, and is performed at a rate of about 0.3 Å/s. The deposition is terminated when the film reaches 30 nm thickness and then cooled in a vacuum for 30 minutes.

Step-6 Source/Drain, metal wire (Au) deposition

In a vacuum of about  $5 \times 10^{-4}$  Pa, Au is deposited with a current of 7 A. The thickness of all Au layers is about 30 nm.

Step-7 Parylene protective film formation

The parylene film is used to protect the OTFTs from environment-induced degradation. It is formed by the chemical vapor deposition (CVD) process. First, the furnace is heated to  $690 \,^{\circ}$ C and evacuated to 7 Pa. Then, 1 g parylene is set and heated to  $175 \,^{\circ}$ C to vaporize. Parylene in gaseous form at  $175 \,^{\circ}$ C is decomposed in the furnace at  $690 \,^{\circ}$ C and polymerized to form a film on an OTFT chip. Since the Parylene layer is used to protect OTFTs, it is relatively thick at about  $600 \,\mathrm{nm}$ .

Step-8 Hole opening for via

Holes are drilled on the parylene to connect the metal wire to the upper layer. The holes are generated by oxygen plasma for 30 minutes while supplying 0.2 L/min of oxygen.

#### CHAPTER 2. PRELIMINARIES OF ORGANIC THIN FILM TRANSISTORS

#### Step-9 Pad metal (Au) deposition

The pad metal is the top layer of the device. Probes contact the pad for measurement. In addition, for complex OTFT circuits, only one layer of metal wire is generally insufficient. The pad metal is also used for wiring purpose.

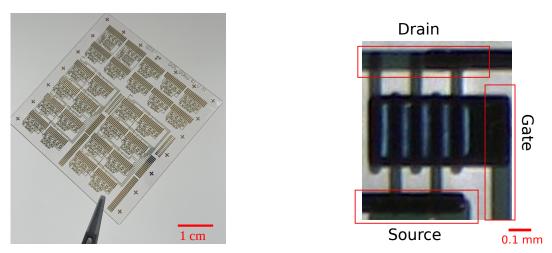

The OTFT chips in this dissertation are fabricated on a  $5 \text{ cm} \times 5 \text{ cm}$  glass substrate. By replacing the glass substrate with a plastic film, the OTFT circuits can also be fabricated on flexible film substrates. A photo of an entire chip and one OTFT is shown in Fig. 2.4. Thanks to an extremely thin insulator layer, which is about several nm, the OTFTs can be driven by a low supply voltage. However, it is inevitable that the thin insulator tends to have a problem of gate dielectric breakdown, decreasing the chip yield. To mitigate this problem, the use of the gate electrode layer is minimized and this layer is used only for the OTFTs gate, i.e., this layer is not used for wiring purpose. Most of the metal wires in circuits use the Au layer deposited in Step-6 and Step-9. The parylene layer with several hundred nm thickness has better insulation properties.

(a) Chip entire. (b) Single OTFTs device. Figure 2.4: Photo of a fabricated OTFTs chip. Substrate is a  $5 \text{ cm} \times 5 \text{ cm}$  glass. A flexible film substrate can also be used.

## 2.3 Operation principle and device model of OTFTs

The OTFTs have a metal-insulator-semiconductor (MIS) structure and the operation principle is similar to Si MOSFET. For example, in n-type transistors, when the gate-to-source voltage  $(V_{\rm gs})$  is larger than the threshold voltage  $(V_{\rm th})$ , the transistor turns ON and a channel is formed at the interface of the organic semiconductor and insulator. By applying a positive drain-to-source voltage  $(V_{\rm ds})$ , carriers are injected from the drain and current begins to flow through the channel. When increasing  $V_{\rm ds}$  to  $V_{\rm gs} - V_{\rm th}$ , the potential between the gate and the source is eliminated, the channel disappears and becomes pinched off. Above this voltage, the current is saturated and only controlled by  $V_{\rm gs}$  regardless of  $V_{\rm ds}$ . A simple Shockley model shown in Eq. 2.1 can express this operation [38] as,

$$I_{\text{SAT}} = \frac{\mu W C_i}{2L} (V_{\text{gs}} - V_{\text{th}})^2$$

$$I_{\alpha} = \begin{cases} I_{\text{SAT}} & (V_{\text{ds}} > V_{\text{SAT}}) \\ I_{\text{SAT}} \begin{pmatrix} 2 - \frac{V_{\text{ds}}}{V_{\text{SAT}}} \end{pmatrix} \frac{V_{\text{ds}}}{V_{\text{SAT}}} & (V_{\text{ds}} \le V_{\text{SAT}}) \end{cases}$$

$$(2.1)$$

where, the  $I_{\text{SAT}}$  and  $V_{\text{SAT}}$  are the pinch off current and voltage. On the other hand, Si MOSFETs and OTFTs use different electrodes, leading to differences

| Parameter                                                                    | Explanation                   |

|------------------------------------------------------------------------------|-------------------------------|

| $V_{ m SAT}, I_{ m SAT}$                                                     | Pinched off voltage, current  |

| W, L,                                                                        | Channel width, Channel length |

| $\overline{C_{\mathrm{I}}}$                                                  | Gate dielectric capacitance   |

| $B, V_{\rm B}, K_{\alpha}, m_{\alpha}, n_{\alpha}, \lambda_{\alpha}, I_0, S$ | Fitting parameters            |

Table 2.1: Explanation of each parameter in OTFTs device model

in operation in the transistor OFF state. In Si MOSFETs, the leakage current is very small because a reverse electric field is applied to the pn junction between the drain and the source. In OTFTs, there are carriers with potentials exceeding the injection barrier of source metal to organic semiconductor. These carriers can inject into the organic semiconductor, resulting in a relatively large leakage current.

For accurate SPICE simulation, a high accuracy model is required. As described above, the operation of OTFTs can be explained by a similar principle as that of Si MOSFETs. A device model on the basis of Si MOSFET models has been proposed to describe the characteristics of OTFTs [39]. In this model, the on-current  $(I_{\alpha})$  model shown in Eq. 2.3 is represented by the alpha-power law [40], which is more accurate than the Shockley model. The current in the subthreshold region  $(I_{sub})$ , shown in Eq. 2.6, is expressed by the exponential function of  $V_{gs}$ .  $I_{sub}$  is caused by the diffusion current due to the charge density gradient between the source and the drain.  $I_{\alpha}$  and  $I_{sub}$  are smoothly connected by the tanh function. The gate leakage current is expressed by  $I_{leak}$ . The explanation of each model parameter is shown in Table 2.1.

$$I_{\rm D} = I_{\alpha} \frac{1}{2} \left[ 1 + \tanh \left[ B \left\{ V_{\rm gs} - (V_{\rm th}(t) - V_{\rm B}) \right\} \right] \right] + I_{\rm sub} \frac{1}{2} \left[ 1 - \tanh \left[ B \left\{ V_{\rm gs} - (V_{\rm th}(t) - V_{\rm B}) \right\} \right] \right] + I_{\rm leak}$$

(2.2)

$$I_{\alpha} = \begin{cases} I_{\text{SAT}} & (V_{\text{ds}} > V_{\text{SAT}}) \\ I_{\text{SAT}} \left( 2 - \frac{V_{\text{ds}}}{V_{\text{SAT}}} \right) \frac{V_{\text{ds}}}{V_{\text{SAT}}} & (V_{\text{ds}} \le V_{\text{SAT}}) \end{cases}$$

(2.3)

$$V_{\rm SAT} = K_{\alpha} \left( V_{\rm gs} - V_{\rm th}(t) \right)^{m_{\alpha}} \tag{2.4}$$

$$I_{\rm SAT} = \frac{W}{L} C_{\rm I} \mu \left( V_{\rm gs} - V_{\rm th}(t) \right)^{n_{\alpha}} \left( 1 + \lambda_{\alpha} V_{\rm ds} \right)$$

(2.5)

$$I_{\rm sub} = I_0 \exp\left\{-\frac{\ln(10)}{S} \left(V_{\rm gs} - V_{\rm th}(t)\right)\right\}$$

(2.6)

### 2.4 Electronic characteristic of OTFTs

Generally, the OTFTs are almost unipolar that p-type is much stronger than n-type. Unlike Si MOSFETs using pnp or npn structure to form a channel, the OTFTs use n/p-type semiconductor materials. The carriers are produced by the energy level between the organic semiconductor and the source/drain. The highest occupied molecular orbital (HOMO) is used for p-type organic semiconductor and the lowest occupied molecular orbital (LOMO) is used for n-type organic semiconductor. The metals typically used for the source/drain, such as Au or Ag, have high work functions better suited for injection of holes into the HOMO than of electrons into the LUMO. Low-work-function metals such as Al or Mg, oxidize easily and readily form reactive complexes with the organic semiconductor, resulting in the degradation of both metal and organic semiconductor [38].

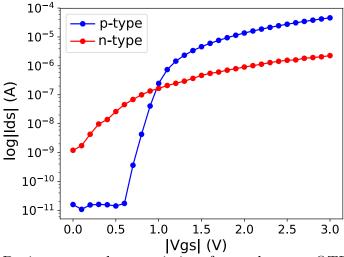

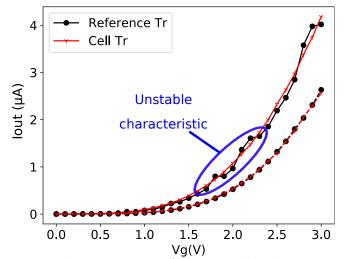

An example of the measured  $I_{\rm d} - V_{\rm g}$  characteristics of the p-type and ntype OTFTs used in this thesis is shown in Fig. 2.5. These devices can be driven by a supply voltage of 3 V or lower [41]. The p-type transistors exhibit better performance than the n-type with more than 10x higher on-current and a significantly better on-off current ratio.

When compared to Si devices, OTFTs are relatively easier to degrade the performance due to bias-stress voltages and reactions with air humidity or oxygen [42–44]. Moisture diffuses into the organic semiconductor, capturing the carriers generated in the channel. This reduces the on-current and mobility. In addition, oxygen molecules oxidize the semiconductor, degrading the characteristic of OTFTs. The degradation affects the threshold voltage and mobility. The degradation model is expressed as shown in Eq. 2.7 [44]:

$$p(t) = \mathbf{P0} + \mathbf{A}_{\mathbf{P}} \left( t - \mathbf{t}_{\mathbf{0}} \right)^{\mathbf{n}_{\mathbf{P}}}, \qquad (2.7)$$

where p denotes a model parameter that represents degradation, either threshold voltage ( $V_{\rm th}$ ) or mobility ( $\mu$ ). **P0** denotes the initial value,  $\mathbf{A_P}$  and  $\mathbf{n_P}$  denote degradation rate. Once degraded, it is difficult to fully recover to the original characteristic. In recent years, numerous efforts have been made to enhance the stability of OTFTs [9,10,45]. The environment-induced degradation can be suppressed via protection methods such as the application of an encapsulant on the top of the circuit. With the advancement of device materials and structures, the recent OTFTs can reportedly operate for approximately one year [46].

The bias-stress degradation is also a serious issue for low voltage OTFTs, under the conditions where devices are in static bias conditions. The degradation mechanism is considered as the trap of mobile charge carriers in the semiconductor channel formed on the gate dielectric. The trapped carriers lead to increased threshold voltage and decreased mobility, thereby, degrading

Table 2.2: Parameters of the degradation model of OTFTs in Eq. 2.8, Eq. 2.9, and Eq. 2.10

| Parameter       | Explanation                               |

|-----------------|-------------------------------------------|

| p               | Model parameter for $V_{\rm th}$ or $\mu$ |

| $\delta_1$      | Degradation term                          |

| $\delta_2$      | Recovery term                             |

| $-A_{\rm p}, m$ | Degradation rate                          |

| $-B_{\rm p}, n$ | Recovery rate                             |

Figure 2.5: Drain current characteristics of p- and n-type OTFTs with a size of W/L=1200  $\mu$ m/50  $\mu$ m.  $V_{ds}$ =3.0 V. © IEEE 2022

the performance of the device [47]. The performance of the OTFTs is reported to recover when stress voltage is removed. The degradation and recovery model for the bias stress is represented as follows [20], and the explanation of each model parameter is shown in Table 2.2.

$$\Delta p(t+t_0) = \delta_1 + \delta_2, \tag{2.8}$$

$$\delta_1 = \phi_p \left( 1 - \exp\left( -A_p t^m \right) \right), \tag{2.9}$$

$$\delta_2 = \Delta p(t_0) \left( 1 - \left( \frac{1 - \exp\left[ -B_{\rm p} t \right]}{1 - \exp\left[ -B_{\rm p} \left( t + t_0 \right) \right]} \right)^n \right), \tag{2.10}$$

# Chapter 3

# Physical Unclonable Function using OTFTs

# **3.1** Introduction

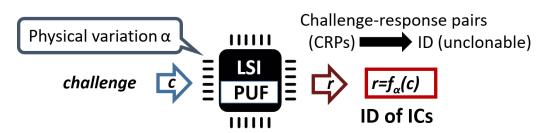

With the advancement of IoT society, various IoT devices can now be connected to the internet. Securing data generated by IoT devices has become crucial. Among the vast areas of information security, authorization of hardware devices is one of the most important topics. For that reason, physically unclonable functions (PUFs) are attracting attention in the field of hardware security [21– 24]. On the basis of physical variation during the manufacturing process, PUF generates identification information, which is random, unclonable, and unique to each chip. The challenge-response (input and output) of the PUFs can be used for authentication, encryption, etc [48–50].

Physically unclonable function circuits using OTFTs [1,2] are the prospective candidates for use with IoT sensors. Moreover, OTFT PUFs can be implemented in RFID tags or with flexible sensors to improve the security of the communications that those devices establish. Besides hardware devices, OTFT-based PUFs can also be used for the packaging of merchandise. By printing on the surface of packaging materials, OTFT PUFs can be used for various purposes, such as delivery tracking or expiration date control.

In this chapter, we propose a new PUF circuit, organic current mirror PUF (OCM-PUF), which is suitable for fabricating using OTFTs. In recent years, numerous efforts have been made to enhance OTFT stability and considerable progress has been achieved [9–11]. However, the deterioration of organic devices leading to the degradation of circuit performance is still a serious issue in OTFTs [39, 46, 51]. Considering the performance and the stability of OTFTs available today, we take the simplest approach to construct the organic PUF.

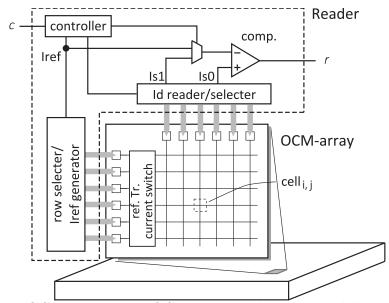

Figure 3.1: OCM-array as an OCM-PUF, and its use model. © IEEE 2020

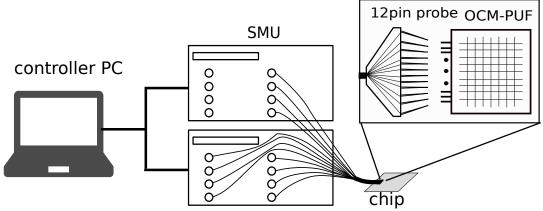

The conceptual illustration and the usage model of the proposed OCM-PUF are shown in Fig. 3.1. In this example, the PUF is printed as an organic current mirror array (OCM-array) on the surface of merchandise, such as a smartphone or grocery packaging. The printed array serves as a serial number and/or expiry date associated with it [52]. When in use, a reader device first accepts challenge c to apply for the OCM-array. The OCM-array outputs the corresponding response r. The challenge and response pairs are then compared with those taken at the time of packaging and stored in the database. We fabricate the proposed PUF to experimentally evaluate its performance [53].

Compared with the existing PUFs that use OTFTs such as SRAM PUF [54] or Arbiter PUF [55] the circuit structure of the proposed PUF is simpler. Therefore, a stable circuit operation is expected even if the circuit is fabricated using OTFTs. The response of the proposed OCM-PUF is determined by the current variation of each device. Moreover, the salient feature of the proposed PUF is its resilience against device degradation. As described in Chapter 2, device degradation is an unavoidable problem of OTFTs. In PUF circuits, since the short actual operating time, the degradation over time is dominant rather than bias-stress degradation. The proposed PUF achieves self-compensation against device degradation by utilizing the current mirror structure.

In this chapter, two types of OCM-PUFs are proposed and thoroughly evaluated: one that aims for area efficiency [56] and one that pursues improved robustness in the systematic variation. Through the test-chip fabrication and measurements, the advantages and disadvantages of the two proposed PUFs were compared, and the PUF metrics of the proposed OCM-PUFs were quantitatively evaluated.

The rest of this chapter is organized as follows. In Sec. 3.2, preliminaries of PUFs, and organic PUFs are introduced. Then, in Sec. 3.3, the circuit structure and its operation of the proposed OCM-PUF are presented. The proposed circuit is evaluated through test chip measurements as presented in Sec. 3.4. Finally, we conclude this chapter in Sec. 3.6.

# 3.2 Background

#### 3.2.1 Physically unclonable function

The PUFs exploit the manufacturing process variation to generate unique information for each instance. The PUFs are expected to be widely used in the authentication and key generation for common key cryptosystems [57]. It can be embodied in physical structure and is easy to evaluate, however, difficult to predict and duplicate.

The general operation of the PUF is pictorially illustrated in Fig. 3.2. A PUF works as a function f that returns a response r = f(c) for a challenge input c. Here, the function f of a PUF is non-deterministic and chip-dependent because it depends on the physical variation of the hardware circuit. This property is achieved by simply using the same usual layout and fabrication. However, each PUF acquires its own unique challenge-response pairs (CRPs) because they are determined by physical variations that are beyond the control of manufacturing equipment. Because manufacturing variation is the source of the random response, cloning the function f is impossible even by the manufacturer of the PUF. In other words, the PUF circuit is designed, so that the chip-dependent manufacturing variability is enlarged and becomes observable. At present, authentication and secure key generation are the two primary applications of PUFs. Two categories of PUFs exist: strong PUF and weak PUF [58]. The strong PUFs own an exponentially large number of CRPs and are typically used for authentication. The weak PUFs have a limited number of CRPs and are typically used for key generation.

In conventional common-key cryptosystems, keys are stored in non-volatile memory within a chip. However, safely managing keys in memory is difficult and expensive. The invasive attack can extract the digital key stored in the memory. In order to achieve a higher level of security, additional tamper-sensing circuitry has been required to protect memory [57], which may become costly. By using PUFs, secret keys can be derived from the physical characteristics of the circuit at a lower cost than storing keys in memory [59].

In addition, PUFs can be used in the authentication process. As shown in Fig. 3.3, we may consider the authentication between Alice and Bob. In the PUF-based authentication, a large number of CRPs were collected and stored in a secure database and then the PUF was securely passed to Bob before communication. After this setup, Alice chose a CRP(c,r) from the CRP database and sent the challenge to Bob. When Bob received the challenge, a response  $r_{\alpha}$  obtained from the PUF was returned to Alice. Bob will verify the response r by whether it matches  $r_{\alpha}$  or not.

The performance of PUF can be evaluated using randomness and reliability metrics [60]. The randomness represents the balance of 0's and 1's in the response. It can be defined as follows:

Randomness =

$$-\log_2\left(\frac{1}{2} + \left|\frac{1}{C}\sum_{c=1}^C r_c - \frac{1}{2}\right|\right),$$

(3.1)

where  $r_c$  and C are the responses to challenge c and the maximum number of challenge c, respectively. The reliability is a metric that indicates whether a PUF always returns the same response to the same challenge. The reliability can be estimated by calculating the ratio of the response change as follows:

$$Reliability = \frac{Changed bits}{Total bits}.$$

(3.2)

The reliability metric can be used for the evaluation of the effectiveness of the aging compensation. Both metrics assume a value between 0 and 1, where 0 is the worst, and 1 is the best.

A changing response is considered an error response. Decreasing the error rate is critical in designing PUFs using organic devices. The responses of a PUF can change with the change in environmental conditions. Typically, the error, observed as a bit-flip, can be corrected by an error-correction code (ECC) [57]. However, a PUF with a very high error rate will result in an impractically large ECC. In the worst-case scenario of observing considerable randomly occurring errors, the generation of ECC becomes infeasible. It has been reported in [61] that an error rate higher than 25% can make using ECC entirely impractical.

#### 3.2.2 Organic thin-film transistor PUF

Thus far, several PUFs using OTFT devices have been proposed. These techniques have successfully realized the functionality of PUFs. However, there remains room for improvement before their practical application, particularly in terms of the stability of the responses.

Figure 3.2: Typical use of PUFs. (c) IEEE 2020

Figure 3.3: Example PUF-based authentication. © IEEE 2020

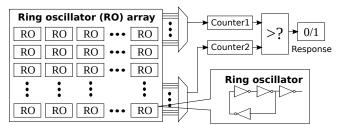

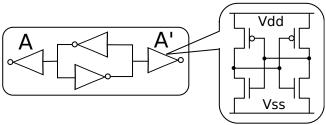

The ring oscillator (RO) PUF [1] shown in Fig. 3.4 utilizes the frequencies of ROs. The frequencies of two selected ROs have been compared to generate a response. Due to the variation in transistors, each RO has different frequency. Hence, the response is unique. Fig. 3.5 shows the construction of the buskeeper PUF [2] which uses a pair of cross-coupled inverters to generate a response. After applying supply voltage, the value of cross-coupled invert is random mainly depending on the threshold voltage of internal transistors. The Buskeeper PUF in [2] is reported to be more tolerant to environmental changes than RO PUFs. However, the responses of the PUF are easily affected by the temporal degradation of the OTFT, decreasing the reliability of the PUF.

In these PUF implementations, several transistors have been used to generate a response bit. In the case of the buskeeper PUF, without considering the access transistors, four OTFTs are used to construct one cell. A RO PUF requires an even larger number of transistors than the buskeeper PUF. As the area of the PUF becomes larger, there will be a greater chance of observing device failure. The large area may also lead to non-uniformity of the device performance. Since the size of the OTFT devices is much larger than that of silicon devices, it would be desirable to shrink the circuit area to as small as possible. For assumed applications of organic PUF, such as smart packaging or authentication of organic IoT sensors, the desirable circuit area would be

Figure 3.4: Construction of ring oscillator PUF [1]

Figure 3.5: Cell of Buskeeper-PUF [2]

less than a few square centimeters. Moreover, higher cell density increases the available number of PUF bits for a given area. This leads to a higher security level [53]. In our organic PUF design, area efficiency and stable performance against aging are the two main objectives.

# **3.3** Organic current mirror array

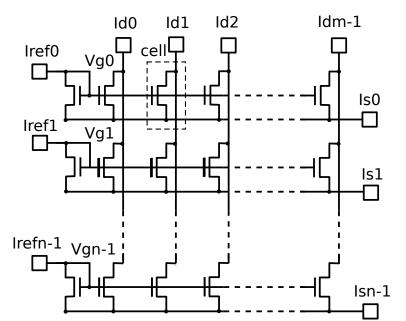

#### 3.3.1 Circuit architecture

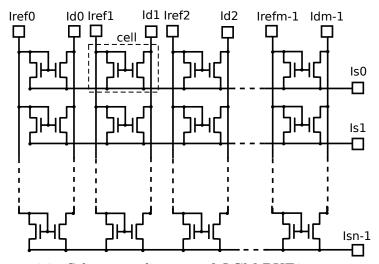

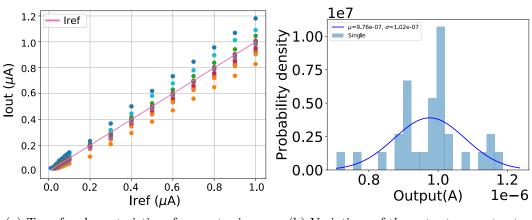

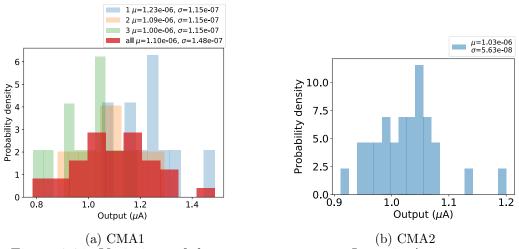

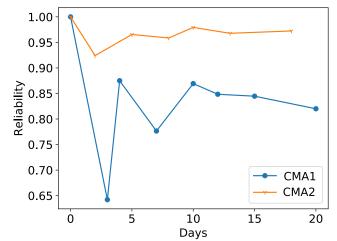

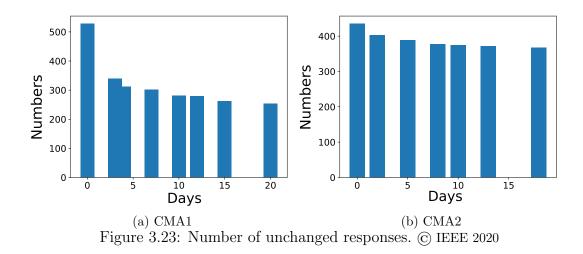

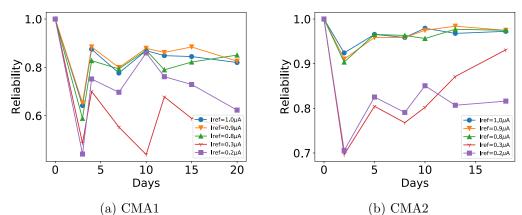

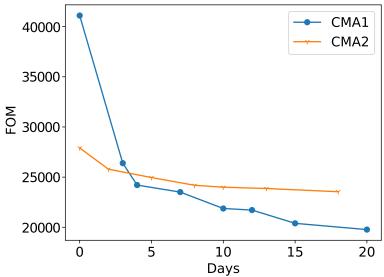

Here, we propose two designs of current mirror arrays (CMAs): CMA1 and CMA2. The CMA is the integral component of the OCM-PUF.