# 時分割多元接続システムにおける 同期制御方式の研究

平成3年5月

守倉正博

# 目次

| 第 | 1  | 章          | 緒言 | *** | *******           | ********* | **********   |           |                                          |                 | *************************************** | . 1   |

|---|----|------------|----|-----|-------------------|-----------|--------------|-----------|------------------------------------------|-----------------|-----------------------------------------|-------|

|   |    |            |    |     |                   |           |              |           |                                          |                 |                                         |       |

|   | 1. | 1          |    | 研究  | の背景               | <u>t</u>  |              |           |                                          |                 |                                         | . 1   |

|   | 1. | 2          |    | 研究  | 課題σ               | 所在        |              |           |                                          |                 |                                         | 2     |

|   |    | 1.2.1      |    | 単一  | 中継器               | 達用 T      | DMA方         | 式         |                                          | ************    | •••••••••                               | 4     |

|   |    | 1.2.2      |    | 複数  | 中継器               | 運用「       | DMA方         | 式 …       |                                          |                 |                                         | 6     |

|   |    | 1.2.3      |    | S S | - T C             | МАЯ       |              |           |                                          |                 |                                         | 7     |

|   |    | 1.2.4      |    | 衛星  | 上再生               | 中継工       | DMA方         | 式 …       |                                          |                 |                                         | 8     |

|   | 1. | 3          |    | 論文  | の概要               | Ę         |              |           |                                          |                 |                                         | 9     |

|   |    |            |    |     |                   |           |              |           |                                          |                 |                                         |       |

|   |    |            |    |     |                   |           |              |           |                                          |                 |                                         |       |

| 第 | 2  | 章          | 同期 | 制御  | *****             |           |              |           |                                          |                 | ******************                      | 10    |

|   |    |            |    |     |                   |           |              |           |                                          |                 |                                         |       |

|   | 2. | 1          |    | まえ  | がき                | ******    |              |           |                                          |                 |                                         | 10    |

|   | 2. | 2          |    | 送受  | 信同期               | 制御法       | <u> </u>     | ********* |                                          |                 | TNAKARA KASTILAT TARAKKAN               | 10    |

|   |    | 2.2.1      |    | 受信  | 同期                |           |              |           |                                          |                 |                                         | ·· 10 |

|   |    | 2.2.2      |    | 初期  | 捕捉                | *******   | *********    | ******    |                                          | ********        | ****************                        | - 14  |

|   |    | 2.2.2.1    |    | 初期  | 捕捉法               | ******    |              |           |                                          |                 |                                         | . 14  |

|   |    | 2. 2. 2. 2 |    | 初期  | 捕捉用               | ウィン       | ノドウ幅         |           |                                          |                 |                                         | . 15  |

|   |    | 2.2.3      |    | 送信  | 同期                | ********  | *******      | ******    | ** * * * * * * * * * * * * * * * * * * * |                 |                                         | . 19  |

|   | 2. | 3          |    | 同期  | 制御信               | 号伝送       | き特性の改        | 善法        |                                          |                 |                                         | . 23  |

|   |    | 2.3.1      |    | 直列  | 転送方               | 正と注       | <b></b>      | 左         | *** - * * * * * * * * * * * * * * * * *  | *********       |                                         | . 23  |

|   |    | 2.3.2      |    | バー  | スト誤               | しりパタ      | アーンの理        | 論的検       | 請                                        | **********      | **********                              | . 24  |

|   |    | 2.3.3      |    | ブロ  | ック無               | (効確等      | <b>三とブロッ</b> | ク誤り       | 確率 …                                     | *************** |                                         | - 26  |

|   |    | 2.3.4      |    | 実験  |                   |           |              |           |                                          |                 |                                         | . 27  |

|   | 2. | 4          |    | むす  | ٠. ت <del>ن</del> | ********* |              |           |                                          |                 |                                         | 30    |

| 第  | 3 章     | 同期語 … |                   | 31 |

|----|---------|-------|-------------------|----|

|    | . 1     | 生 そん  | き                 | 21 |

|    | i. 2    |       | 検出器の構成と特性         |    |

|    | 3. 2. 1 |       | 検出器の構成            |    |

|    | 3. 2. 2 | 不検出   | • 誤検出特性           | 36 |

|    | 3. 2. 3 | 同期語   | 長                 | 40 |

|    | 3. 2. 4 | 同期語   | パターン              | 43 |

| 3  | 1. 3    | 同期語   | 検出特性の改善法          | 46 |

|    | 3. 3. 1 | 符号化   | UW検出法             | 46 |

|    | 3. 3. 2 |       | 復号後の符号誤りパターン      |    |

|    | 3. 3. 3 | 符号化   | U W 検 出 特 性       |    |

| 3  | 3. 4    | むすび   |                   | 54 |

|    |         |       |                   |    |

| 第一 | 4 章     | 複数中継器 | 運用時の同期制御          | 55 |

| 4  | . 1     | まえか   | き ·····           | 55 |

| 4  | . 2     | 複数中   | 継器運用・時分割多元接続装置の構成 | 55 |

|    | 4. 2. 1 | TDM   | A 同期制御法 ······    | 58 |

|    | 4. 2. 2 | ガード   | タイム               | 59 |

| 4  | . 3     | 記憶型   | バースト復調器AFC回路      | 60 |

|    | 4. 3. 1 | 回路構   | 成と記憶型動作           | 61 |

|    | 4.3.2   | 制御部   |                   |    |

|    | 4. 3. 3 | 実験    |                   | 65 |

| 4  | . 4     | むすび   |                   | 71 |

| 第 | 5        | 章          | 衛星 | Ŀ  | マ            | ス:         | 9 :             | ל     |    | צי      | ク    | 周     | 波 | 数           | 制   | 御       |         | ****    | • • • • • | ••••    |     |        |       |             | ••••   | <br>******   | 72  |

|---|----------|------------|----|----|--------------|------------|-----------------|-------|----|---------|------|-------|---|-------------|-----|---------|---------|---------|-----------|---------|-----|--------|-------|-------------|--------|--------------|-----|

|   |          | ş.         |    | +  | =            | .,         | <del>-</del> tc |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              | 70  |

|   | i.       |            |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              |     |

| į | <b>.</b> | 2          |    | マ  | ス            | タ・         | クロ              | _     | ツ  | ク       | 制    | 御     | 方 | 式           |     | 7/7/7/7 |         | ****    |           | ••••    |     |        | ***** |             |        | <br>         | 74  |

|   |          | 5. 2. 1    |    | マ  | ス            | タ・         | クロ              | ם     | ッ  | ク       | 位    | 相     | 誤 | 差           | 測   | 定       |         | • • • • |           | ••••    |     |        |       |             |        | <br>         | 75  |

|   |          | 5. 2. 2    |    | マ  | ス            | タ・         | クロ              | 3     | ッ  | ク       | 周    | 波     | 数 | 制           | 御   | ル       | -       | プ       | *         | ****    |     |        | ***** | • • • • • • |        | <br>         | 78  |

|   |          | 5. 2. 3    |    | マ  | ス            | タ          | クロ              | _     | ッ  | ク       | 制    | 御     | 誤 | 差           |     |         |         |         |           |         |     |        |       | • • • • • • |        | <br>         | 80  |

|   |          | 5. 2. 4    |    | 最  | 適            | 制行         | 卸「              | 間     | 嗝  |         |      | •••   |   |             |     | •••     |         | •••     |           | • • • • |     |        |       |             | •••••  | <br>         | 87  |

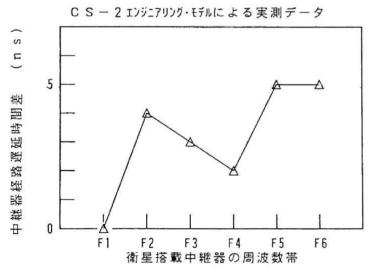

| Ę | i.       | 3          |    | 実  | 験            | 結!         | 果               | 9     |    |         | •••• |       |   |             |     |         | • • • • | ••••    | • • • • • | • • • • |     |        |       |             |        | <br>         | 89  |

| Ę | j.       | 4          |    | ŧ  | <del>d</del> | び          |                 | • • • |    |         | •••• | * * * |   |             |     |         |         |         |           |         |     |        |       |             | ****** | <br>         | 93  |

|   |          |            |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              |     |

|   |          |            |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              |     |

| 第 | 6        | 章          | 時分 | 割  | 多            | 元拍         | 妾≉              | 売     | 装  | 置       | の    | 小     | 型 |             | 高   | 信       | 頼       | 化       |           |         |     |        | ••••• | •••••       |        | <br>         | 94  |

|   |          |            |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              |     |

| 6 | i.       | 1          |    | ま  | え            | かく         | ė               | 9     |    | · • • • | •••• |       |   |             |     |         | ••••    | ••••    |           |         |     |        |       |             |        | <br>         | 94  |

| 6 | i.       | 2          |    | Τ. | D            | М.         | Αij             | 麦     | 置  | の       | 構    | 成     |   | ***         |     |         |         | ****    |           | • • • • |     |        | ••••  |             |        | <br>         | 94  |

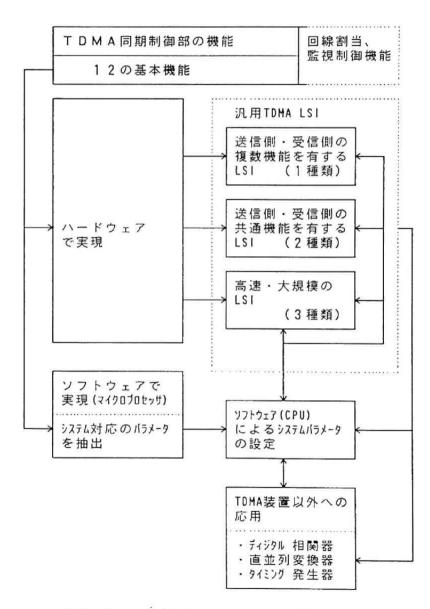

|   |          | 6. 2. 1    |    | Т  | D            | м.         | Αſ              | 司     | 期  | 制       | 御    | 部     | に | お           | け   | る・      | 信       | 号       | 処理        | 里枝      | 既要  |        |       |             |        | <br>         | 96  |

|   |          | 6. 2. 2    |    | Т  | D            | м,         | Αſ              | 司     | 期: | 制       | 御    | 部     | の | 主           | な   | 0       | 路       |         |           |         |     |        |       |             |        | <br>         | 96  |

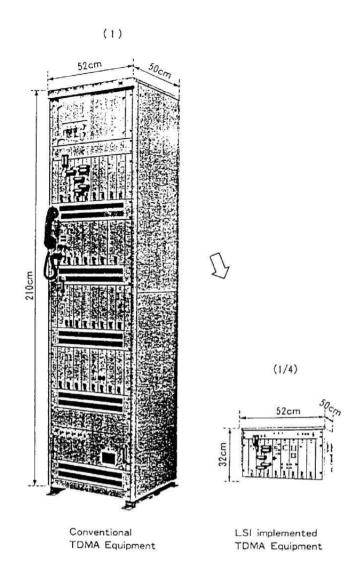

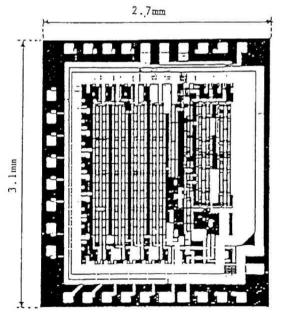

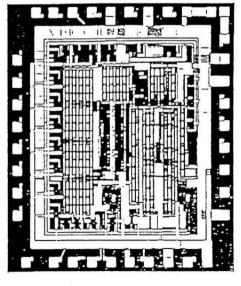

| ŧ | i.       | 3          |    | Т  | D            | м,         | Αď              | 麦     | 置  | の       | L    | s     | 1 | 化           | 手   | 法       |         |         |           | • • • • |     |        |       |             |        | <br>         | 100 |

|   |          | 6. 3. 1    |    |    |              | イ:         |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        | <br>         | 101 |

|   |          | 6. 3. 2    |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              | 101 |

|   |          | 6. 3. 3    |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              | 105 |

|   |          |            |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              |     |

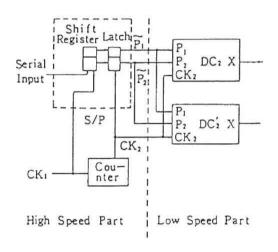

| C | i.       |            |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              | 107 |

|   |          | 6. 4. 1    |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              | 107 |

|   |          | 6. 4. 2    |    |    |              |            |                 |       |    |         |      |       |   |             |     |         |         |         |           |         |     |        |       |             |        |              | 108 |

|   |          | 6. 4. 3    |    | 衛: | 星:           | 搭章         | 战月              | Ħ     | S. | /       | P    | 変     | 換 | L           | S   | 1       | ۲       | Р       | / 9       | S       | 变 換 | LS     | 3     | ••          |        | <br>11111111 | 111 |

|   |          | 6. 4. 4    | 8  | 衛: | 星            | 搭重         | 战月              | Ħ.    | ュ. | =       |      | ク     | ワ | -           | ۲   | 検       | 出       | 器       | の相        | 冓 万     | 戉   |        |       |             |        | <br>         | 113 |

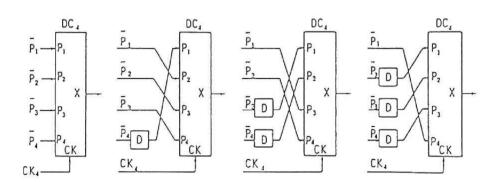

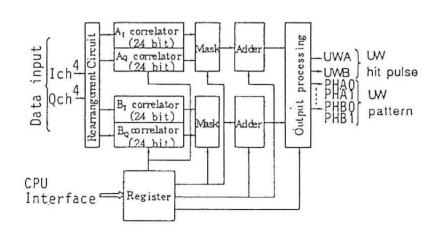

|   |          | 6. 4. 4. 1 |    | 高: | 速            | デ          | ٠ :             | 1     | 9  | ル       | 相    | 関     | 器 |             | *** |         | ****    |         |           | • • • • |     | *****  | ***** | *****       |        | <br>         | 113 |

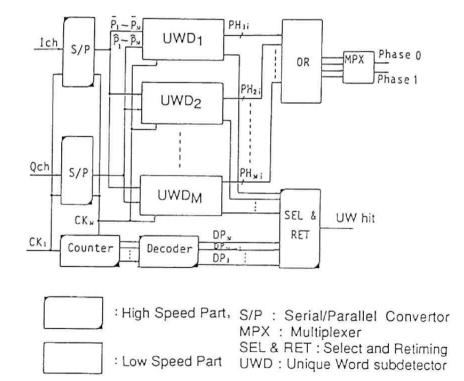

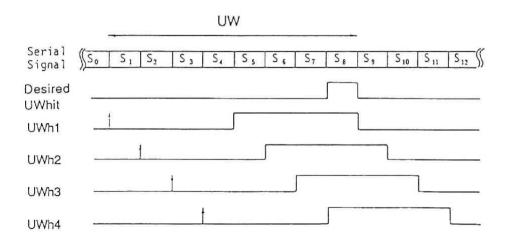

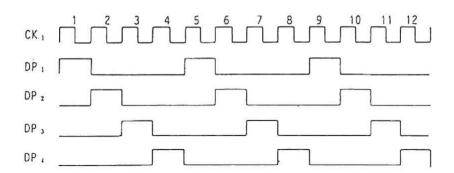

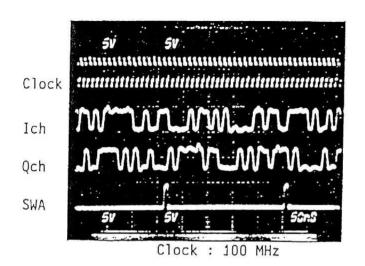

|   |          | 6. 4. 4. 2 |    | 高: | 速            | <b>그</b> : | = -             | -     | ク  | ワ       | _    | ۴     | ( | U           | W   | )       | 検       | 出       | 器         | 2       |     | erini, |       | •••••       | ••••   | <br>•••••    | 117 |

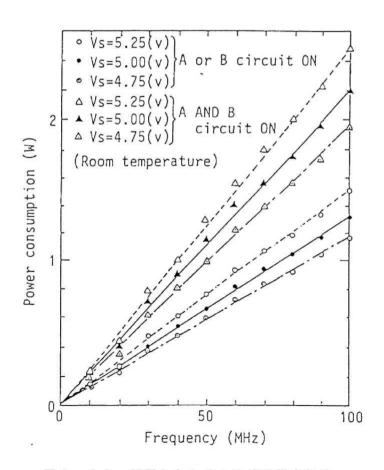

|   |          | 6.4.4.3    |    | 開: | 発            | U١         | Νŧ              | 食     | 出: | 88      | L    | S     | I | の           | 構   | 成       | Ł       | 特       | 性         | ٠       |     |        |       | •••••       |        | <br>         | 120 |

| e |          | 5          |    | む  | के .         | U          |                 |       |    |         | •••  |       |   | T. T. T. T. |     | 7.5.57  |         |         |           |         |     |        |       | rener.      |        | <br>         | 123 |

| 第7章   | 結言                                      |                                         |                                         |                                         | <br>                 | 124 |

|-------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------|-----|

| 参考文献  | *************************************** |                                         |                                         |                                         | <br>                 | 126 |

| 本論文に関 | する著者の                                   | 発表論文                                    | *************************************** |                                         | <br>                 | 135 |

| 謝辞    | *******                                 | *************************************** | *************************************** | *************************************** | <br>**************** | 139 |

\*

### 第1章 緒言

#### 1. 1 研究の背景

衛星通信の歴史は1960年にNASAがアルミ箔で覆った直径30mの風船衛星 Echo 1を高度約1,600kmに打上げたことにさかのぼる(\*\*)。この受動型衛星 を用いてNASA及びベル電話研究所がFM方式による電話及びTV信号の伝送に成功して以来、能動型静止衛星の時代を迎えて衛星通信は急速な発展を続けている。

衛星通信が固定通信の手段として実用化されて以来、衛星通信回線において広く用いられてきた通信方式は周波数分割多元接続方式(Frequency Division Multiple Access: FDMA)である。この方式は周波数帯域を分割して各局に割り当てる方式であり、変復調器の動作速度が低速となり、小型地球局による通信が可能という長所を有している。しかし、FDMA方式は衛星中継器で複数波を同時に増幅しなければならないことから、中継器の飽和動作点で運用することができず、衛星中継器当たりの伝送容量が小さくなるという欠点を有している。また種々の速度からなるディジタル信号伝送との親和性に乏しいという欠点も有している。これらの問題を解決するため、衛星中継器当たりの送信電力を最大限利用可能で種々の速度からなるディジタル信号伝送が容易に実現可能な時分割多元接続方式(Time Division Hultiple Access: TDMA)が考案され、これまで研究・開発が進められている。

衛星TDMA通信方式の歴史は1966年米国コムサット研究所による6Mbit/s TDMA通信(MATE方式)実験に始まる (2)。 我が国では1968年に、NTT電気通信研究所による13.664Mbit/s TDMA(SMAX)方式の実験が行われている (3)。 その後、種々の研究開発が各国で進められ、世界初の商用TDMAシステムが1976年にカナダで導入された (4)。 我が国ではNTTがSMAX方式の実験結果をもとにTDMA-60MおよびTDMA-100M方式を1982年に実用化した (5)。 一方、インテルサット衛星用TDMA通信方式も種々変遷後、1985年からはDSI付き120Mbitノs TDMA方式がインテルサットーV号衛星(14/12GHz帯)を用いて商用されている (5)。

本論文は衛星TDMA通信を実現する上で重要な技術である同期制御方式に関するものである。

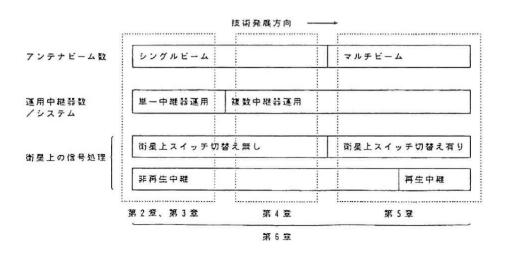

### 1.2 研究課題の所在

これまで実用化されて来た衛星TDMA通信システムは大型の地球局アンテナ、高出力の送信機及び大規模なTDMA装置を必要とするものであり、衛星TDMA通信の適用領域の拡大には更に①システム当たりの伝送容量の増大、②地球局の小型化・経済化、③柔軟な回線運用が必要となる。これらの条件を満足するため、技術発展方向としては次のように研究開発が進められている。

(1)シングルビーム衛星に搭載された単一中継器でTDMAシステムを構成する方式。 (単一中継器運用TDMA方式) (2) (7)

1

(2)シングルビーム衛星に搭載された複数中継器でTDMAシステムを構成する方式。 (複数中継器運用TDMA方式) (8) (9)

1

(3) マルチビーム衛星に搭載された複数中継器と中間周波スイッチによりTDMAシステム を構成する方式。 (Satellite Switched-TDMA: SS-TDMA方式) (10) (11)

1

(4)マルチビーム衛星に搭載された複数中継器を用いて再生中継を行うことによりTDMA システムを構成する方式。 (衛星上再生中継TDMA方式) (12) (13) (14)

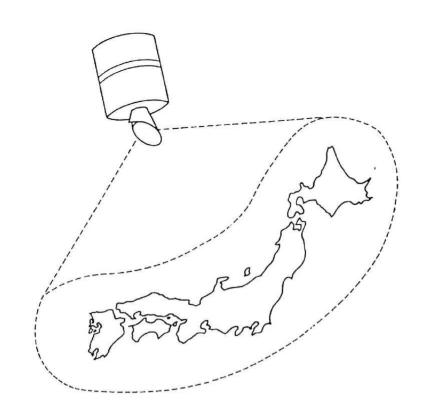

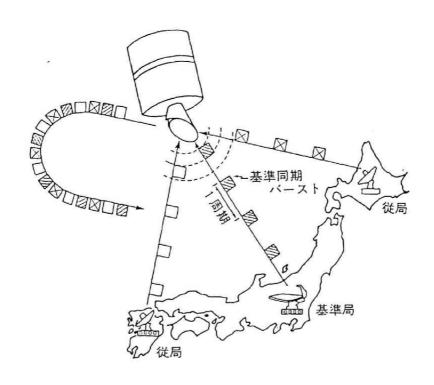

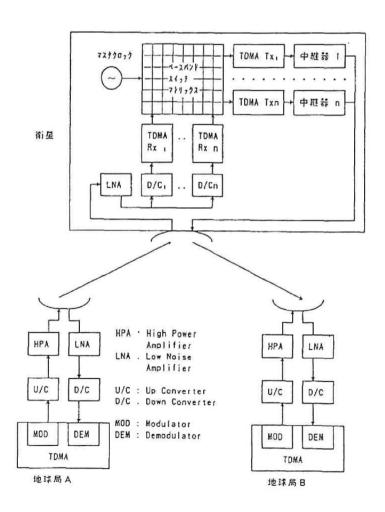

ここでシングルビーム衛星通信とは図1.1に示すように衛星アンテナの照射エリアが衛星通信のサービスエリアに対応しているシステムである。またマルチビーム衛星通信は図1.2に示すようにサービスエリアを複数のスポットビームにて照射する方式である。マルチビーム衛星通信は衛星アンテナ利得が高くなることから回線容量の増大、地球局の小型化が可能となる。一方、スポットビーム間の相互接続性を保証するため衛星上にてビーム切替えスイッチが必要となる。

以下に本論文で前提とするこれらTDMA方式の概略を述べ、研究課題の所在を明らかにする。

図1.1 シングルビーム衛星通信方式

図1.2 マルチビーム衛星通信方式

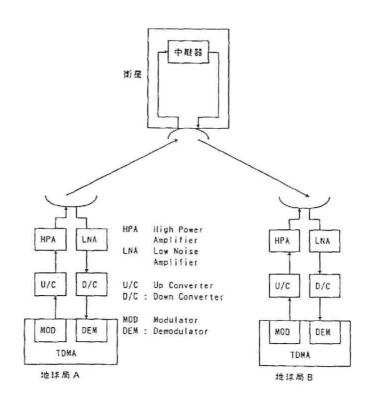

### 1. 2. 1 単一中継器運用TDMA方式

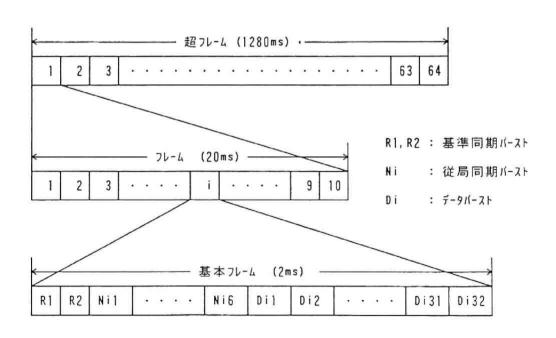

本方式は各種TDMA方式の基本となるもので図1.3に衛星TDMA通信の概念を示す。また単一中継器運用TDMA方式を構成する地球局と衛星の装置ブロック図を図1.4に示す。本TDMA方式では、まず衛星上で周期的に区切られた時間を考える。TDMAでは、この周期すなわちTDMAフレームを時間分割して各地球局に割り当てる。各地球局は自局の信号をその割当時間内に収まるように信号を送出する。従って各送信信号はTDMAフレームと等しい周期を持った断続信号となる。この断続信号を衛星TDMA通信では一般にバースト信号と呼ぶ。

各地球局のバースト信号は図に示すように衛星上で時間的に配列された形となり、地球局に戻ってくる。各地球局ではこれを受信し自局向けの信号が存在するタイムスロットを抜き出す。各地球局はバースト信号を送出するに当たって、それが衛星上で割り当てられた時間位置に置かれ、互いに衝突しないようにバースト送信時間を制御する。衛星上の時間位置は基準同期バーストと呼ばれるバースト信号を基準として決められる。基準同期バーストはTDMAシステムにおいて時間基準となる基準局から送信され、各地球局はその基準同期バーストに絶えず追従して各バースト信号の送信タイミングを制御する。

このような単一中継器運用TDMA方式において所要C/N値を小さくし、地球局アンテナ径および送信機の出力を低減させるため強力な誤り訂正 (Forward Error Correction: FEC)が用いられつつある。これまで大規模なハードウェアが要求されていた誤り訂正回路も近年のLSI化技術の進歩により、1チップLSI化が実現し容易にTDMA装置に適用可能な技術となっている。この強力な誤り訂正方式を用いたTDMAシステムでは、誤り訂正符号化がなされたデータ部の回線品質を一定値以上に保つため、誤り訂正符号化が施されていない同期語 (Unique Word: UW)に対する要求条件が厳しくなる。また安定な同期制御を行うためには同期制御信号に対する高信頼性が要求される。

図1.3 衛星TDMA通信の概念

図1 4 単一中継器運用TDMA方式

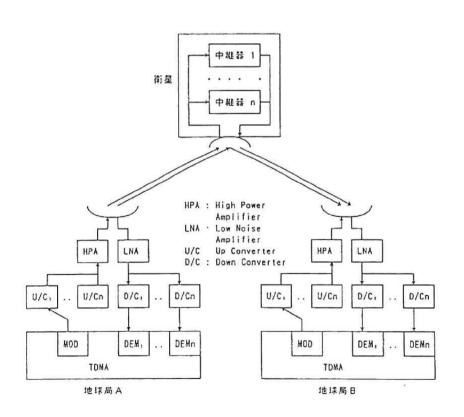

# 1. 2. 2 複数中継器運用TDMA方式

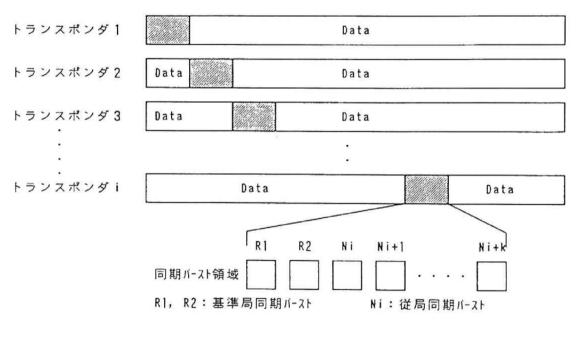

本方式はシステムに要求される伝送容量が1中継器の容量よりも大きい場合に用いられ、トランスポンダホッピング(Transponder Hopping)方式とも呼ばれる。本方式の特徴は図1.5に示すように各地球局が伝送すべきトラヒックをバースト信号ごとに周波数の異なるトランスポンダに向け送信または受信することにあり、衛星中継器の有する伝送容量を効率良く使用できる。この反面、各地球局では複数の周波数変換器と復調器が必要とされ、ハードウェアの増大により地球局装置が大型化するという問題がある。このため周波数変換器と復調器の台数を増大させることなくトランスポンダホッピング機能を実現するため新たなTDMA同期制御法、TDMA装置構成法が必要となる。

図1.5 複数中継器運用TDMA方式

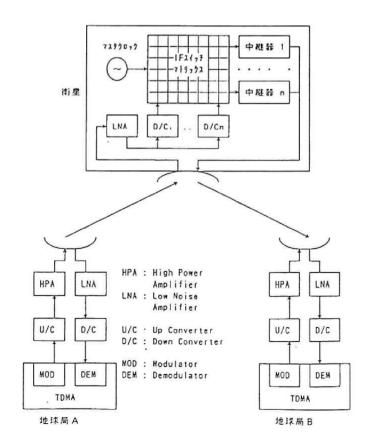

### 1. 2. 3 SS-TDMA方式

マルチビーム衛星通信では、図1・2で示したように衛星アンテナ利得を向上させることに加え、同一周波数を多数のスポットビームで同時に使用し、衛星通信に割り当てられた周波数を何重にも利用できる長所がある。このような衛星では一つのビームからの信号を他のビームへ接続するため、衛星上にビーム間接続の切替えスイッチが搭載される。この切替えスイッチはあらかじめ定められたシーケンスに従って切り替わり、同じシーケンスが各TDMAフレーム毎に繰り返される。一方、各地球局は自ビームと目的ビームが接続されるタイミングに合わせバースト信号を送出する。

SS-TDMA方式における装置ブロック図を図1.6に示す。本方式においては複数中継器運用TDMA方式における送信側U/C (Up Converter) 及び受信側D/C (Down Converter)のバースト毎に実時間で無線周波数を切り替える機能が、地球局ではなく衛星上に集約されたと考えられる。従ってSS-TDMA方式では各地球局は実時間でバースト信号周波数を指定する必要は無く、単一中継器運用TDMA方式と同様に簡易な地球局構成となる。このようなSS-TDMA方式では、衛星上に搭載された切り替えスイッチを駆動するマスタクロックを地上網の高安定なクロックといかに同期させるかが重要な課題の一つとなる。

図 1. 6 SS-TDMA方式

## 1. 2. 4 衛星上再生中継 T D M A 方式

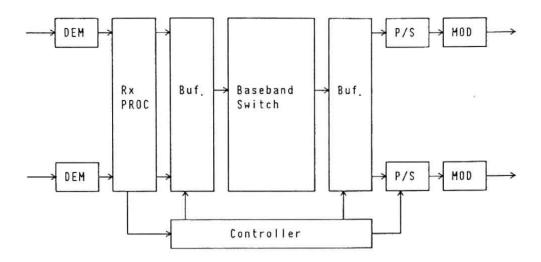

本方式の装置ブロック図を図1.7に示す。衛星上再生中継TDMA方式では、各地球局から送信されたバースト信号を衛星上で復調・再生し、他ビームからのバースト信号と搭載ベースバンドスイッチにより交換し、多重化した後、下り回線TDMA信号とする。本方式は衛星上でバースト信号が再生中継されるため回線品質の改善及び異速度のTDMA方式との相互接続が可能等の特徴を有する。従って柔軟な回線運用を行う上で有望な方式である。本方式を実現する上での技術的課題は搭載マスタクロックの地上網クロックへの同期化に加え、搭載TDMA装置のLSI化が鍵となる。

図1.7 衛星上再生中継TDMA方式

### 1.3 論文の概要

以上述べたように、本論文は単一中継器運用TDMA方式から衛星上再生中継TDMA方式に至る各種TDMA方式において、技術的課題となる同期制御法、同期制御装置構成法について研究した結果をまとめたものである。各章の位置づけを図1.8に示す。.

第2章ではシングルビームでかつ単一中継器でのTDMA通信方式において、同期制御の基礎となるTDMA送受信同期制御法について整理し、フィードバックループ法による同期制御が適することを示す。更に本フィードバックループ法を実現する上で課題となる同期制御信号伝送特性の改善について明らかにする。

第3章では強力な誤り訂正方式を採用した場合において、単一中継器TDMA通信方式の同期語検出法について検討を行い、新たに符号化ユニークワード検出法を提案する。さらに実験により符号化ユニークワード検出法の特性を明らかにし、その有効性を示す。

第4章では複数中継器運用TDMA方式において技術的課題となるTDMA同期法について検討を行い、複数中継器運用TDMA方式に適したフレーム構成の提案を行う。更に地球局装置を小型化・簡易化するためバースト復調器の構成について検討を行い、新たに記憶型バースト復調器AFC (Automatic Frequency Control) 回路を提案し、実験的にその特性を明らかにする。

第5章ではSS-TDMA方式及び衛星上再生中継TDMA方式を実現する上で技術的課題となる搭載マスタクロックの制御法について検討を行い、マスタクロックの最適制御間隔を理論的に導出する。また実験により理論の妥当性を明らかにする。

第6章では地球局TDMA装置及び衛星上TDMA装置を小型化する上で鍵となる大規模TDMA装置のLSI化手法について検討を行い、その設計法を明らかにする。

第7章は第2章から第6章までの研究結果を総括し、本論文のまとめとしている。

図1.8 各章の位置づけ

### 第2章 同期制御

### 2.1 まえがき

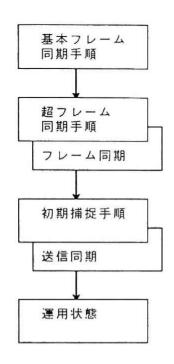

TDMA通信では、各局が送信するバーストが互いに衝突して通信の障害とならないように種々の同期をとることが必要となる。本章では全ての衛星TDMA方式において基本となる単一中継器運用TDMA方式に関して、①TDMAシステムの時間基準をとるための受信同期、②情報送信のためのデータバーストの送出を可能とするためのTDMAシステムへの初期捕捉(Initial Acquisition)および、③定常的に通信を行うための同期(送信同期)に分類して考察する。初期捕捉については後述する距離推定方を用いた場合に技術的課題となる初期捕捉ウィンドウについて検討を行い、送信同期については、後述するフィードバックループ制御方を用いた場合に問題となる同期制御情報の高信頼化について検討を行う。

### 2. 2 送受信同期制御法

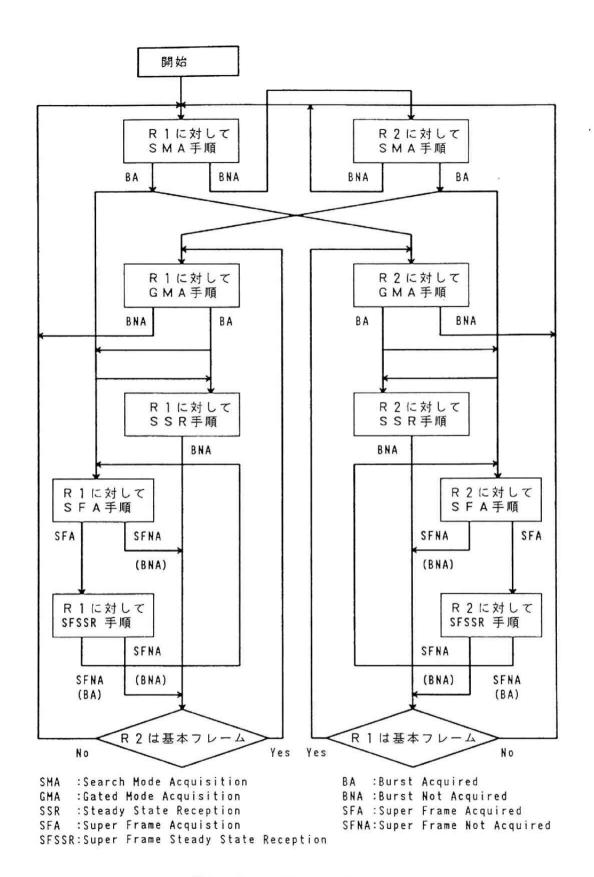

従局TDMA装置の同期制御手順を図2.1に示す。以下では図2.2に示したフレーム構成を例にとりこれらの同期制御について考察する。

本TDMAフレーム構成例では基準局は2局あり、それぞれ基準同期バーストR1、R2を2msの周期で送出する。2基準局(R1局およびR2局)は互いに相補的に機能する。TDMA通信に参加する最初の局(例えばR1局)には初期接続制御および送信同期制御は必要なく自局送信信号を受信するための受信同期が必要となるのみである。第2番目の局からは初期接続および送信同期制御が必要となる。R2局および他の従局はこれらの同期後初めて通信が可能となる。

# 2. 2. 1 受信同期(1)(2)

基準局より送信された基準同期バーストをもとに生成されるTDMAフレームは衛星上にて各地球局に依存しない1中継器当たり唯一のフレームとなる。各地球局は衛星から送信されるこのフレームを共通に受信する。しかし各地球局は地理的に異なった場所に位置しているため、絶対時間の異なったフレームを受信することになる。また、この受信フレームは衛星の位置変動に伴い、それぞれの局にて時々刻々変化する。従って各地球局では受信信号から時間基準となる基準同期バーストを検出し、これを時間基準として受信フレ

図2.1 従局TDMA装置の同期制御

図2.2 T D M A フレーム構成

- ムを作成することが最初に必要となる。この基準同期バーストを検出し受信フレームを 確立するまでを受信同期といい、一般に基準同期バーストの受信周期を周期とするフレー ム (ここでは基本フレームと呼ぶ) に対する同期確立が必要となる。受信同期制御フロー を図2.3に示し、以下にその動作を述べる。

#### (a) 基本フレーム同期

基準局が2局構成の場合、通常以下に示す3種の手順を経て同期が確立される。

#### ① S M A (Search Mode Acquisition) 手順

基準同期バーストR1およびR2のいずれをも捕捉していない状態で適用される手順であり、R1およびR2のユニークワード(UW: Unique Word)をオープンアパーチャ(Open Aperture: TDMAフレーム上の位置を限定せず、全フレームにわたる動作)で探索する。UWを検出すると受信フレームカウンタがリセットされ、ナローアパーチャ(Narrow Aperture: 次のフレームでUWの検出が予定される時間位置付近に限定してUWを検出する動作)でのUW検出モードへ移行する。通常、オープンアパーチャ動作時の誤検出率を低くするためUWの相関検出閾値(Correlation Threshold)を低くし、ナローアパーチャにて複数回のUW検出が連続してなされた後、初めてSMA手順完了となる(後方保護と呼ばれる)。

#### ②GMA (Gated Mode Acquisition) 手順

SMA手順で一方の基準同期バーストを捕捉後、他方の基準同期バーストを捕捉するための手順であり、受信タイミングが確立していることから、まだ捕捉していない基準同期バーストをナローアパーチャ動作で探索・検出する。

### ③SSR (Steady State Reception)手順

SMA手順およびGMA手順でR1およびR2基準同期バーストの同期確立後、定常的に受信同期を保持する手順である。降雨等により回線品質が劣化した場合に基準同期バーストのUW不検出率が増加するが、1回の不検出で同期外れとみなさずに通常複数回の連続不検出をもって同期はずれとする(前方保護と呼ばれる)。

### (b) 超フレーム同期

超フレーム同期は基本フレーム同期確立後引き続いて行われる同期手順であり、基本フレーム同期と同様に超フレーム同期確立のための手順(SFA手順:Super Frame Acquistion)と超フレーム同期保持の手順(SFSSR手順:Super Frame Steady State Reception)とからなる。基本フレーム同期と同様に通常超フレームUW検出において後方保護および前方保護がかけられ、それぞれ同期確立および保持の確度を上げている。以上の手順で基本および超フレーム同期が確立し、受信同期確立が完了する。

図2.3 受信同期制御フロー

# 2. 2. 2 初期捕捉(3)(4)

### 2. 2. 2. 1 初期捕捉法

初期捕捉 (Initial Acquisition)は受信同期確立後、地球局と衛星との距離をもとに送信タイミングを決定するために必要な機能であり、送信タイミング設定確度の向上、装置簡易化等の観点から種々検討されている。

#### (1) m - シークエンス法 (低レベル初期捕捉)

本方法ではM系列符号の特徴を生かし、通信中の回線にできるだけ干渉を与えないように低レベルで送信したM系列と衛星を介して受信したM系列を比較し、地球局と衛星間の距離を測定する。測定結果をもとに所期のタイムスロット位置に送信すべきタイミングを決定する。

この方法の利点としては、①衛星の軌道情報を必要としない、②距離予測のための計算機を必要としない、③初期捕捉用ウィンドウを必要としない、④特に正規信号伝送速度と同一信号速度でM系列を送信する場合にはアクジション用の特別な変復調器を必要としない等がある。また欠点として①既に通信中の回線に干渉を与える。②低レベルで送受信するため、多数決判定の採用等、高い符号誤りへの配慮が必要等がある。本方法の初期捕捉信号レベルとしては通常正規レベルよりも20dB程度低い値が用いられる。

#### (2) 受信同期法(高レベル初期捕捉)

一般に地理的に異なる場所に位置する3局で測距をすれば静止衛星の位置を高精度に推定が可能なことから、衛星の正確な位置を推定し、各従局の地理的位置を考慮した送信フレームタイミングを基準局が決定し各従局に通知することにより高レベルにて初期捕捉を行う方法である。本方法は従局における特別な初期捕捉機能を必要とせずオープンループ方式による初期捕捉方式に属する。

#### (3) 距離推定法(高レベル初期捕捉)

距離推定法は、衛星の軌道情報により各従局にて衛星と地球局の距離を推定して初期捕捉を行う方法である。また衛星―地球局間の距離推定は(2)で述べた方法を用いて行うことも可能であるが、受信同期法との大きな差は本方法では衛星折り返し信号を自局または基準局にて受信し正規のバーストを送信する以前のその同期精度を高めることである。

距離推定方式では、通常プリアンブルと呼ばれる搬送波、クロック再生符号と同期語の みからなる短バーストを初期捕捉バーストとして高レベル(正規レベル)にてフレーム中 の空きバースト部へ送信する。従って他の回線へ干渉を与えないためには初期捕捉バースト送信タイミング精度以上の空きバースト領域(初期捕捉ウィンドウ)が必要となる。この方法の利点は①正規レベルで初期捕捉信号を送信することから回線品質の良い状態で同期信号の検出ができる。②通信中の他の回線に干渉を与えない。③基準局にて従局発初期捕捉バーストの復調・位相誤差検出を行い、各従局に通知するフィードバックループ方式との併用により基準局の負担は大となるが従局初期捕捉機能の簡易化が図れることである。また、欠点としてはフレーム長の短い場合、フレーム内の大部分を初期捕捉ウィンドウ領域として配分しなくてはならずフレーム利用効率を著しく劣化させる点である。しかし、伸張/圧縮バッファに利用可能なメモリの大容量化に伴い、TDMAフレーム長が長くなりこの欠点はほとんど問題とならなくなっている。本方法を用いた初期接続法が国内衛星通信用TDMA方式では主に用いられている。次節では本初期捕捉法を用いた場合に重要となる初期捕捉ウィンドウ幅について考察する。

#### 2. 2. 2. 2 初期捕捉用ウィンドウ幅

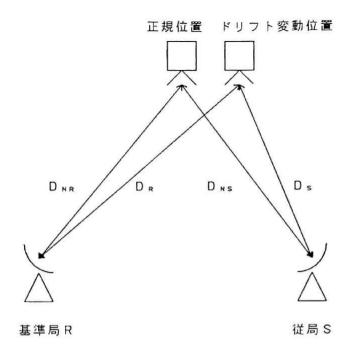

日本のように狭いサービスエリアを対象としたTDMA方式では静止衛星の正規位置と 基準局との距離をもとにして各従局と衛星との伝搬距離を決定し、初期捕捉を行う距離推 定法(1点測距)が主に用いられている。本方式では基準局からの受信フレームタイミン グを基準とし、基準局から指定された時間 d だけ遅延させて送信タイミングを取り、バー ストを送信する。しかし衛星は正規位置にはとざまらず、絶えずドリフト運動をしている ため、従局のバースト送信位置は正確なものとは言えず、バースト送信位置の誤差が伴う 。この許容すべき誤差の範囲を初期捕捉用ウィンドウ幅と呼び、以下に本ウィンドウ幅に 対する設計法を述べる。

まず、図2・4に示すように基準局Rが自局の往復伝搬遅延時間DRを測定する。基準局Rでは、このDRと予め知っている衛星の正規位置での往復伝搬遅延時間DBRとを比較し(DR-DNR)を求め、従局Sにこの分だけ遅延するよう指示する。つまり基準局Rは、自局における衛星の正規位置からの位置変動が従局Sに対しても同じとみなすことになる。しかし、従局Sにおける衛星の正規位置からの変動は(Ds-DNS)であるのでそこに誤差が存在する。従って、システムを運用する上で、初期捕捉時のバースト送信位置に、この誤差を見込んだウィンドウをあける必要がある。

図2. 4 衛星と地球局間の距離変動

ここで基準局Rが従局Sに指示する情報は

$$\Delta D_R = D_R - D_{NR} \tag{2-1}$$

であり、従局Sが実際に持つ衛星の正規位置からの誤差は、

$$\Delta D_s = D_s - D_{NS} \tag{2-2}$$

である。この両者の差分ΔDがバースト位置誤差である。

$$\Delta D = \Delta D_R - \Delta D_S \qquad (2-3)$$

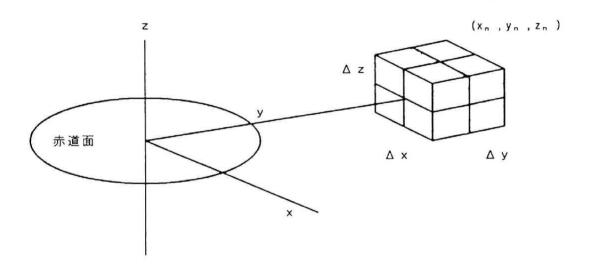

ここで図 2 . 5 に示すように、 衛星の正規位置の座標を  $(x_n, y_n, z_n)$  とし、各座標軸方向へのドリフトの最大移動量を  $(\Delta x, \Delta y, \Delta z)$  とすると、衛星の座標は

$$\begin{cases} x' = x_n + \Delta x = \Delta x \\ y' = y_n + \Delta y \\ z' = z_n + \Delta z = \Delta z \end{cases}$$

(2-4)

と表すことができる。但しこの場合、衛星の正規位置座標をx。=z。=0とした。

図2.5 衛星の位置保持精度

また基準局 R の衛星に対する相対的緯度、経度を( $\theta_R$  ,  $\phi_R$  )、その座標を( $x_R$  ,  $y_R$  ,  $z_R$  )とし、従局 S のそれらを( $\theta_S$  ,  $\phi_S$  ) , ( $x_S$  ,  $y_S$  ,  $z_S$  )とすると

$$\Delta D_{R} = D_{R} - D_{NR}$$

$$= \{ (\Delta x - x_{R})^{2} + (y_{n} + \Delta y - y_{R})^{2} + (\Delta z - z_{R})^{2} \}^{-1/2}$$

$$- \{ x_{R}^{2} + (y_{n} - y_{R})^{2} + z_{R}^{-2} \}^{-1/2}$$

$$\Delta D_{s} = D_{s} - D_{NS}$$

$$= \{ (\Delta x - x_{s})^{2} + (y_{n} + \Delta y - y_{s})^{2} + (\Delta z - z_{s})^{2} \}^{1/2}$$

$$- \{ x_{s}^{2} + (y_{n} - y_{s})^{2} + z_{s}^{2} \}^{1/2}$$

となる。

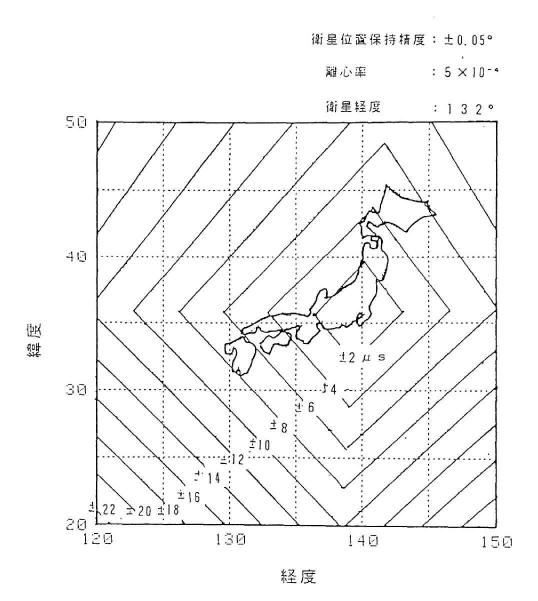

静止衛星の軌道位置を東経132°及び位置保持精度を東西・南北0.05°以下、難心率 10<sup>-4</sup>とした時の初期捕捉用ウィンドウ幅△Dの具体的数値を等高線として図2.6に示す

図2.6 初期捕捉用ウィンドウ幅

# 2. 2. 3 送信同期(3)

送信同期はバースト同期とも呼ばれ、初期捕捉後のTDMA通信中に必要となる定常的なバーストの送信タイミング制御をいう。

送信同期法には、初期捕捉法と同様にオープンループ法、クローズドループ法およびフィードバックループ法がある。

## (1) オープンループ法

本方法は初期捕捉における受信同期法を定常状態でも継続し続ける方法である。オープンループ法による送信同期では1局または複数局により、衛星の軌道位置を決定し、更に各従局、衛星間の距離を求め、この距離データに基づいて各従局の送信タイミングを決定する。

図2.7 オープンループによる送信同期の原理

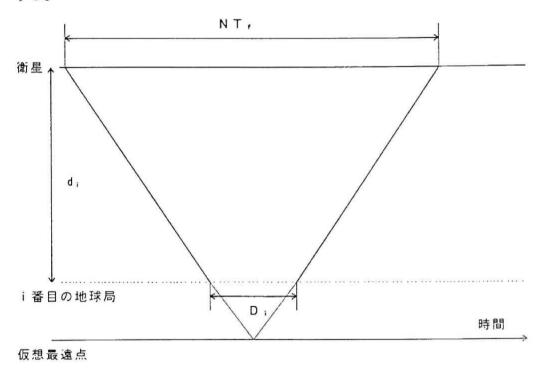

オープンループ法による送信同期の原理を図2.7に示す。仮想最遠点はフレーム長の整数倍でかつ地球局—衛星間の最大距離よりも大となるように選定する。こうすることにより、仮想最遠点に地球局がある場合には、基準同期バースト(R)を受信した時刻が送信フレーム基準タイミングとなる。そこでi番目の地球局は地球局と仮想最遠点との時間差Diだけ時間を遅らせたタイミングを送信フレーム基準タイミングとする。Diは図2

. 7からわかるように次式で与えられる。

$D_i = N T_f - 2 d_i / c$

(2-7)

但し

c : 光速

, N:整数

T: フレーム長 , d: 衛星~地球局 i 間の距離

本方法はd;が正確に測定できれば精度の高い同期が得られ、低速TDMA方式の場合には数シンボルのガードタイムでよいことから、低速TDMA通信において用いることが多い。

### (2) クローズドループ法

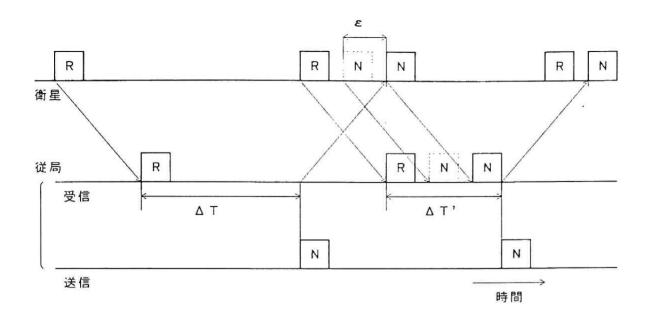

自局が送信した衛星折り返し同期バーストを受信し、TDMAフレーム上所定の位置に保持するよう送信タイミングを制御する方法である。従って初期捕捉法としてはクローズドループによる距離推定法を用いた場合には初期捕捉完了後スムーズに送信同期フェーズに移行される。この概略を図2.8、図2.9に示す。

図2.8 クローズドループ法の概念図

R : 基準同期バースト

N : 従局同期バースト

図2.9 クローズドループ法によるタイミング制御

地球局(従局)は衛星距離データから推定した送信タイミング値 Δ T だけ基準同期バースト受信タイミングを遅らせて初期捕捉バーストを送出する。衛星から再送信されたこのバーストを受信することにより本例ではをだけ所定位置より進んでいることがわかる。そこで従局は次フレームから新しい Δ T ' (= Δ T - ε)を設定し同期バーストを送信する。これにより衛星では所定の位置に同期バーストが受信されることになる。この結果、従局は他の通信回線に干渉を与えることなく、データバーストを送出し通信を行うことができるようになる。定常状態では後述のガードタイム内を種々の要因により同期バーストが移動することから、この同期バーストを所定位置に保持するよう制御しつづける。

衛星から再送信された自局送信バーストを自局で受信することが必要なことから本方式 はシングルビーム衛星通信方式には適するものの一般にマルチビーム衛星通信方式には適 さない。

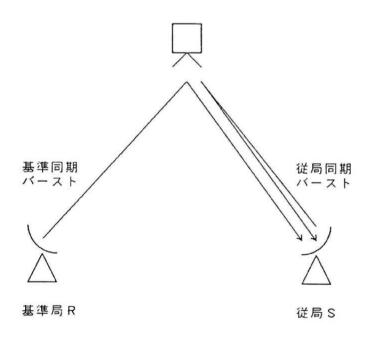

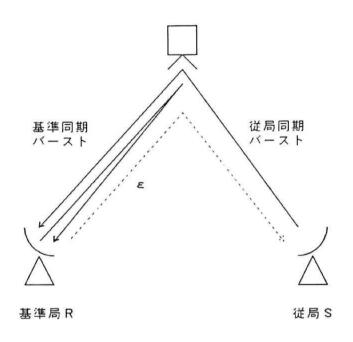

#### (3) フィードバックループ法

フィードバックループ法は衛星から再送信された自局送信同期バーストを当該従局では 受信せず、基準局が受信し、フレーム上での位置誤差を検出する。基準局はこの検出した

位置誤差をそれぞれの従局に衛星回線(通常は基準同期バーストに含まれる)を介して伝送する。各従局はこの位置誤差データを受信し、送信タイミングを制御する。本方法の概念を図2.10に示す。本方法は衛星から再送信された自局送信信号を受信する必要がないことから、シングルビーム衛星通信方式に加えマルチビーム衛星通信においても適用可能である。

図2.10 フィードバックループの概念図

本方法の特徴は従局におけるバースト位置誤差測定の機能が不必要なことから、従局TDMA装置の小型化・経済化が可能であること及びそれに伴い基準局TDMA装置にて全従局同期バーストの位置誤差を測定する必要がありクローズドループ方式に比較し基準局TDMA装置に能力増加を図らねばならないことである。

また、一般に基準局には大型アンテナが使用される一方、従局では小型アンテナが使用されることから、フィードバックループ法を用いた場合には、クローズドループ法よりも高い同期維持特性が達成可能であり、近年の衛星通信用TDMA方式ではフィードバックループ方式が広く用いられている。フィードバックループ法を実現する上で重要な点は基準局で測定した従局同期バーストの同期タイミング誤差をの転送方法である。次節では基準局から従局方向の同期制御信号転送に関する高信頼化について述べる。

#### 同期制御信号伝送特性の改善法(5)(6)(7) 2.3

近年、多くの衛星通信システムでは回線品質の改善、実効的な回線容量の増大を図るた め、FEC (Forward Error Correction)が広く用いられてきている(\*)(\*)。FECの中で も特に高符号化利得が得られる畳込み符号化軟判定ビタビ復号が最も多く用いられており 、多数のビタビ復号器LSIが報告されている(8)(9)(10)。一方、衛星通信用TDMAシ ステムにおける各種同期制御信号にはデータ信号以上の高信頼性が要求されるため、誤り 制御方式としてハードウェア上構成の簡易な多数決判定法がしばしば用いられている(8)

これまで畳込み符号化ビタビ復号を行う通信路において多数決判定法を採用した衛星通 信システムの制御信号伝送特性に関する詳細な報告はなされていなかった。また、ビタビ 復号後の符号誤りパターンに関しては、バースト的であることがこれまでに指摘されてお り(\*)(い)(い)、多数決判定の実現法によって信号の信頼性が大きく異なる。

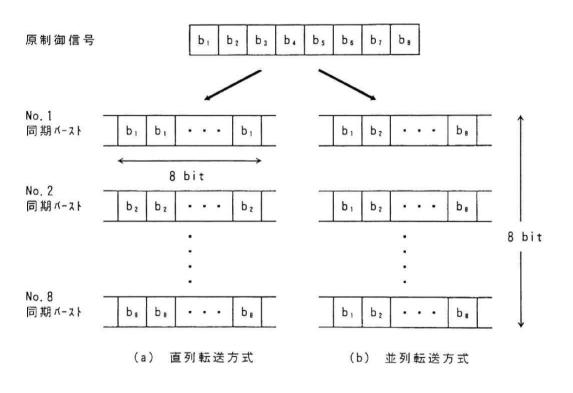

本節では、この問題を解決するため多数決判定の実現法として、並列転送方式を提案し 、直列転送方式(い)との信号伝送信頼性の評価を行う。この結果、並列転送方式の信号伝 送信頼性が大幅に改善されることを示す。

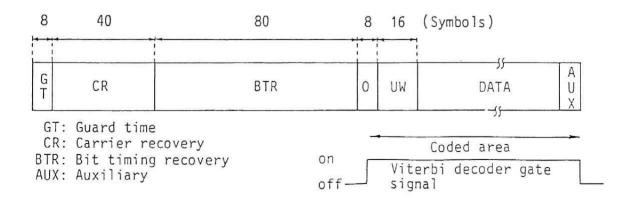

# 2.3.1 直列転送方式と並列転送方式

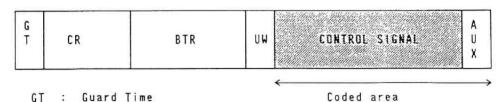

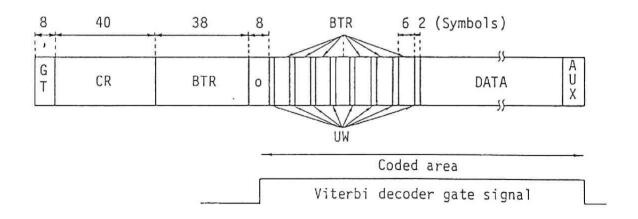

TDMA方式における同期制御信号は一般に図2.11に示す同期バーストまたはデー タバーストにより転送される。以下の議論では同期バーストにより制御信号を転送する場 合を示すが、データバーストを用いた場合でも同様である。同期バーストによる制御信号 伝送は一般にマルチフレーム構成をとることが多く(13)、複数同期バーストにより1制御 信号の転送を行う。ここではnビットの制御信号(b,-b,)を1ブロックとして扱い、 mビット多数決判定する場合について検討を行う。

GT : Guard Time

CR : Carrier Recovery BTR : Bit Timing Recovery

AUX : Auxiliary

図2.11 同期バースト構成

ここで、ハードウェア構成簡易化の観点からn及びmは次式を満足するものとする。

$$n=8\cdot N$$

,  $m=8\cdot M$  (2-8) 但し、 $N$ 、 $M$ は自然数

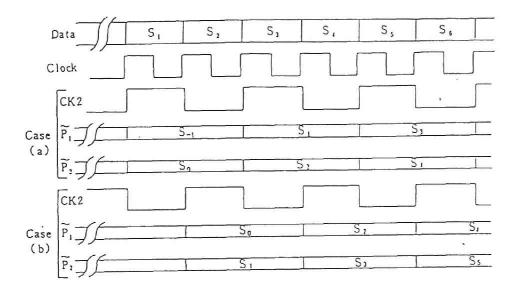

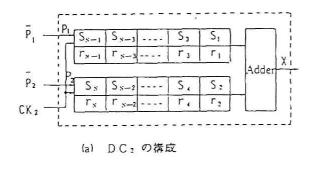

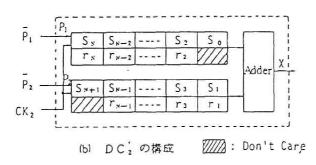

原制御信号から多数決判定用符号を生成し転送するには、図2.12に示すように直列転送方式と新たに提案する並列転送方式がある。前者は原制御信号のビットストリームに従い1ビット毎にmビット多数決判定用符号を生成し(本例ではm=8)、同期バーストとして転送する方式である。後者は原制御信号ブロックを1ブロック/同期バーストとしてm回(m個の同期バーストを用いて)転送する方式である。

図 2 . 1 2 制御信号転送方式

### 2. 3. 2 バースト誤りパターンの理論的検討

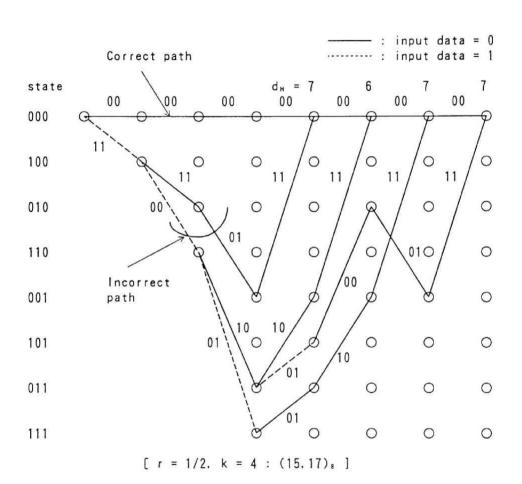

ビタビ復号アルゴリズムは最尤パスを探索するためにトレリス構造を用いている(1.1)。 雑音の影響を受けた受信信号の最尤パスを探索するに当たっては、ビタビ復号器が誤った パスを選択する場合が発生する。これがバースト誤りを起こす原因となる。例として図 2 . 13に符号化率 1/2、拘束長 4の最適畳み込み符号のトレリス構造を示す。図 2. 1 3では、正しいパスを全"0"パターンと仮定している。

第1種の誤りと呼ばれる事象は、任意のノードにおいてパスが再結合する際に正しいパスが排除されることをいう。

図2.13 第1種誤りによるバースト誤り

ビタビ復号後のバースト誤りパターンを計算機探索により導出し、その結果をハミング 距離 (dn) とともに表 2. 1 および 2. 2 に示す。表 2. 1 は符号化率 1 / 2、拘束長 4 の場合であり、表 2. 2 は符号化率 1 / 2、拘束長 7 の場合である。

これらのバースト誤りは従来の直列転送方式による多数決判定の信頼性を大きく劣化させる原因となる。

| dн | Error pattern    |    |

|----|------------------|----|

| 6  | 11               |    |

| 7  | 1<br>111<br>1101 |    |

|    | 101              | 87 |

| 8  | 1111<br>11101    |    |

|    | 110011<br>110101 |    |

| dн | Error pattern |  |

|----|---------------|--|

|    | 1             |  |

|    | 11            |  |

|    | 111           |  |

|    | 1001          |  |

|    | 1011          |  |

| 10 | 11001         |  |

|    | 10101         |  |

| 18 | 111001        |  |

| 1  | 1100111       |  |

| 1  | 10101001      |  |

|    | 1100111001    |  |

## 2. 3. 3 ブロック無効確率とブロック誤り確率

mビット多数決判定法では、m/2ビットの誤りが発生すればそのビットに対する判定 結果は無効とし、m/2+1ビット以上の誤りがある場合に誤りとなる。原制御信号b,~ b。のブロックで1ビット以上の無効判定が発生するブロック無効確率をP」とし、1ビ ット以上の誤りが発生するブロック誤り確率をPょとするとP,及びP。はそれぞれ(2.9) )及び(2.10)式で表される。尚、ユニークワードの不検出,誤検出確率は無視できるもの と仮定する。

$$P_{i} = \sum_{i=1}^{n} C_{i} a'_{m/2} (1 - a_{m/2})^{n-1}$$

(2-9)

$$P_{f} = \sum_{k=1}^{n} {C_{k}} \left( \sum_{i=m/2+1}^{m} a_{i} \right)^{k} \left( \sum_{j=0}^{m/2-1} a_{j} \right)^{n-k}$$

(2-10)

但し、a::多数決判定においてmビット中iビット誤る確率

a;は直列転送方式の場合には、誤り訂正復号後のバースト誤り特性に依存するため実 験的に導出する必要がある。一方、並列転送方式の場合には、各ビットは異なる同期バー ストで伝送されることから互いに独立な符号誤り特性を有する。この場合のa;をa;゚

とするとarは次式で与えられる。

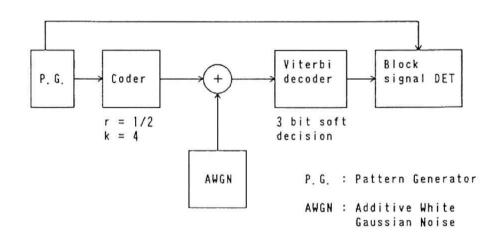

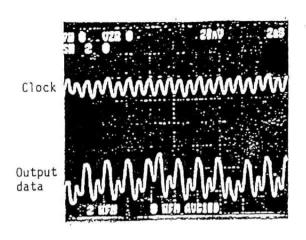

### 2.3.4 実験

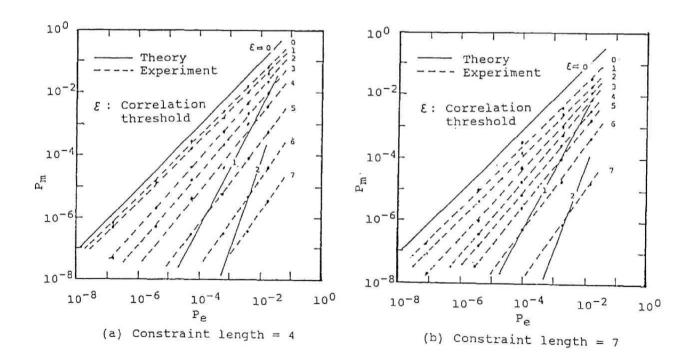

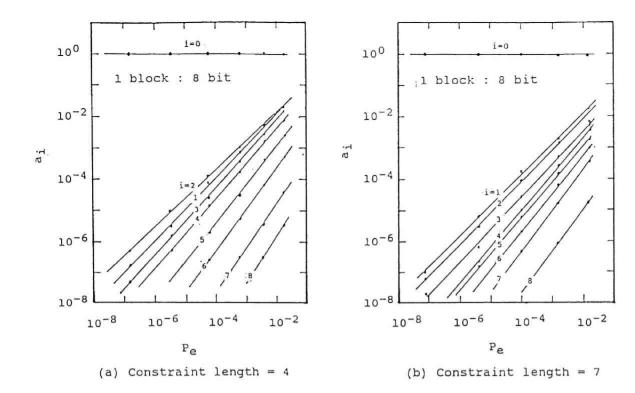

符号化率 1/2、拘束長 4 および 7 のたたみ込み符号化-3 ビット軟判定ビタビ復号に対する復号後のバースト誤り特性について実験的に評価を行っている。また以下の実験的検討では n=8 , m=8 の場合を取り扱っている。

図 2 . 1 4 実験回路

a;を導出するための実験回路を図2.14に示す。本実験回路ではブロック信号"11111111"を送出し、受信側で相関閾値をに設定したブロック信号検出回路を用いて不検出率を測定した。不検出率特性 Pmを図2.15に示す。図中、実線は符号誤りパターンがランダムである場合の理論値を示しており、これと比較しバースト誤りのため Pm特性が劣化していることがわかる。a,を用いて Pm(を)を表現すると次式を得る。

$$\begin{cases}

P_{m}(\varepsilon) = \sum_{i=\varepsilon+1}^{8} a_{i} & (0 \le \varepsilon \le 7) \\

i = \varepsilon + 1

\end{cases}$$

$$P_{m}(8) = 0$$

$$(2 - 1 2)$$

従って(2.12)式よりa, は次式で与えられる。

$$\begin{cases} a_0 = 1 - \sum_{i=1}^{8} a_i = 1 - P_m(0) \\ a_i = P_m(i-1) - P_m(i) & (0 \le i \le 8) \end{cases}$$

(2-13)

図2. 15及び(2.13)式から導出したa;を図2. 16に示す。1ブロック中2ビット誤り確率の高いことが図2. 16より明らかである。

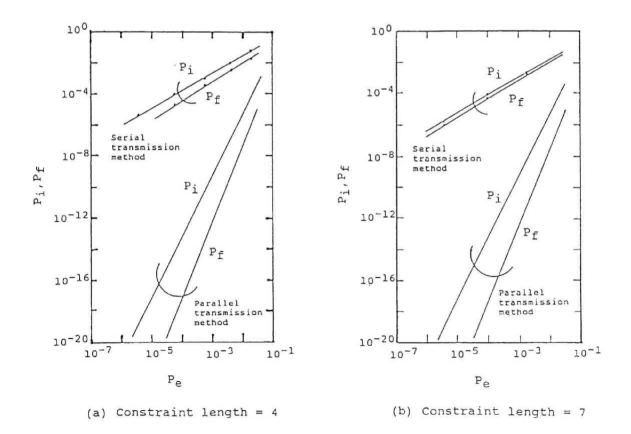

次に図2.16及び(2.9)、(2.10)、(2.13)式を用いて直列転送方式のP:, P·を求め図2.17に示す。また、並列転送方式は(2.9)、(2.10)、(2.11)式を用いて導出できる。並列転送方式のP:, P·を同様に図2.17に示す。

図よりPe=1×10⁻⁴においてPi,Piとも並列転送方式の方が直列転送方式より約10 桁改善されることがわかる。

図2.15 不検出率特性

図2.16 ブロック内における i ビット誤りの確率特性 (測定値)

図2. 17 ブロック無効確率 (Pi) およびブロック誤り確率(Pf)特性

## 2. 4 むすび

本章では単一中継器運用TDMA方式において基本となる受信同期法、初期捕捉法、送信同期法について整理を図った。次に初期捕捉法に関して、距離推定法を用いた場合に技術的課題となる初期捕捉ウィンドウについて考察を行った。この結果通信衛星CS-3レベルの衛星位置保持精度(±0.05°)を有する静止衛星の場合±10μsの初期捕捉ウィンドウ幅で十分なことを示した。

送信同期に関しては、従局TDMA装置を簡易化でき降雨に対して同期保持特性に優れたフィードバックループ法で技術的課題となる同期制御信号の高信頼化について考察を行った。この結果、誤り訂正に加え多数決判定を採用した場合における制御信号の転送方法として並列転送方式を提案し、同期制御信号のブロック無効確率およびブロック誤り確率という観点から評価を行った。提案する並列転送方式は従来方式である直列転送方式と比較し、8ビット多数決判定の場合、Pe = 1×10<sup>-4</sup>において同期制御信号を正しく受信できる確率を10桁程度改善できることを明らかとした。

### 第3章 同期語

#### 3. 1 まえがき

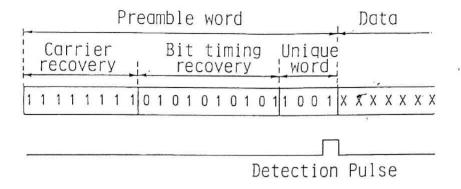

TDMA方式においては、各々の地球局の送信するバースト信号は、互いに重なり合わず、かつそれぞれのバースト信号を識別できなければならない。まず、バースト信号を正しく復調するため、バースト信号の先頭に搬送波再生信号、クロック再生信号、同期語信号 (Unique Word:UW) からなるプリアンブル部 (Preamble)を通常使用する。搬送波再生信号、クロック再生信号はディジタル変調されたバースト信号を同期検波する際に必要となる信号であり、受信側で搬送波同期とクロック同期を確立するために用いられる。一方、同期語はディジタル復調された信号をもとにワード同期を確立し、各々のバースト信号の種別を認識するために用いられる (1)(2)(3)。

本章では、まず同期語検出器の構成と特性について述べ、所望する同期特性を得るための同期語長、同期語パターンの選定法、相関閾値について述べる。またこれら同期語検出特性を改善する方法について提案しその特性を明らかにする。以下の説明では同期語をUWと略す。

#### 3.2 同期語検出器の構成と特性

#### 3.2.1 同期語検出器の構成

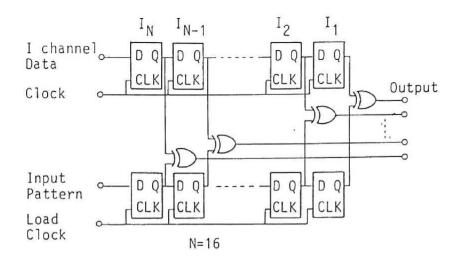

UW検出パルスとバースト構成との関係を図3.1に示す。正常にUWパターンの検出が行われた場合には、UW検出器での処理遅延を無視するとUW部分の最後のビット位置にてUW検出パルスが得られる。このようなUWパターンを検出するためのUW検出器は図3.2に示すようなディジタル相関器(4)が基本となる。つまりロビットシフトレジスタに入力されたバーストは逐次固定パターンと比較され不一致ビット数が加算回路によって積算される。出力される不一致ビット数は相関閾値と比較され、相関閾値以下になるとUW検出ビット位置であると判断する。

4相PSK (Phase Shift Keying)変調—同期検波方式を用いたTDMAシステムは、再生搬送波の位相不確定性 (Phase Ambiguity)を受信側で除去する必要がある (5)。受信側での位相不確定性除去方法として、バースト信号の搬送波再生部にて絶対位相の確定を行う方法 (6)(7)とUWパターンを利用する方法 (8)の2つが考えられる。ここでは前者を対象とし、再生搬送波の位相不確定性は復調器にて除去されているものとする。

図3.1 バースト構成とUW検出パルス例

図 3.2 UW検出器

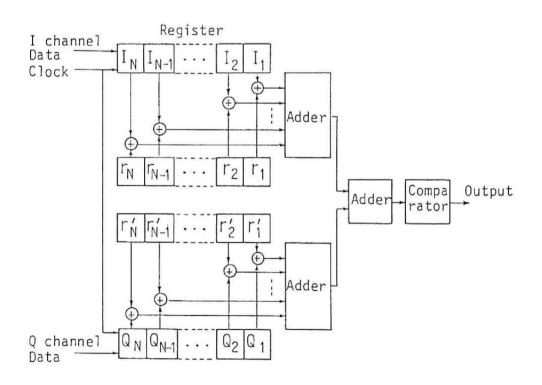

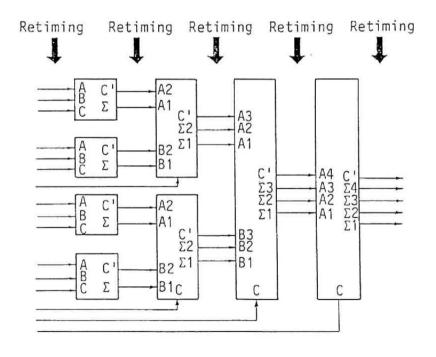

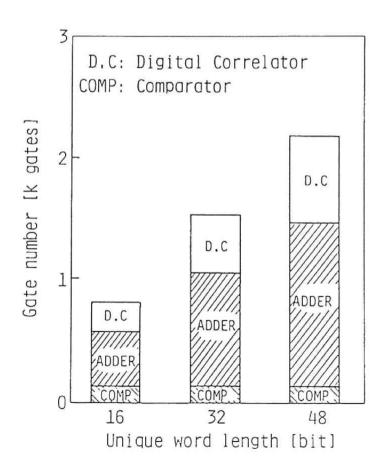

次にUW検出器の構成とハードウェア量について定量的評価を行う。まず図3.2に示すUW検出器のハードウエア量を積算するためUW検出器をディジタル相関部,アダー部,コンパレータ部に分割して検討する。ディジタル相関部及びアダー部(16ビット長)の構成例を図3.3.1及び図3.3.2に示す。ハードウェア量を積算する場合の基本となるゲート数は2入力NAND(NOR)を1ゲートとして換算を行う。またフルアダー及びコンパレータは各々TTL論理素子である74183(1ビットフルアダー),7482(2ビットフルアダー),7488(4ビットコンパレータ)等を基本にゲート数の算出を行う。また各基本ブロックのゲート数を表3.1のように仮定した。

一方、UW検出器はTDMA装置の中で同期精度を決定する重要な役割を果たすため、極力高速動作が要求される。この場合ハードウェアをTTL、CMOS論理素子等で構成する場合、論理素子の伝搬遅延が問題となる。本UW検出回路を高速に動作させる場合に最も厳しい部分はアダー部である。そのためアダー部では各フルアダーの入出力信号をDフリップフロップでリタイミングすることとしてハードウェア量を算出する。以上の条件からUW長が16、32、48ビットの場合についてUW検出回路のゲート数を算出した(図3、4参照)。同図よりUW長に比例してゲート数が増大し、UW長を48ビットとした場合には16ビットの場合の約3倍のゲート数が必要となる。

·図 3.3.1 ディジタル相関部

図 3.3.2 16ビットアダー部

表 3.1 基本ブロックのゲート数

|                | DFF | EXOR | l bit<br>FA | 2 bits<br>FA | 3 bits<br>FA | 4 bits.<br>FA |

|----------------|-----|------|-------------|--------------|--------------|---------------|

| Gate<br>Number | 6   | 3    | 13          | 24           | 35           | 43            |

DFF: D Flip Flop EXOR: Exclusive OR FA: Full Adder

図 3.4 UW検出器のゲート数

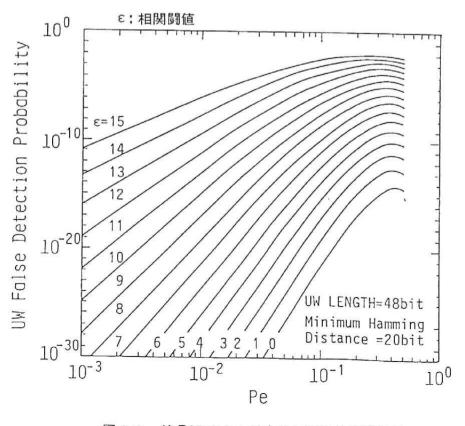

#### 3. 2. 2 不検出·誤検出特性

TDMA方式におけるバースト信号の喪失はUWの不検出または誤検出によって生ずる。UW不検出という事象は、正常にバースト信号が受信され復調されたにも関わらず、UW検出ができずにワード同期が確立されず、バースト信号の喪失を生ずることを言う。またUW誤検出という事象は正常にバースト信号が受信され復調されたにも関わらず、誤ったタイミングでUW検出を行ってしまい、ワード同期が確立されず、バースト信号の喪失を生ずることを言う。そこでこれら不検出率と誤検出率を所望する値以下にするだけのUW長およびUWパターンの選定が必要となる。

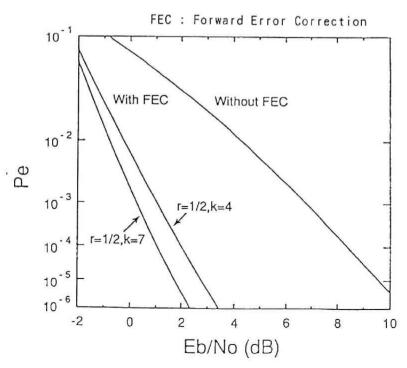

不検出率、誤検出率の最悪値を算出するにはUW部における限界符号誤り率について規定する必要がある。一般に、衛星通信用TDMA方式では回線品質の改善を図るためプリアンブル部を除くデータ部に誤り訂正符号が適用されており、誤り訂正後の限界符号誤り率としては通常 pe-1 x 10<sup>-4</sup>が用いられている。従って、誤り訂正が施されていないUW部では適用する誤り訂正方式に応じて限界符号誤り率が異なってくる<sup>(9)</sup>。図3.5に示す如く符号化率r=1/2,拘束長k=4の畳込み符号化・ビタビ復号法を用いる場合とr=1/2,k=7の畳込み符号化・ビタビ復号法の場合ではUW部における限界符号誤り率は異なり、強力な誤り訂正を適用するTDMAシステムほどUW検出特性に要求される条件は厳しくなる。例えば符号化率r=1/2,拘束長k=4の畳込み符号化・ビタビ復号法を用いるシステムではUW部における符号誤り率は理論値として pe = 4 x 10<sup>-2</sup> となる。

図3.5 誤り訂正符号を用いた場合の符号誤り率特性

従来から、UWの検出率、不検出率に関しては、テレメトリの分野で研究されており、 それらの確率は次式で与えられる(1º)。

但し q<sub>e</sub>=1-p<sub>e</sub>, N:UW長, ε:相関閾値

一方、UWの誤検出率に対しては大きく分けて2つの場合が考えられる。1つはランダムビット中で誤検出を生ずる場合と、固定パターンとオーバーラップして誤検出を生ずる場合である。ランダムビット中での誤検出率Fは次式で表される。

$$F = \frac{1}{2^{N}} \sum_{i=0}^{\varepsilon} {N \choose i}$$

(3-3)

固定パターンとオーバーラップした部分での誤検出率を低下するためには、UWパターンの自己相関と相互相関を検討する必要がある。基準同期バーストのUWを検出する受信フレーム同期の確立時には他のバースト信号との相互相関が問題となり、受信フレーム同期が確立した後の定常時では基準局から指定されたバースト信号のみ、既知のタイミングで受信することから自己相関が問題となる。相互相関は自己相関の延長上にあるため、自己相関について以下詳細に検討する。

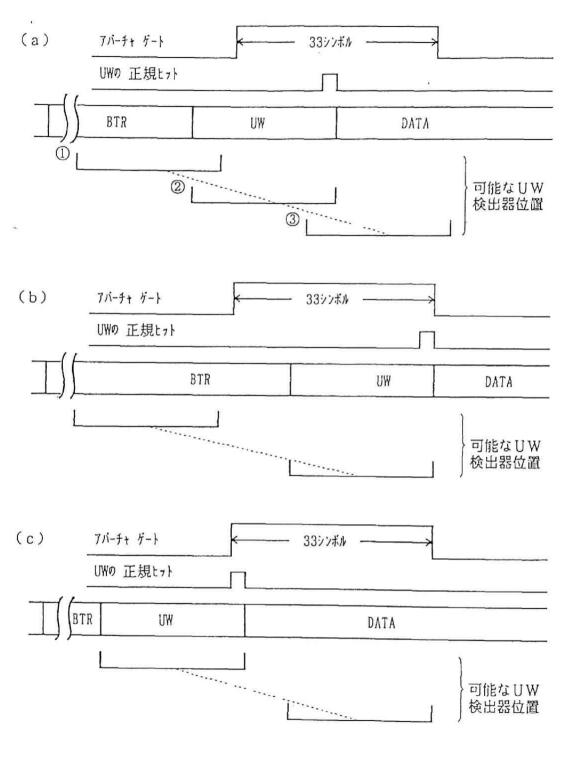

受信フレーム同期が定常状態に達したときには、誤検出率を低くするためUW検出パルスに対してアパーチャ・ゲート信号を設ける。アパーチャ・ゲート信号はバースト信号のガードタイムを考慮してゲート幅が定めれられる。受信フレーム同期確立後のUW検出パルスとアパーチャ・ゲートとのタイミング関係は図3.6に示すように3つの場合が考えられる。また図中、アパーチャ内にあって有効なるUW検出器位置も同時に示す。

図3 6 UW検出位置

図3.6(a)の有効なるUW検出器位置において誤検出の生ずるのは①~②の区間(固定パターンのみの部分)と②~③の区間(固定パターンとランダムパターンの部分)に分けられる。

まず図3.6(a)の①~②区間中における誤検出率は次式で与えられる(!!)。

$$H_{-b} = \sum_{i=E_b - \varepsilon}^{E_b} {E_b \choose i} p_e' q_e^{\varepsilon_{b-i}} x \qquad \sum_{j=0}^{\varepsilon - E_b + 1} {N - E_b \choose j} p_e' q_e^{N - \varepsilon_{b-j}}$$

$$(3-4)$$

また②~③区間中における誤検出率は次式で与えられる。

$$H_{+b} = \frac{1}{2^{b}} \sum_{i=E_{b}-\epsilon}^{E_{b}} {E \choose i} p_{e}^{i} q_{e}^{E_{b}-i} x \sum_{j=0}^{\epsilon-E_{b}+1} {N-E_{b}-b \choose j}$$

$$x p_{e}^{j} q_{e}^{N-\epsilon b-b-j} x \sum_{k=E_{b}+b-\epsilon-i+j}^{b} {b \choose k}$$

$$(3-5)$$

但し E。: 各UW検出器位置におけるUWパターンとの不一致数 (ハミング距離)

N: UW長

上式で示すアパーチャ内での誤検出率は不検出率とともに考えなければならない。すなわち図3.6(a)のノミナル位置にUWがある場合、誤検出が生ずるのはUW検出器位置が①~②の場合と、ユニークワードの不検出が生じてかつUW検出器位置が②~③の領域で誤検出する場合である。従って、後者の場合は不検出率と誤検出率の結合事象となるため誤検出率は無視できることになる。以上のことからアパーチャ内における誤検出率に対して最も厳しいのは図3.6(b)の場合である。従って誤検出率の評価を行うに際し、最悪値評価を行う方法をとると、図3.6(b)の場合を今後検討すれば良いことになる。

これまで各シンボル位置での誤検出率を導出してきたが、アパーチャ内における総合の 誤検出率 H。は、上述の条件を入れると下式で与えられる。

$$-\omega$$

$-b=-1$

$-b=-1$

$-\omega$

(3-6)

但し  $\omega = 16$  シンボル

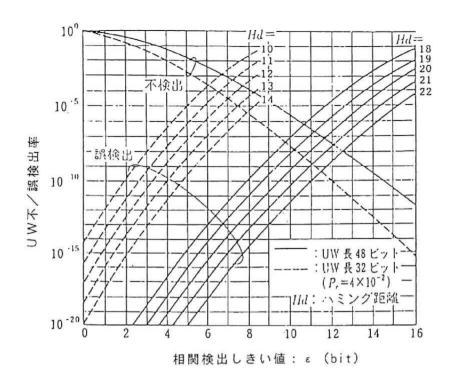

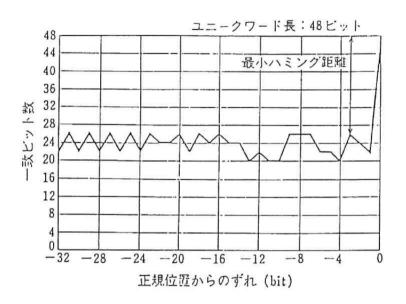

#### 3.2.3 同期語長

UWはTDMAシステムにおける同期系で重要な位置を占めるが、情報伝送の効率という点からはUW長は短い程好ましい。一方TDMA装置のハードウェア構成上からいってUW長は8シンボルの整数倍(バイト単位)となることが好ましい。一般にUW長を長く取ればとるほど相関閾値を適当にとると不検出率、誤検出率の双方を低くすることができる。従って所望する不検出率、誤検出率を満足する最小のUW長を求めることが必要である。

ここで、所望するバースト喪失確率を限界符号誤り率(p。=1×10<sup>-4</sup>)に対して無視できる10<sup>-7</sup>程度以下とする場合の不検出、誤検出率について検討を行うこととする。まず16シンボル(32ビット)にした時の不検出、誤検出率を図3.7に示す。誤検出率はハミング距離をパラメータにしている。図3.7で示されるようにハミング距離が1つ異なると10倍程度、誤検出率が異なる。従って(3-6)式で示されるアパーチャ内の総合誤検出率はほとんどアパーチャ内で最小ハミング距離をもつUW検出位置での誤検出率で支配される。この場合に16シンボルのUWパターンをうまく選定できたとしても通常、最小ハミング距離は12ビット程度しかとれない。従って不検出率、誤検出率の双方を最小にするε=7の時であっても不検出率、誤検出率は10<sup>-5</sup>程度しかとれないため要求条件を満足しない。ゆえに16シンボル以下のUW長では不足する。

次に 2 4 シンボル ( 4 8 ビット) の場合について同様に図 3 . 7 に示す。後述するように、 2 4 シンボルのUWパターンの中で、最小ハミング距離を 2 2 ビットとするものが得られ、 $\varepsilon=1$  2 において不検出、誤検出とも $10^{-7}$ 以下にできる。

以上で要求条件を満足する必要最小限のUW長が24シンボル (48ビット) と定まったので、不検出率、誤検出率と符号誤り率の関係が計算でき、図3.8、3.9に計算結果を示す。図中のパラメータは相関閾値である。

図3 7 UW不検出率及び誤検出率特性

図 3.8 符号誤り率に対する UW不検出率特性

図 3.9 符号誤り率に対する UW 誤検出率特性

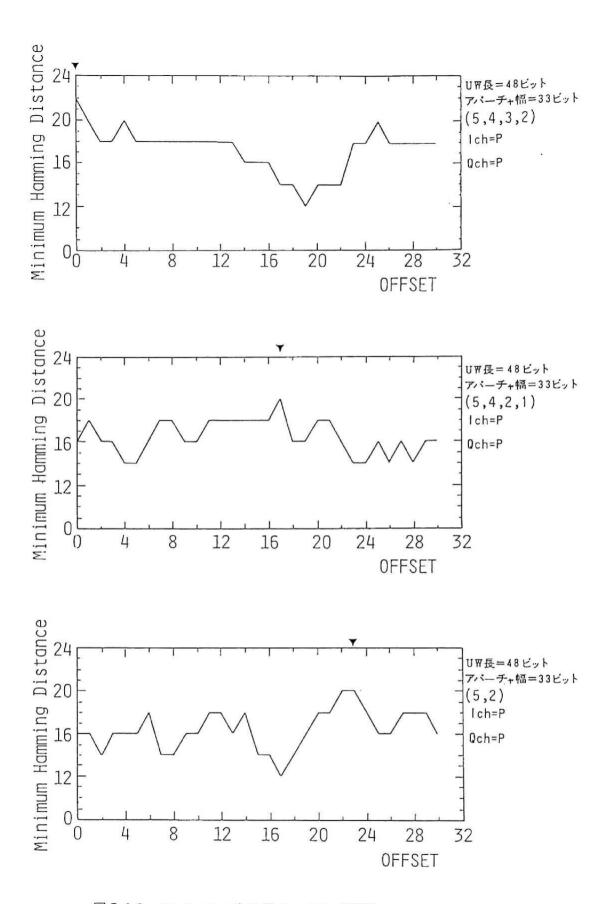

#### 3. 2. 4 同期語パターン(12)

UW検出器を実用化する場合にはUWパターンを決定することが不可欠である。ところがこれまでUWパターンの体系的な構成法は明らかにされていない。従って24シンボルのパターンに対して I、Qチャネルとも同じパターンを入力するとして2²4通りの中から最適なものを選ぶ必要がある。2²4通りものパターンを大型計算機により最適解を求めるという方法も考えられるが、ここでは自己相関特性に優れたM系列の擬似ランダム符号の中から最適なものを選ぶこととする。

M系列は、その繰り返し周期に応じて生成関数の次数が定まる。24ビットのパターン 長より長い次数として5次以上のものが必要になる。5次M系列の生成関数としては、次 の3つがある。

$$\begin{cases} F_1 = X^5 + X^4 + X^3 + X^2 \\ F_2 = X^5 + X^4 + X^2 + X \\ F_3 = X^5 + X^2 \end{cases}$$

(3-7)

5次M系列の周期は31ビットであるため、24ビットのUWパターンを定めるには先頭から取り出す場合を始めとして、31通りの取り出し方がある。先頭から取り出す場合をここではオフセット (Offset) = 0 と定めることにする。

前節で述べたようにアパーチャ内の総合誤検出率日。を支配するのは、アパーチャ内の UW検出位置毎のハミング距離の中で最小となるもの、すなわち最小ハミング距離である。 従って5次M系列(F₁)から取り出したUWパターンをもとにアパーチャ内の最小ハミング距離を導出し、この結果を図3.10に示す。図中、縦軸は最小ハミング距離であり、 横軸はオフセットすなわちUWパターンに対応する。図中▼印で示すようにオフセット= 0の場合が、最も最小ハミング距離を大きくできることがわかる。以下同様にF₂、F₃ の場合についても最適なパターンが定まり、まとめると次表のようになる。

表3.2 5次M系列での最適ユニークワードパターン

| Fı | offset=0  | , | P | Ξ | 1111110010011000010110101 |

|----|-----------|---|---|---|---------------------------|

| F₂ | offset=17 | r | Р | = | 1101010010001011111101100 |

| Fз | offset=23 | , | P | = | 1101100011111100110100100 |

図3.10 アパーチャ内の最小ハミング距離

次に誤検出が生ずるビット位置を考察する。図3.11には、正規のUW検出位置から前の部分で誤検出する場合のUWパターンと固定パターン(クロック再生ビット)との一致ビット数を示している。48ビットと一致ビット数との差がハミング距離となる。従って固定パターンとの一致ビット数が最大の位置が最小ハミング距離を与える点となる。図3.11に見られるように最小ハミング距離を与えるUW検出位置は複数個存在する場合があり、これらの検出位置にて誤検出が生ずる確率が高いことを示している。

図3.11 UWパターンとハミング距離の例

### 3.3 同期語検出特性の改善法

これまで述べてきた方式ではUWは誤り訂正符号化を施されず相関検出されている (7) (8) (10) (12) (13) 。従って所望するUW検出特性を得るには、データ信号部に適用する誤り訂正方式が高利得となるにつれ、UWビット長を大きくする必要があり、結果としてUW検出器のハードウエア量が増大する傾向にある。

本節では、誤り訂正復号器での同期及びバースト誤りの問題を解決することにより、UWビットパターンにも誤り訂正を施しいか、軟判定ビタビ復号後にUW検出を行う方法を新たに提案する。これによりUW検出特性を改善することができUW長の短縮化が可能となることからUW検出器のハードウエアを削減することができる。

# 3. 3. 1 符号化UW検出法(14)(15)

従来のUW検出法では、UW検出器は誤り訂正前の悪い符号誤り率で動作しなけれならず、r=1/2, k=4の畳み込み符号化3ビット軟判定ビタビ復号法を用いる場合には、48ビット以上のUW長が必要である。そこで所要UW長を短くする方法として、UW部分に誤り訂正を施す誤り訂正符号化UW検出法を提案する。本UW検出法を採用すれば、UW部分の符号誤りは誤り訂正後の符号誤り率とほぼ等しくなり、UW検出率特性を改善させることが期待できる。その結果所望するUW検出率を達成するために必要なUW長を短くでき、UW検出器のハードウェアを大幅に削減できる。このような特徴を有する符号化UW検出法を実現する場合に解決すべき問題点は次の2点である。

- 1) ビタビ復号器をバースト動作させるためのゲート信号供給タイミングの生成。

- 2) バースト的なビタビ復号器出力データ符号誤りパターンによるUW検出率特性劣化の軽減。

従来方式ではUW検出パルスからビタビ復号器をバースト動作させるゲート信号を得ていた。すなわち、このゲート信号をオフ状態とすることにより、ビタビ復号器の入力符号量子化符号則が自然 2 進である時にはパスメモリに"0"を書き込むことが可能である。通常 T D M A 方式で用いられているバースト構成では誤り訂正符号化のなされていないプリアンブル部でゲート信号をオフ状態とし、パスメモリをクリアする。通常プリアンブル部はビタビ復号器のパスメモリ長(本例では 2 0 シンボル)より長いため確実にパスメモ

リをクリア可能である。またデータ部の復号はUW検出パルスにより正確にゲートをオン 状態にでき符号誤り率の劣化を生じない。

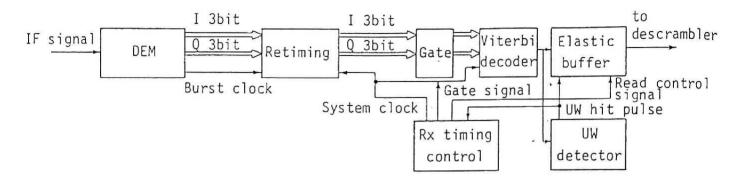

一方、符号化UW検出方式では、誤り訂正されていないプリアンブル部分で確実にパス メモリをクリア可能であるがビタビ復号器に対するゲート信号を受信タイミング制御部よ り供給するため、ゲートをオン状態にする際にガードタイム相当の変動が存在する。そこ で"β"の連続したパターン中であればどのタイミングでビタビ復号を開始しても符号誤 り率を劣化しないという性質を利用し、UW先頭位置に配置された8シンボル長 (ガード タイム相当)の"0"パターン中でビタビ復号器へのゲート信号をオン状態としている。 このような構成となっているためパスメモリは確実にクリアされ、UW先頭位置に配置さ れた"0"パターン中で符号誤りが生じたとしても、その誤りは定常状態と同様にビタビ 復号器で訂正され復号器出力の誤り率に劣化を生じない。この場合のバースト構成を図3. 12に示す(プ。受信側での動作を説明するため符号化UW検出器のTDMA装置内にお ける位置付けを図3.13に示す。送信側ではUW部及びデータ部をたたみ込み符号化し、 他のプリアンブル部と結合してデータバーストを送出する。受信されたデータバーストは 復調器にて4相PSK絶対同期検波され、位相不確定性は除去される。検波出力は Iチャ ネル、Qチャネル双方とも3ビット軟判定され、クロック読み換え回路にてバーストクロ ックからシステムクロックに読み換えられる。システムクロックに読み換えられたデータ はビタビ復号器に入力される。ビタビ復号器へのゲート信号はデータバーストの受信タイ ミングがガードタイム内で変動することからUW部に先行する"0"シンボル部でゲート をオン状態とする。これより、ビタビ復号器をバーストモードで正常に動作させることが 可能となり、ビタビ復号器出力には誤り訂正後のUWパターンが得られる。すなわち誤り 訂正されたUWをUW検出器で検出する構成となっている。

図 3.12 符号化 UWのバースト構成

図3.13 符号化UW検出器を用いたTDMA装置受信部構成

以上述べた図3.12に示すバースト構成の符号化UW検出法は誤り訂正後の符号誤りパターンがランダムである場合には前述の効果が得られる。しかし、ビタビ復号後の符号誤りパターンはバースト的であることが知られており(15)、このままでは符号化UW検出特性を著しく劣化させてしまう。そこでUWを構成する各ビットをクロック再生部にインタリープ配置しバースト誤りに基づくUW不検出率、誤検出率の劣化を低減する。この場合のバースト構成例を図3.14に示す。本バースト構成ではクロック再生部にUWをインタリープしているため、クロック引き込み過程において先頭のUWを検出することになる。この時のクロックジッタが先頭のUWに与える影響を以下に述べる。

図3.14 符号化UWのバースト構成(インタリーブ有り)

入力 C / N = 6 d B に てクロックスリップ率が U W 検出率に影響を与えないという条件から、クロックのタンク(単同調)を Q = 4 0 0 程度とする。この時クロック再生部におけるクロックジッタは入力 C / N とクロック抽出回路 (15) での劣化 6 d B 及びタンクの引き込み特性から導出される。またデータ部ではパターン効果 (17) による劣化 9 d B をさらに加えてクロックジッタを導出する。この結果クロック再生部の引き込みがデータ部の S / N と同程度になるのに要するクロック再生部長は 5 5 シンボルである。従って、図 3 . 1 4 のバースト構成を用いると先頭 U W 部では引き込み過程にあり、クロックジッタは r m s 値で約 8 ° となる。この値は参考文献 (18) で示されているように B T = 0 . 7 の場合でも約 0 . 1 d B の等価 C / N 劣化量であることから、先頭 U W の符号誤り率に対する劣化は無視できるものと考えられる。

#### 3. 3. 2 ビタビ復号後の符号誤りパターン(19)

インタリーブ符号化UW検出法を適用する場合ビタビ復号後の符号誤りパターンが重要となる。従来ビタビ復号後の誤りパターンに対する検討は実験的に符号誤り発生間隔の確率分布を得ることにより符号誤りパターンがバースト的傾向を示すことが報告されているにとどまっている(20)。

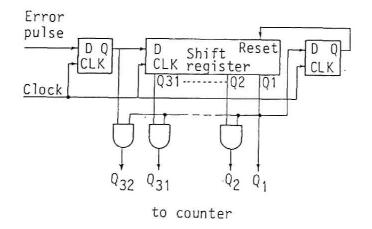

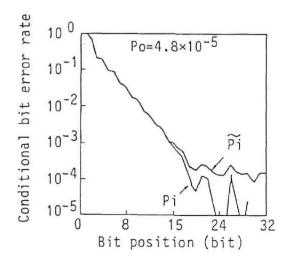

ここではバースト的な符号誤りが生じた場合の各ビット位置での符号誤り率について実験により詳細に検討を行った。実験回路は後述する図3.17を用い、ビタビ復号後の符号誤りパルスを図3.15に示すバースト符号誤り測定回路に入力する。

図3.15 バースト誤りパターン測定回路

ビタビ復号後のバースト誤りの詳細な実験を行うに際しバースト誤りのモデルを仮定する。本モデルの特徴を以下に列挙する。

- (1) バースト誤りが発生した場合 (発生率 $p_o$ ) , 隣接するm ビットまでの条件付符号誤り  $x = y_o$  (i=1, · · · · ,m) は互いに非独立事象である。

- (2) バースト誤りが発生する確率は互いに独立事象である。

- (3) バースト誤りが発生中に次のバースト誤りが発生した時には次のバースト誤りは前のバースト誤りの影響は受けない。

以下の検討ではバースト誤り発生中の多重バースト誤りは2重までとし、3重以上は高次項として無視する。以上の条件から、実験結果から得られる見掛け上の条件付符号誤り率p, (i=1, · · · · , n)は次式で与えられる。

ここで次のような変数変換を行う。

$$\stackrel{\wedge}{p}_{i} - \frac{\stackrel{\wedge}{p}_{i}}{p_{0}}$$

(3-9)

すなわち

٠,..

測定回路のビット数 n を十分大きくとれば p , ( n < i≤m ) は、十分小さいと考えられるため本測定回路により、n ビット目までの条件付符号誤り率が正確に求められる。

nとして本測定回路では32とした。

以上から行列でpiとpiの関係を表記すると下式を得る。

$$\begin{bmatrix} 1 & 0 & 0 & \cdots & 0 & 0 \\ p_0 & 1 & 0 & \cdots & 0 & 0 \\ p_0 & p_0 & 1 & \cdots & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ p_0 & p_0 & p_0 & \cdots & 1 & 0 \\ p_0 & p_0 & p_0 & \cdots & p_0 & 1 \end{bmatrix} \begin{bmatrix} p_1 \\ p_2 \\ p_3 \\ \vdots \\ p_{n-1} \\ \vdots \\ p_n \end{bmatrix}$$

$$\begin{bmatrix} p_1 \\ p_2 \\ p_3 \\ \vdots \\ p_{n-1} \\ \vdots \\ p_{n-1} \\ \vdots \\ p_n \end{bmatrix}$$

$$(3-11)$$

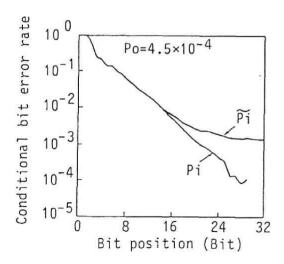

以上からバースト誤りの発生した場合の符号誤りパターンが各ビット位置での条件付確率として得られる。図からバースト誤りの及ぶ長さとして20ビット程度まで延びており条件付符号誤り率は指数関数的に減少することが明らかになった。従って、符号化UWの検出率を向上させるためには、UWのインタリーブ配置が有効であるが、UW部を1ビット単位で20ビット毎にクロック部にインタリーブすることは非現実的であるためここではUWを2ビット毎にグループ化してインタリーブする方法を採用する。

図 3.16.1 ビタビ復号後の条件付ビット 誤り率 (Pe=1.2 × 10<sup>-3</sup>)

図.3.16.2 ビタビ復号後の条件付ビット 誤り率 (Pe=1.2×10<sup>-4</sup>)

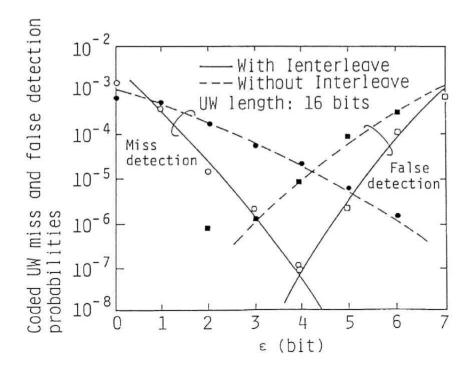

### 3. 3. 3 符号化UW検出特性(21)

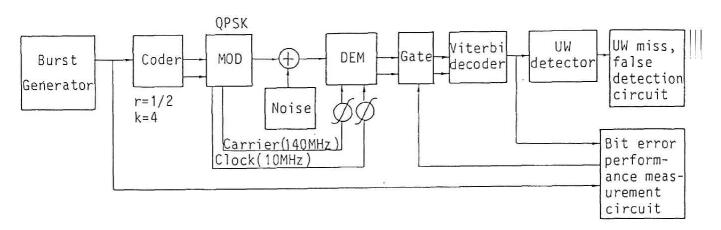

符号化UW検出回路の特性を、図3、17に示す実験回路で評価した。実験回路では、変復調方式としてクロック速度10MHzの4相PSK絶対同期検波方式を用い、図3.12(E。=7)、及び図3.14(E。=8)に示すバースト構成の場合について実験を行った。

図3.17 実験回路

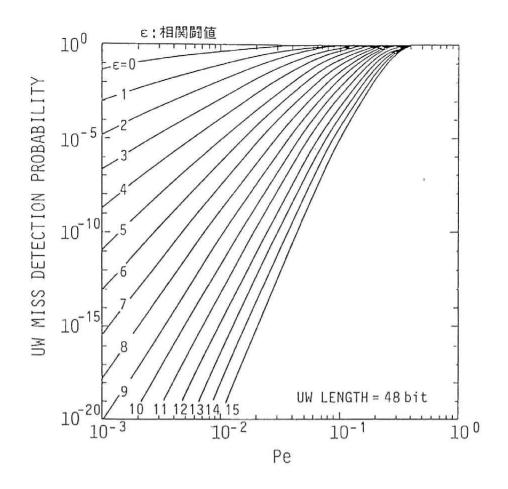

バースト構成に示す 8 シンボル "0"の最後尾位置からビタビゲートを動作させた場合のUW各ビットの符号誤り率特性(インタリーブあり)を図3.18に示す。同図よりUW全ビットにわたり1×10~4以下の符号誤り率特性が得られることが分かる。特に、先頭ビット位置付近では、ビタビ復号器内がクリアされた直後であるためクリア直前のバースト誤りの影響を受けず、定常状態の符号誤り率よりも良くなっている。ビタビゲート信号を8 シンボル"0 "パターンの先頭部で動作させた場合には"0 "パターン中の符号誤りの影響を受けUWの先頭ビット位置でも定常状態の符号誤り率に近づくと思われる。

UW長を16ビットとした符号化UWの不検出率、誤検出率特性を図3.19に示す。 図中、実線はインタリーブ有りの場合であり、破線はインタリーブ無しの場合である。インタリーブ無しの場合はUW内でバースト誤りが発生するため許容誤りビット数に対する改善がビット当たり1/2程度しか無い。一方、インタリーブを行った場合には、バースト誤りの影響が軽減されUW検出率特性が大きく改善されることが分かる。この場合符号化インタリーブUWを用いた場合に許容誤りビット数を4とすれば不検出率、誤検出率共に1×10<sup>-7</sup>程度にすることができる。

図 3.18 ビット位置対符号誤り率特性

図 3.19 符号化 U W 検出率特性

以上から符号化UW検出法を用いることにより従来方式と同程度のUW検出率特性を保 ちつつ、UW長を実質的に48ビットから16ビットに短縮できることが明らかとなった。 これはハードウェア規模で約1/3への削減に対応する。また、インタリーブする間隔を さらに長くとることが可能であれば、符号化UW検出法の特性は一層改善される。

## 3. 4 むすび

本章ではUW検出器の構成について述べ、そのハードウェア量を定量的に評価した。次にUW検出特性について考察を加え、所望するUW検出率を得るためのUW長、UWパターン、相関閾値の設計法を明らかにした。更に低C/N時のユニークワード検出率特性を改善する方法として符号化ユニークワード検出法を提案し、r 1/2、k 4の畳込み符号化3ビット軟判定ビタビ復号法を適用するシステムにおいて従来48ビット必要であったユニークワード長を16ビットに短くし、所望する不検出率、誤検出率を満足できることを示した。この結果、従来のユニークワード検出器で必要であったハードウェア量を約1/3まで削減できる見通しを得た。本章ではr=1/2、k=4の畳込み符号化3ビット軟判定ビタビ復号法の場合を対象として論じたが、他の誤り訂正方式を適用した場合にも同様に用いることが可能である。

### 第4章 複数中継器運用時の同期制御

#### 4. 1まえがき

地球局間の接続性の改善、衛星回線の有効利用、柔軟なネットワークの構築及びシステムの経済化を図るには1つの地球局が複数のトランスポンダにアクセスするトランスポンダホッピングTDMA方式が有効である(1)(2)(3)。このトランスポンダホッピングTDMA方式に用いるTDMA装置を実現するためには同期法、ガードタイム、及びバースト間周波数偏差による符号誤り率劣化が重要な検討課題となる。

従来のトランスポンダホッピング方式では、復調器、周波数変換器が複数必要となる等シングルトランスポンダ運用TDMA装置に比較しハードウェアが大きい構成となっていた。また、従来のトランスポンダホッピング方式ではガードタイムがμ秒オーダと大きく、フレーム効率の観点からはこの低減が望まれる。また1つの復調器で全受信信号を復調する方式としかつDown Converter (D/C) を安価に実現しようとすると、D/Cの安定度が低下し(シングルトランスポンダ運用ではあまり問題とならない)バースト間周波数偏差が大きくなり結果として符号誤り率が劣化する問題があった。

本章では、高利得誤り訂正を採用し、ハードウェアの軽減を図ったトランスポンダホッピング用TDMA装置の構成と特性について述べる。まず、TDMA同期法については基準局ハードウェアを軽減するフレーム構成について検討する。また、トランスポンダホッピング時のガードタイム構成要素を明らかにする。さらにバースト間周波数偏差に対処する方法として記憶型バースト復調器AFC回路を提案し、実験的に特性の評価を行う。

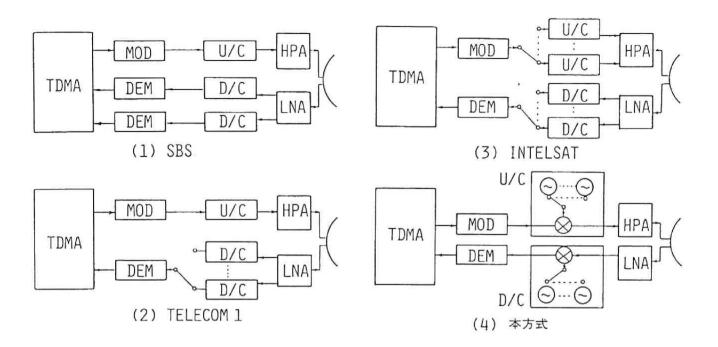

## 4. 2 複数中継器運用・時分割多元接続装置の構成(4)

提案するトランスポンダホッピング用TDMA方式の概念図を図4.1に示す。また、従来のトランスポンダホッピング方式と本方式の主要諸元及びハードウェア比較を表4. 1及び図4.2に示す。SBSシステム(5)では複数の周波数変換器、復調器を用いる構成となっている。INTELSAT TDMA/DSIシステム(6)及びTELECOM 1システム(7)ではIFスイッチを導入し復調器を1台としているが周波数変換器は複数 個用いる構成となっている。

一方本提案方式では周波数変換器、変復調器、TDMA装置まで含めた一系統の送受信装置によるトランスポンダホッピング用地球局装置とすることにより基準局、従局ともハ

ードウェア量が削減されている<sup>(3)</sup>。またガードタイムは地球局周波数変換部の経路長差がないことからその低減が図られる。

一方バースト間周波数偏差への対処法として従来次の方法がとられていた。

SBS:トランスポンダ対応で復調器を設ける方法

TELECOM1:遅延検波を用いる方法

INTELSAT:地球局周波数変換器のローカル周波数をトランスポンダ対応で調整する方法

これらの方法ではそれぞれハードウェア規模が大きい、誤り訂正能力が劣る、及び保守が 複雑となる等に問題があった。

これらの問題を解決するためには、衛星及び地球局周波数変換器の安定度を改善する方法及び復調器で対処する方法がある。本提案方式では復調器AFC回路の機能向上により、大きなバースト間周波数偏差への対処を可能としている。

図 4.1 トランスポンダホッピング方式

図4.2 トランスポンダホッピング用ハードウェアの比較

表 4. 1 トランスポンダホッピング方式の主要諸元

| システム名                | ホッヒング方式 | ホッピング<br>トランスポンダ<br>数 | ホッピング 用<br>ハードウェア               | ガードタイム<br>μ sec<br>( シンボル) | 誤り訂正<br>方式                             | クロック<br>(MHz) |

|----------------------|---------|-----------------------|---------------------------------|----------------------------|----------------------------------------|---------------|

| SBS                  | 受信      | 4                     | D/C × 4<br>DEM × 4              | 0.3                        | 無し                                     | 24            |

| TELECOMI             | 受信      | 5                     | D/C × 5                         | 1. 3 (32)                  | 無し                                     | 25            |

| INTELSAT<br>TDMA/DSI | 送受信     | 4                     | U/C × 4<br>D/C × 4              | 1.1 (64)                   | r=7/8<br>(BCH)                         | 60            |

| 提案方式                 | 送受信     | 7                     | U/C × 1<br>D/C × 1<br>(Local複数) | 0.3                        | r=1/2, k=<br>4 たたみ 込<br>み符号化<br>Eタビ 復号 | 25            |

# 4. 2. 1 TDMA同期制御法

基準局送受信装置を1系統で実現する本トランスポンダホッピング方式を可能とするため、図4.3に示すフレーム構成を提案する。本フレーム構成の特徴は同期バースト領域をトランスポンダ間で時間的に変位させることにある。このため基準局は全トランスポシダに対して時分割的に送受信可能となる。本フレーム構成を用いたとき、同期法については受信同期、初期アクジション、送信同期とも従来のシングルトランスポンダ運用時と全く同様に行なうことができる。たとえば、トランスポンダ間の同期及び従局への制御情報の伝達は送信ホッピングを用いた基準バーストの送出により行なうことができる。また従局同期バーストの遅延時間測定及び従局同期バースト中の監視情報の取得は受信ホッピングにより行なうことができる。

**図4.3** TDMAフレーム構成

# 4. 2. 2 ガードタイム

トランスポンダホッピング時のガードタイム構成要素を表 4.2 に示す (\*)。シングルトランスポンダ運用時のガードタイムに新たに加わる構成要素としては、信号の経路遅延時間差及びホッピングのための周波数変換器ローカルの切替に伴う時間がある。

本トランスポンダホッピング方式では、周波数変換器、変復調器等を複数個用いる従来の方式と異なり地球局内の経路遅延時間差は生じない。そのため、経路遅延時間差としては図4.4に示す衛星搭載中継器間の経路遅延時間差のみが寄与し、地球局内遅延時間差がある場合と比べ、本方式では経路遅延時間差が小さくなる。

| シングルトランス<br>ポンダ運用時と共<br>通の構成要素 | 地球局—衛星間の距離変化による同期誤差<br>(衛星軌道保持範囲 ±0.05度 | ± 5.8 ns  |

|--------------------------------|-----------------------------------------|-----------|

|                                | 送信クロック周波数誤差による同期誤差                      | ±16.6ns   |

|                                | <b>量</b> 子化誤差                           | ± 40. 0ns |

| トランスポンダホッピング時に加わ<br>る構成要素      | 中継器経路遅延時間差                              | 5 ns      |

|                                | ホッヒング・スイッチ立ち上がり・立ち下がり時間                 | 15 ns     |

|                                | スイッチ切り替えに伴う量子化誤差                        | 40 ns     |

| 合計                             |                                         | 184.8 n   |

表 4. 2 ガードタイム構成要素 (クロック周波数25MHz)

図4. 4 中継器経路遅延時間差(FI基準)

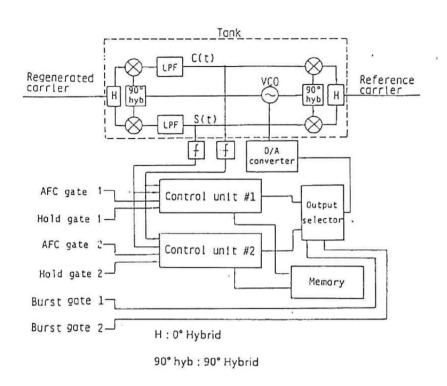

#### 4. 3 記憶型バースト復調器AFC回路(9)(10)

トランスポンダホッピング方式においては、シングルトランスポンダ運用時にバースト間周波数偏差を生じる送信周波数変換器に加えて受信周波数変換器及び衛星上周波数変換器がバースト間周波数偏差を増加させる要因となる。このため安価な周波数変換器を適用する場合には大きなバースト間周波数偏差を生じ、平均値AFC(Automatic Frequency Control)機能を有する通常のバースト復調器では再生キャリア位相誤差が大きくなり符号誤り率が劣化する。 トランスポンダホッピング方式におけるバースト間周波数偏差への対処法としては、周波数変換器の側で対処する方法及び復調器の側で対処する方法がある。従来の対処法のうち、前者としてはローカル周波数をトランスポンダ対応で調整する方法(5)があり、後者にはトランスポンダ対応で復調器を設ける方法(5)及び遅延検波を用いる方法(7)がある。これら従来の方法はいずれも各々保守性、経済性及び性能の点で改善の余地があった。

これらの点を改善するためにはバースト毎の周波数誤差情報を記憶することによりバースト間周波数偏差に追従する記憶型AFC回路が有効である。従来記憶型AFC回路としては準同期検波後ベースバンドでキャリア再生を行う方法(\*\*)及び逆変調キャリア再生方式等で用いられるタンクの入出力間の位相差から周波数誤差を検出しサンプルホールドする方法(\*\*)が提案されている。前者はハードウェア実現上の問題から高速なバースト復調器への適用が難しい。一方、後者は周波数誤差情報の記憶にアナログのサンプルホールド回路を用いるため多数のバーストに対応するためにはハードウェアが大きくなる難点があった。これに対し、逆変調等により得られる抽出搬送波とVCOとのビート信号から周波数誤差情報を取り出すことによりバースト間周波数偏差の平均値に追従する追尾型フィルタ(\*\*)が報告されている。この追尾型フィルタはAFC情報を低速信号に変換してディジタル処理する特徴を持つ。

本節ではこの追尾型フィルタの特徴を活かし、バースト毎の周波数誤差をディジタル的に記憶することによりバースト間周波数偏差に瞬時に追従する記憶型バースト復調器AFC回路を提案し、実験的に特性の評価を行う。本AFC回路の第一の特長は、ディジタル処理部がバーストの周波数誤差程度の速度で動作すればよいため、高速バースト信号に対してもバースト毎のAFC回路として十分動作できることである。第二の特長はディジタル処理型であることからフィルタ定数の切り替えが容易であること、LSI化による小型化に適していること、調整箇所が少ないこと等の利点を有することである。

本AFC回路の性能目標値を表 4.3に示す。同表よりわかるようにバースト間周波数 偏差が 50kHzと大きく、従来のAFC及び単一復調器を用いる方式では目標値を満足できないことがわかる (14)。以下記憶型AFC回路の構成と制御動作について検討する。

最大バースト間周波数50 kHz (p-p) 以下共通周波数偏差±1 MHz低 C / N 限界5 dB許容符号誤り率劣化<br/>(再生キャリア位相誤差)0.3 dB (Pe = 1×10<sup>-4</sup>)<br/>(±2°)

表 4.3 AFC回路の性能目標値

### 4.3.1.回路構成と記憶型動作

提案するAFC回路の構成を図4.5に示す。本AFC方式は復調器キャリア再生タンクに適用するものである。このタンクでは逆変調、4逓倍等によって得られる抽出搬送波を入力とし、同期検波に用いる再生搬送波を出力とする。本AFC回路はタンク部、コンパレータ、制御部、記憶回路、出力セレクタ及びD/A変換器から構成される。

タンク部はその中心周波数をVCO(Voltage Controlled Oscillator)で任意に設定できる周波数追従型となっている。入力した抽出搬送波は一旦周波数変換され2つの互いに直交するビート信号(C(t)、S(t))となり低域通過フィルタによりろ波される。ろ波されたビート信号は再び周波数変換され再生搬送波となる。本タンクのバースト間周波数偏差への追従はタンクの中心周波数を個別バースト対応で制御することにより行う。コンパレータはタンク部内の互いに直交するビート信号を二値量子化しディジタル信号に変換する機能を有する。

制御部は二値量子化された(C(t)、S(t))から周波数誤差を検出、積分する機能を有するとともに誤差情報の記憶機能を有する。

制御部の記憶機能を用いた個別バースト周波数への追従動作は以下のようである。バースト毎に検出された誤差情報は制御部内で蓄積される。制御部内に蓄積された周波数誤差情報は一旦記憶回路に記憶される。次のフレームにおいて記憶された情報は該当バーストが到達する直前に記憶回路から制御部内に書き込まれ、VCOを制御してタンクの中心周波数をバースト周波数の近傍に設定する。

本AFC回路ではバースト毎のタンク中心周波数の切り替えがガードタイム内に行われる必要がある。このため制御部を2系統設け出力セレクタで切り替えることにより、一方がVCOの制御を行う間に他方がメモリ回路とのアクセスを行う構成としている。

図4.5 記憶型バースト復調器AFC回路の構成

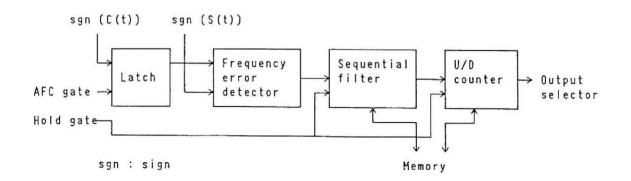

### 4.3.2 制御部動作

制御部は図4.6に示すようにラッチ、周波数誤差検出器、シーケンシャルフィルタ及びU/D(アップ/ダウン)カウンタから構成される。

図4.6 制御部の構成

#### (1) 周波数誤差制御(13)

制御部の動作は以下のようになる。前述のように、抽出搬送波はタンク部内VCO出力により周波数変換されビート信号(C(t)、S(t))を生じる。

$$C(t) = \cos (2\pi\Delta f t) \qquad (4-1)$$

$S(t) = sin(2\pi\Delta ft)$

但し  $\Delta f = f_{reg} - f_{vco}$

freg:抽出搬送波周波数

fvco: VCO周波数

C(t) 及びS(t) はコンパレータにより2値量子化される。ここでC(t) の正エッジにおけるS(t) の正負は Δfの極性により一意的に定まる。このことから、周波数誤差検出器内 フリップフロップを用いてC(t) の正エッジにおけるS(t) の符号を検出することにより周波数誤差情報を得る。検出された誤差情報はシーケンシャルフィルタ及びU/Dカウンタで積分された後、D/Aコンバータ及びVCOを制御する。制御フローを図4.7に示す。本AFC回路では残留周波数誤差特性の改善及び引き込み時間の短縮化のためC(t) の負エッジも制御に用いている。なお本AFC回路のバースト動作は図4.6に示すように制御部入力にラッチを設けバースト対応でAFCゲートを開閉することにより行う。周波数誤差情報はAFCゲートの開いている期間に抽出される。

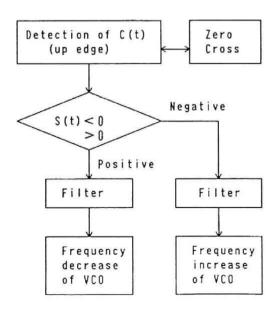

図4.7 AFC制御フロー

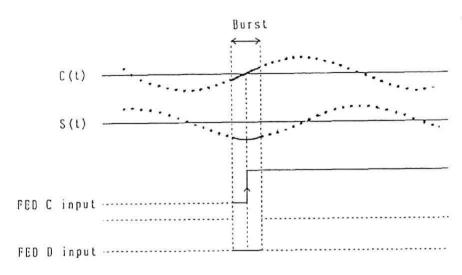

抽出搬送波周波数がVCO周波数よりも高い場合の動作例を図4.8に示す。図中 C(t) 及びS(t) は2値量子化され、制御部内周波数誤差検出回路のC入力及びD入力と なっている。C入力はバースト内において正エッジを生じ、D入力の符号を判定する。こ の判定結果を用いてVCOの周波数を増加させる。

FED: Frequency error detector 図4.8 制御動作の一例

#### (2) 誤制御パターンの除去

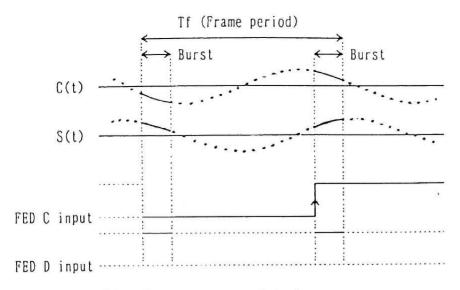

本AFC回路ではAFCゲート内でC(t)が零点を切る時にバーストの周波数誤差検出が行われる。このため、前フレームでのバースト終了時と次フレームでのAFCゲート立ち上がり時のC(t)の符号が異なる場合、ゲート立ち上がり時にC(t)が零点を横切り撥似的な誤差検出動作が起こる。このときに検出されるS(t)の符号はAfの符号とは無関係であるため、検出結果には誤制御パターンが含まれることになる。誤制御パターンの一例を図4.9に示す。本AFC回路では誤制御パターンによる残留周波数誤差特性の劣化を防ぐため、AFCゲート立ち上がり時にシーケンシャルフィルタ及びU/Dカウンタの動作を停止し、誤制御情報を除去する構成としている。

FED: Frequency error detector

図4.9 誤り制御波形

### 4.3.3 実験

AFC回路について評価すべき特性には残留周波数誤差及びバースト引き込み時間がある。残留周波数誤差は復調器の符号誤り率劣化を引き起こすため、その低減が望まれる。 一方、同期バーストの引き込み時間は従局のイニシャルアクジション時間に加わるためこれと比較し十分短いことが望ましい。本章ではこれらの点について実験的に評価を行う。

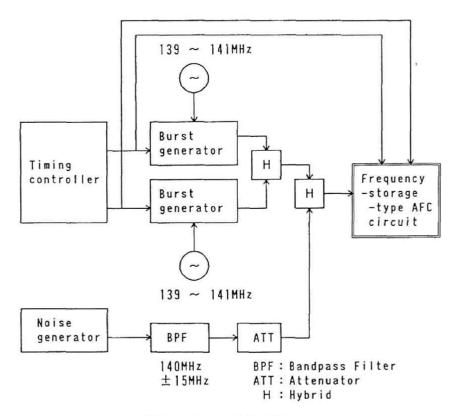

#### (1) 実験回路

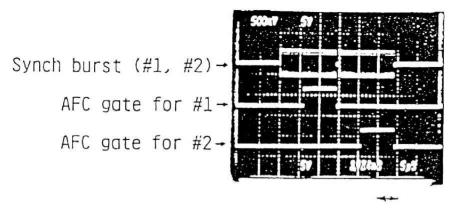

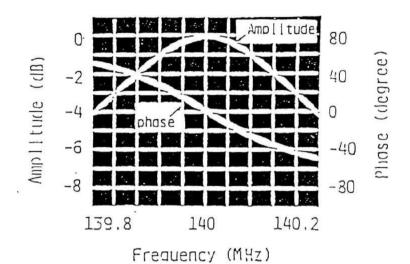

本AFC回路の動作確認を行うため2バーストで実験を行った。実験回路の構成及び主要諸元を図4・10、表4・4に示す。実験では24・5MHzのクロックをもとにフレームを構成し、ガードタイム相当の時間間隔(本例では8シンボル)で接する2個のバーストキャリアを用いて行う。フレーム周期は20msとし、AFC制御情報を抽出するバーストとして長短2種のバースト(データ及び同期バースト(15))について検討する。周波数誤差情報を抽出するAFCゲートはプリアンブル(約6μs)を除いたデータ部分とし検出信号の精度を高めている。2つの同期バーストとそれぞれのAFCゲート信号の関係を図4・11に示す。また、本AFC回路で用いる単同調キャリア再生タンク(3dB帯域幅約400kHz)の振幅位相特性を図4・12に示す。

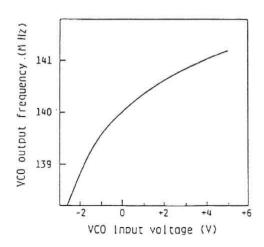

D/A変換器には16ビット、±5 V。- 。(制御間隔 0.15 mV/step ) のものを用い、 ビット数切り替えにより12ビット及び8ビットで動作可能である。VCOの入力電圧と 出力周波数の関係を図4.13に示す。図より、本AFC回路を16ビットで動作させた 時の制御精度は139MHzにて約120Hz/step、141MHzにて約27Hz /stepとなることが導かれる。

図4.10 実験回路

表 4. 4 実験回路の主要諸元

| クロック               | 24.5 MHz                            |  |  |  |

|--------------------|-------------------------------------|--|--|--|

| フレーム周期             | 20 ms                               |  |  |  |

| バースト長              | 14μs (同期バースト相当)<br>59μs (データバースト相当) |  |  |  |

| バースト数              | 2                                   |  |  |  |

| ガードタイム             | 8 シンボル                              |  |  |  |

| タンク3dB帯域幅          | 400 kHz                             |  |  |  |

| シーケンシャル<br>ループフィルタ | AND/NOR フィルタ<br>4 段                 |  |  |  |

| D/A変換器             | 8/12/16 ビット                         |  |  |  |

5μs

図4.11 同期バーストとAFCゲート

12 タンクの振幅位相特性

☑ 4

図4.13 VCOの入出力特性

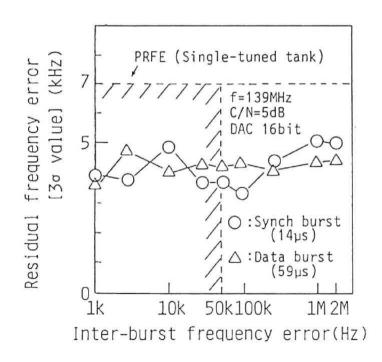

#### (2) 残留周波数誤差特性

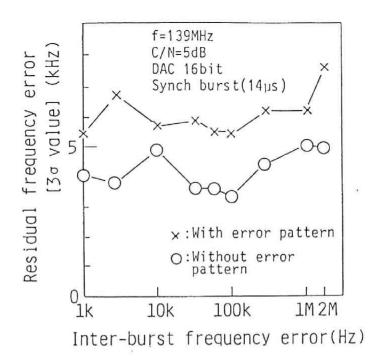

限界C/N=5dBにおいて同期バーストからAFC制御信号を検出する場合の、誤制御パターン除去前と除去後のバースト間周波数偏差と残留周波数誤差(3 α値)の関係を図4.14に示す。本実験時の抽出搬送波周波数を139MHzとし、図4.13よりわかるように高感度の側で評価を行った。本図より、バースト間周波数偏差2MHz以下における誤制御パターン除去前及び除去後の残留周波数誤差は各々約8kHz、約5kHzである。このことから誤制御パターン除去前と比較し除去後は残留周波数誤差が約1/3減少することがわかる。

また図4.14より残留周波数誤差のバースト間周波数偏差に対する依存性はあまり見られない。すなわち本AFC回路が各バースト毎に独立に追従することから回路の特性はバースト間周波数偏差によらないことを示している。

次に誤制御パターン除去後のバースト長に対する残留周波数誤差特性の評価を行う。限界C Z N = 5 d B において同期パースト及びデータバーストから A F C 制御信号を検出する場合の入力バースト間周波数偏差と残留周波数誤差の関係を図 4 . 1 5 に示す。図より同期及びデータバーストに本 A F C 方式を適用した場合バースト間周波数偏差 2 M H z 以下における残留周波数誤差は約 5 k H z となることがわかる。また残留周波数誤差はバースト長に依存しないことがわかる。その理由としては雑音による誤制御が残留周波数誤差変動の原因であり、雑音により A F C 回路の誤制御が起こる確率がバースト長に依存しないためと考えられる。

一方再生キャリア位相誤差による符号誤り率劣化を 0.3 d B 以下とするためには、A F C 回路の許容残留周波数誤差を単同調タンクの場合 7 k H z 以下とする必要がある。図 4.1 5 より、本 A F C 回路はバースト間周波数偏差が要求値である 5 0 k H z を越えて 2 M H z に達する場合にも残留周波数誤差が許容値内におさまることがわかる。したがって周波数変換器により発生するバースト間周波数偏差が 2 M H z まで許容されることから、バースト間周波数偏差 5 0 k H z 時と比較しローカルの周波数安定度をさらに約 2 桁低くすることができる。

DAC: D/A Converter

図4.14 誤制御パターン除去による残留周波数誤差特性の改善

PRFE: Permissible Residual Frequency Error

DAC: D/A Converter

図4.15 残留周波数誤差

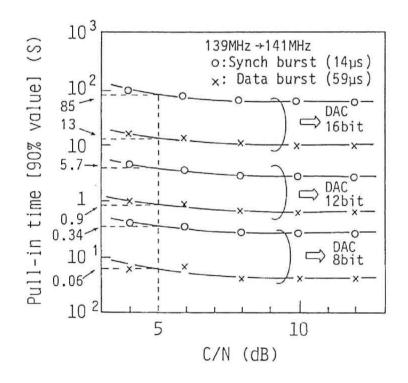

#### (3) 引き込み時間

同期バースト及びデータバーストから制御信号を検出する場合の C/Nに対するバースト引き込み時間 (90%値)を図4.16に示す。図よりC/N=5 d B 時に,同期バーストに対してD/A コンバータを 16 ビット及び 8 ビットで動作させるときの引き込み時間は各々約85 s、約0.34 sである。同期バーストの引き込み時間は従来の初期アクジション時間 5.12 s  $^{(15)}$  に加わるためできるだけ小さくする必要がある。引き込み時間の短縮はD/A コンバータの入力ビット数を上位 8 ビットから 16 ビットへ切り換えることにより実現可能となる。

また、図4.16より同期バーストに比べ6.6倍のAFCゲート長をもつデータバーストからAFC制御信号を検出する場合、C/N=5dBにて引き込み時間は約1/6に減少することがわかる。このことは本AFC回路の引き込み時間が周波数制御情報を抽出する期間であるAFCゲート長に反比例することを示している。

DAC: D/A Converter

図4.16 バースト引込み時間

## 4. 4 むすび

本章では、地球局ハードウェアを軽減するトランスポンダホッピング用TDMA装置について提案し、本構成におけるTDMA同期法、ガードタイム及び復調器AFC回路を検討した。

まず同期法については、基準局1局による管理を可能とするTDMAフレーム構成を提案した。次に、本提案方式のガードタイムを導出し、従来方式に比較し小さいことを示した。最後に、バースド間周波数偏差に追従する高速TDMA用の記憶型バースト復調器AFC回路を提案し、実験的にC/N=5dBにて最大バースト間周波数偏差2MHzまで符号誤り率の劣化を0.3dB以下にできることを示した。さらに本AFC回路のバースト動作時に誤制御パターンが含まれることを指摘しその除去法の検討を行ない、改善効果を実験的に明らかとした。

以上の結果により、1系統の送受信装置でトランスポンダホッピングが可能となり、また本AFC回路を用いれば周波数変換器に周波数安定度の低いローカル発振器を使用でき、地球局装置の経済化が図れる見通しを得た。

#### 第5章 衛星上マスタクロック周波数制御

#### 5.1 まえがき

衛星通信において、伝送容量の増大、地球局の小型化、経済化、周波数の再利用を図るにはマルチスポットビームアンテナを搭載した衛星によるマルチビームTDMA通信方式が有望である(1)。この方式を実現するにはビーム間を接続するためのスイッチを衛星上に設け、所定のビーム間を固定的にあるいはダイナミックに切替え接続する必要がある。接続法にはIF(中間周波数)切替えによる方式とベースバンド切替えによる方式の2種類がある(2)(3)。前者は大容量の中継回線用に主に用いられ、Satellite Switched-TDMA(SS-TDMA)方式と呼ばれる。一方、後者は中小容量の加入者回線用に用いられる衛星上再生中継TDMA方式と呼ばれる。

SS-TDMA及び衛星上再生中継TDMAシステムにおいては、衛星上マスタクロックがIFスイッチや衛星上ベースバンド処理装置に時間基準を与えることから、その高安定化が必須である。またマスタクロックは衛星ネットワークの基準タイミング源となり、その安定性は直接TDMAフレームのガードタイムの長さと地球局において通信信号を伸張/圧縮するバッファのサイズに影響を与えることからも、その高安定化が重要である。

従来、SS-TDMA方式におけるクロックの制御間隔と残留周波数制御誤差に関しては衛星上マスタクロックに地球局のシステムクロックを従属同期させる方法 (4)(5)(衛星上マスタクロックに対して特別なドップラー効果の除去は行なわない)について検討されていた。しかし高安定な地上網クロックに衛星上マスタクロックを従属同期させるための制御間隔については検討されていなかった。本章では衛星上マスタクロックのドップラー効果の影響を除去し高安定な地上網クロックにマスタクロックを周波数同期させる場合に残留周波数誤差を最小化する制御間隔について述べる (5)。

従来、衛星上マスタクロックを制御する方法として以下の方法が提案されている。

- (1) 基準同期バーストに含まれる地上網クロックに位相同期したクロックを衛星上で抽出 しマスタクロックを地上網クロックと位相同期させる方法(\*\*)。

- (2) 地上網クロックに位相同期したクロックにより生成された基準局同期バーストを衛星上にて検出し、正規位置からの誤差情報にもとづいて衛星上マスタクロックを制御する方法(8)

- (3) 基準局にて衛星上マスタクロックと地上網クロックの位相誤差を検出し衛星上マスタ

クロックを周波数同期させる方法 (9) (10) 。

(1)及び(2)の方法はマスタクロック周波数にドップラー効果の影響が加わるためドップラー効果による周波数変動(CS-2号衛星の場合は安定度約3×10-9)以上の高安定化は不可能である。(3)の方法は測定位相誤差からドップラー効果の影響を除去し、高安定なマスタクロックを実現するものである。ドップラー効果除去の方法として次の3方法がある。

- ①衛星が1恒星日を周期とした位置変動を行うことを利用して測定位相誤差を1恒星日で平均化することによりドップラー効果の除去を行う方法(1º)。

- ②衛星と基準局間の測距データを用いて、測定位相誤差からドップラー効果の除去を行う方法(10)。

- ③基準局の送受信フレームが各々逆位相のドップラー効果を受けることを利用して、送信フレームと受信フレームからドップラー効果を除去した位相誤差を得る方法(11)。

以上述べた方法によりドップラー効果の除去を行い,位相誤差測定時の誤差を無限小と仮定して衛星上マスタクロックの周波数を制御する最適アルゴリズムがこれまでに提案されている(\*\*)。このアルゴリズムを用いた制御では主に①の方法によりドップラー効果の除去が行われており,マスタクロックの制御間隔として1恒星日に限定されてしまうという問題があり,制御間隔に関しては検討されていなかった。またこのアルゴリズムによると制御間隔が無限小になれば,マスタクロックの残留周波数誤差も無限小になるが,実際には衛星上マスタクロックと地上網クロックの位相誤差測定時に生じる測定誤差は無視できず測定間隔(制御間隔)の減少とともに測定誤差に起因するマスタクロックの残留周波数誤差は増大する(6)(12)(13)。すなわち最適な制御間隔より小さい制御間隔でマスタクロック周波数を制御すると測定誤差にもとづく誤制御によりマスタクロックの残留周波数誤差が逆に増大するという現象を生じる。

本論文では基本的制御方法として(3) を採用し、ドップラー効果除去の方法として構成が簡易でかつ任意の制御間隔が適用可能な③の方法を採用し、位相誤差測定時に生じる測定誤差の影響を新たに考慮して衛星上マスタクロックの残留周波数誤差を最小化する制御間隔について検討する。

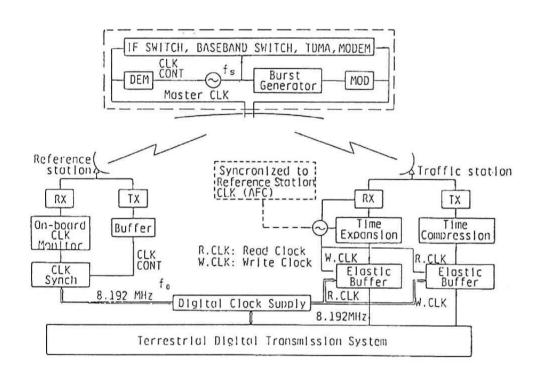

### 5. 2 マスタクロック制御方式

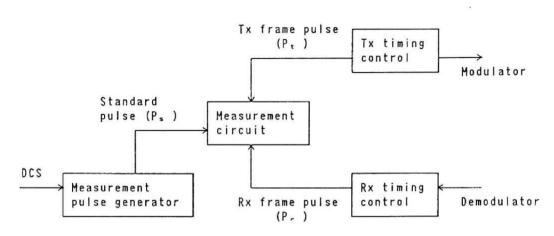

検討対象とするシステムのブロック図を図5.1に示す。まず、基準局は地上網クロックに位置同期したシステムクロックを生成する。この高安定なシステムクロックと衛星上マスタクロックの位相比較を行い、その位相誤差情報からマスタクロック制御情報を生成し、通常の通信チャネルを用いて衛星上に送信し、衛星上マスタクロックを制御する。

本システムでは、衛星の時間基準となる信号(マスタクロック)をTT&C (Telemetry, Tracking & Command)回線又は専用回線等の特別な回線でなく、通常の通信チャネルを介して送信するための変調器を搭載しているが、衛星に本変調器を搭載しない場合でも以下に述べる検討結果は適用可能である。

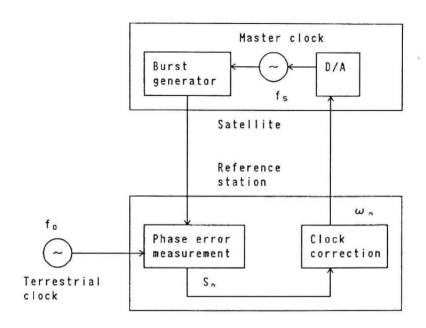

図5.1 ネットワーク同期構成

図5.1に示したネットワーク同期構成のうち、衛星上と基準局に設置されるマスタクロック周波数制御ループを図5.2に示す。この制御ループの動作は以下のとおりである。衛星上バースト発生器ではマスタクロックfs (Hz)をもとに衛星基準バーストを発生する。 基準局ではこの衛星基準バーストを受信し、地上網クロックf。(Hz)との位相誤差測定を行い、正規化位相誤差s。を検出する。この正規化位相誤差量s。をもとに参考文献(10) に述べるアルゴリズムによりマスタクロック周波数制御量 $\omega$ 。を導出する。マスタクロック周波数制御量 $\omega$ 。は衛星上に送信されD / A 変換器に入力され、マスタクロック周波数が補正される。

fo : Nominal clock frequency

fs : Master clock frequency

$\omega_n$ : Correction value  $S_n$ : Phase error

図5.2 マスタクロック周波数制御ループ

以下の節では,まずマスタクロック周波数制御間隔を検討する上で重要なマスタクロック位相誤差測定動作を参考文献(11)にもとづきモデル化を行う。次にマスタクロック周波数制御ループ内で発生する種々の誤差要素に起因したマスタクロックの残留周波数誤差について検討を行う。この検討結果からマスタクロック周波数制御間隔と残留周波数誤差の関係を明らかにし,制御間隔の最小化を図る。

## 5. 2. 1 マスタクロック位相誤差測定

図5.2に示すように基準局においてマスタクロックと地上網クロックの位相誤差測定が行われる。マスタクロック位相誤差測定の回路構成を図5.3に示すいい。この測定法では、地上網クロックから生成された基準フレームパルスP。が基礎となる。この基準フレームパルスと受信フレームパルスP。との時間差T。(s)を測定し、かつ送信フレームパルスP、との時間差T。(s)を測定する。受信フレームパルスは衛星基準バーストを受

信した際のユニークワード検出パルスにより生成される。一方送信フレームパルスは自局 同期バーストと衛星基準バーストの時間関係から正規位置からのずれを検出し送信タイミ ングを補正することにより得られる。すなわち基準局のバースト同期が確立している場合 に得られる送信フレームパルスである。これらT、及びT、をマスタクロック制御間隔T. 毎に測定し、その結果からマスタクロックの位相誤差測定を行う。

DCS: Digital clock supply

図5.3 マスタクロック位相誤差測定回路の構成

以下に正規化位相誤差s。を導出する。

本節以降の検討で用いる記号を以下のように定義する。

fo: ノミナルクロック周波数(Hz)

fs (t): マスタクロック周波数 (Hz)

T: 制御間隔 (s)

$\rho_s(t) = (f_s(t) - f_o)/f_o$ : 時刻t におけるマスタクロックの正規化ドリフト量( $\omega_n = 0$ )

$\rho_n = \frac{1}{T} \int_{t_{n-1}}^{t_n} \rho_s(t) dt$ :時刻 $t_{n-1}$  から $t_n$  における $\rho_s(t)$  の平均値

ρ a(t):時刻t における正規化ドップラーシフト

sta :時刻t における送信位相誤差の測定値(s)

sra :時刻t における受信位相誤差の測定値(s)

ω。 :時刻t における正規化クロック補正値

Ps :地上網クロックにより生成された基準フレームパルス時間位置 (s)

P: 送信フレームカウンタにより生成されたフレームパルス時間位置(s)

Pr :受信フレームカウンタにより生成されたフレームパルス時間位置(s)

$T_t : P_t - P_s (s)$

$T_r : P_r - P_s$  (s)

まずクロック補正値ω。を用いてマスタクロック周波数は次式で与えられる(1°)。

$$f_s(t) = f_o(1 + \rho_s(t) - \omega_n)$$

(5-1)

$SS-TDMA方式では全ての地球局の送信するバースト信号が衛星上においてマスタクロックより生成される IFスイッチ切り替え周期に同期する。従って正規化マスタクロック周波数が (1+ <math>\rho_s(t)$  -  $\omega_n$ ) でドリフトすれば,各地球局の送信タイミングは上り回線でのドップラー効果  $\rho_a(t)$  を打ち消すように (I+  $\rho_s(t)$  -  $\omega_n$  -  $\rho_a(t)$ )にバースト同期する。一方,下り回線は衛星上のタイミングにドップラー効果  $\rho_a(t)$  が相加されるため,各地球局の受信フレームタイミングは (I+  $\rho_s(t)$  -  $\omega_n$  +  $\rho_a(t)$ ) に同期する (14)。

以上のことからt=t<sub>n-1</sub>及びt=t<sub>n</sub>におけるT<sub>r</sub>(T<sub>r</sub>)をそれぞれT'<sub>r</sub>(T'<sub>r</sub>)と定義 すると送信側、受信側のフレームタイミングドリフトに対して次式を得る。

$$T'_{t}-T_{t} = s_{tn} = \int_{t_{n-1}}^{t_{n}} (\rho_{s}(t) - \omega_{n} - \rho_{d}(t)) dt$$

(5 - 2)

$$T'_{r}-T_{r} = s_{rn} = \int_{0}^{t_{n}} (\rho_{s}(t) - \omega_{n} + \rho_{d}(t)) dt \qquad (5-3)$$

従って、両者を平均化した正規化位相誤差s。は次式で与えられる。

$$s_{n} = \frac{s_{\tau n} + s_{\tau n}}{2} = \frac{(T'_{\tau} - T_{\tau}) + (T'_{\tau} - T_{\tau})}{2}$$

$$= \int_{t_{n-1}}^{t_{n}} (\rho_{s}(t) - \omega_{n}) dt \qquad (5-4)$$

上式から明らかなようにマスタクロックの正規化位相誤差s。には、ドップラー効果の影響pa(t)は除去されている。従ってこのs。をもとにマスタクロックを制御することによりマスタクロック周波数の高安定化が可能となる。

# 5. 2. 2 マスタクロック周波数制御ループ(\*)(10)

本節では前節で述べた位相誤差情報s。を用い、マスタクロック周波数制御ループを離散モデル化し、その時の残留周波数誤差について述べる。まず正規化周波数ドリフト $\rho_s(t)$ を離散モデル化するため次式で示す正規化平均周波数ドリフト $\rho_s$ を用いる。

$$\rho_n = \frac{1}{T} \int_{t_{n-1}}^{t_n} \rho_s(t) dt \qquad (5-5)$$

従って (5-4) 式の正規化位相誤差s。は次式となる。

$$s_n T (\rho_n - \omega_n)$$

(5-6)

s。は時間  $t=t_{n-1}\sim t$ 。においてマスタクロックの正規化周波数ドリフト $\rho$ 。と補正値 $\omega$ 。の差(正規化平均残留周波数誤差)を測定間隔T の間積分したものとなる。

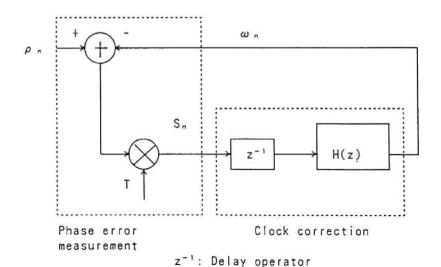

以上からマスタクロック周波数制御ループの離散モデルは図 5. 4 で与えられる。但し、マスタクロック周波数の補正量ω。を算出する最適アルゴリズムH(z)は参考文献(10)により次式で与えられる。

$$H(z) = \frac{2 - z^{-1}}{T(1 - z^{-1})^2}$$

(5 - 7)

図5.4 マスタクロック周波数制御法 (理想モデル)

従って図5. 4 より $t=t_{n-1}\sim t_n$  におけるマスタクロックの正規化平均残留周波数誤差 $\Delta$  の。及び $t=t_{n-1}\sim t_n$  内での動的な正規化残留周波数誤差 $\Delta$  の。は次式で与えられる。

$$\Delta \overline{\omega}_{n} = \rho_{n} - \omega_{n} \qquad (5-8)$$

$$\Delta \omega_n = \rho_s(t) - \omega_n \qquad (5-9)$$

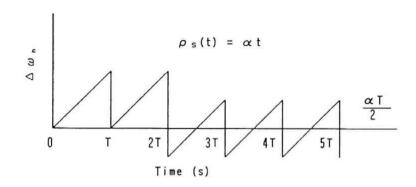

ここでマスタクロック周波数のドリフト例として時間に関して1次近似すれば $\rho_s(t)$ =  $\alpha t$  となり、図 5 . 4 に示す制御ループの応答を示す正規化残留周波数誤差  $\Delta \omega_s$  は図 5 . 5 に示すように変化する。

図5.5 クロック制御ループの応答

## 5. 2. 3 マスタクロック制御誤差

実際のハードウエアでマスタクロック周波数制御ループを構成した場合には図5.4に 示す理想モデルに加え、種々の誤差要因が存在する。これらマスタクロック周波数制御誤 差に影響を与えるものとして次の3点が考えられる。

- (a) VCXOを制御するD/A コンバータの量子化誤差

- (b) マスタクロックと地上網クロックの位相誤差測定時の誤差

- (c) 伝送路上の回線品質劣化

以下ではこの3点について詳細な検討を行う。

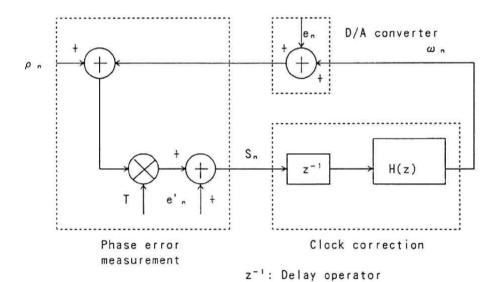

ここで図 5. 4 の理想モデルに(a) 及び(b) の誤差要因e, 及びe',を加えた実モデルを図 5. 6 に示す。

図5.6 マスタクロック周波数制御法 (実モデル)

#### (a) VCXOを制御する D/Aコンバータの量子化誤差

D/A コンバータの量子化誤差をe。とする。e。のマスタクロック正規化残留周波数誤差に対する寄与分 $\delta$   $\omega$  。を算出するため $\rho$  。 e'。=0 とおき、変数s。、e。のZ 変換をS(z)、E(z)で表現すると図 5 . 6 より(5 - 1 0)式が得られる。

$$S(z) = \left\{ \frac{1}{T} \times \left[ 1 + \frac{1}{1 - z^{-1}} \right] \times S(z) \times \frac{1}{1 - z^{-1}} + E(z) \right\} \times (-T)$$

(5 - 1 0)

従ってS(z)は(5-11)式となる。

$$S(z) = -T (1 - z^{-1})^2 E(z)$$

(5 - 1 1)

よって、逆 Z 変換を行うと (5-12) 式を得る。

$$s_n = -T (e_n - 2 e_{n-1} + e_{n-2})$$

(5 - 1 2)

正規化残留周波数誤差  $\delta$   $\omega$  。は正規化位相誤差 s 。を時間で微分すれば得られる。時間 t  $=t_{n-1}\sim t$  。において  $e_n$  , $e_{n-1}$  , $e_{n-2}$  は一定値であるため  $\delta$   $\omega$  。は(5 - 1 3)式となる。

$$\delta \omega_n = -(e_n - 2e_{n-1} + e_{n-2}) \tag{5-13}$$

実際のD/A コンバータ制御では量子化間隔を e とすると、有効桁の丸め込みを行うため D  $\sim e$  の量子化誤差が生じる。これは e/2 をオフセットとして、  $\pm e/2$  の一様分布と考えることができる。従って(5-13)式よりS  $\omega$  。の最悪値として、オフセットがキャンセルされた(5-14)式が得られる

$$|\delta \omega_n| \leq 2e$$

(5-14)

また正規化残留周波数誤差  $\delta$   $\omega$   $\kappa$  の分散  $\sigma_{\delta\omega n}^2$  は  $e_{n-1}$   $e_{n-2}$  が互いに独立事象であることと  $\pm$  e/2 の一様分布であることから次式を得る。

$$\sigma_{\delta\omega n}^2 = e^2/2 \tag{5-15}$$

ここで変調感度をa(Hz/V)、電圧制御範囲 $\pm E(V)$ 、D/A コンバータのビット数をn とすると(5-16)式を得る。

$$e = a \times \frac{E}{2^{n-1}} \times \frac{1}{f_0} \tag{5-16}$$

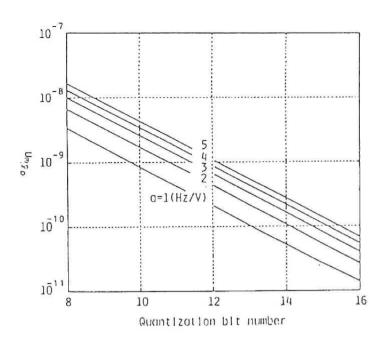

図 5. 7 に  $\pm$  E =  $\pm$  5 (V) として a をパラメータとした  $\sigma_{\delta\omega n}$  の計算結果を示す。本論文では、ドップラー効果で決まる安定度以上の高安定度を目標としていることからドップラー効果  $(3\times10^{-9})$  に対し  $\delta$   $\omega$   $_n$  を無視できる程度に小さくするには 16 ビットの D/A コンバータで十分であることがわかる。

図5.7 D/Aコンバータの量子化誤差の基づく 周波数制御誤差の標準偏差

#### (b) マスタクロックと地上網クロックの位相誤差測定時の誤差

マスタクロック位相差測定誤差e'。のマスタクロック正規化残留周波数誤差に対する寄与分 $\delta$   $\omega'$  。を算出するため、 $\rho$  。=e 。=0とすると正規化位相誤差S(z)は図5 。6 より(5-1 7)式になる。

$$S(z) = S(z) \times \left[1 + \frac{1}{1 - z^{-1}}\right] \times \frac{1}{T} \times \frac{1}{1 - z^{-1}} \times (-T) + E'(z)$$

(5 - 1 7)

よって (5-18) 式を得る。

$$S(z) - (1 - z^{-1})^2 E'(z)$$

(5 - 1 8)

従って逆 Z 変換を行うと (5-19) 式を得る。

$$s_n - e'_n - 2e'_{n-1} + e'_{n-2}$$

(5 - 1 9)

上式でe'。は $t=t_{n-1}\sim t$ 。測定後の位相誤差に寄与する項であることから、 $t=t_{n-1}\sim t$ 。間のマスタクロック正規化残留周波数誤差 $\delta$   $\omega'$ 。に対する位相誤差s'。は次式

となる。

$$s'_{n} = 2 e'_{n-1} + e'_{n-2}$$

(5 - 20)

従ってマスタクロックの正規化残留周波数誤差  $\delta$   $\omega$  '  $_n$ は正規化位相誤差  $\delta$  '  $_n$  を時間で微分すれば得られる。 e'  $_{n-1}$  及び e'  $_{n-2}$  は  $t=t_{n-1}$  ~  $t_n$  において一定値であるため次式を得る。

$$\delta \omega'_{n} = \frac{s'_{n}}{T} \qquad (5-21)$$

すなわちマスタクロック位相差測定誤差にもとづくマスタクロック正規化残留周波数誤差 $\delta$ ω'。は測定間隔Tに逆比例して小さくなることを示している。ここでマスタクロックの正規化位相誤差s'。の標準偏差を評価する。(5-4)式より誤差e'。は次式で与えられる。

$$e'_{n} = \frac{(\Delta T_{\tau}' - \Delta T_{\tau}) + (\Delta T_{r}' - \Delta T_{r})}{2}$$

(5 - 2 2)

但し、 $\Delta T'$  、 $\Delta T_r$  、 $\Delta T_r$  、 $\Delta T_r$  は各々T' 、、 $T_r$  、T' 、、 $T_r$  測定時の誤差である。ここで図 5 . 2 及び図 5 . 3 にもとづき測定誤差 $\Delta T'$  、 $\Delta T_r$  、 $\Delta T_r$  、 $\Delta T_r$  、 $\Delta T_r$  の発生要因とその特性について述べる。

受信側では次の動作によりT'、、Trを測定する。まずマスタクロックをもとに衛星基準パーストが基準パースト発生器により生成される。次にこの衛星基準パーストが基準局にて受信されユニークワード検出が行われる。この時のユニークワード検出パルスは受信パーストクロックからシステムクロックへ乗り換えられ、受信フレームカウンタがリセットされる。最後に受信フレームパルスと基準フレームパルスの時間差T、が位相誤差測定用クロックにより計数される。

従って測定誤差△1', △1、は次の要因より構成される。

- a) マスタクロックの短期安定度にもとづく周波数ドリフト :  $\sigma_1$  (ns)

- b) 搭載基準バースト発生器のロジックジッタ: σ₂ (ns)

- c) 基準局における受信バーストクロックとシステムクロック間の タイミング不確定: ± Br、(ns)

- d) 位相誤差測定クロックの分解能: ±Br<sub>2</sub>(ns)

- e) 受信タイミング測定回路のロジックジッタ: σ a (ns)

他方、送信側では次の動作によりT'、、T、を測定する。まず送信フレームカウンタにも とづき自局同期バーストが送出される。次に衛星基準バーストと衛星折り返し自局同期バ ーストを受信することにより正規位置からのずれを検出して送信フレームカウンタを補正 する。この動作によりバースト同期が維持される。この時送信フレームカウンタより生成 される送信フレームパルスと基準フレームパルスの時間差T、は位相誤差測定用クロックに より計数される。従って、測定誤差ΔT'、、ΔT、は次の要因より構成される。

f) 送信タイミング測定回路のロジックジッタ: σ ₄ (ns)

g) バースト同期制御によるタイミングジッタ: σ 5 (ns)

h) 位相誤差測定クロックの分解能 : ±Br<sub>3</sub> (ns)

各測定誤差要因に関してσ<sub>1</sub> ~ σ<sub>5</sub> はガウス分布、Br<sub>1</sub> ~ Br<sub>3</sub> は一様分布を仮定する。 図 5 . 1 のネットワーク同期構成に示したように、基準局がマスタクロックの周波数誤 差を測定する際にメトリック法 <sup>(1)</sup> を用いず、搭載変調器を用いて直接マスタクロックを 地球局に向け送信することから、従来方式と比較してe'<sub>n</sub> はメトリック法による誤差分だ け小さくなっている。

以上からマスタクロック位相差測定誤差e'。にもとづく正規化位相誤差s'。の分散は次式で与えられる。

$$\sigma_{s,u}^{2} = 5 \left\{ \sum_{i=1}^{5} 2\sigma_{i}^{2} + \frac{1}{3} \sum_{i=1}^{3} 8r_{i}^{2} \right\}$$

(5 - 2 3)

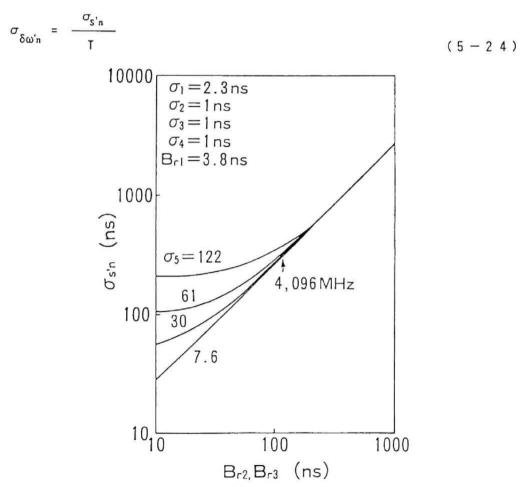

測定クロックと正規化位相誤差s'。の標準偏差 $\sigma_{s'n}$ の関係の典型的な例を図5. 8に示す。

図5. 8 測定クロックの分解能(Br2, Br3) とσ<sub>sn</sub>'の関係

#### (c) 伝送路上の回線品質劣化

伝送路上の回線品質劣化にもとづくマスタクロック周波数制御誤差の要因として次の 2 つがある。

#### ①ユニークワード不・誤検出特性

本論文で採用する位相誤差測定法では基準局における送信フレーム及び受信フレームを刊用する。従って符号誤りによるこれらフレームタイミングを決定するユニークワード検出率の劣化を評価しておく必要がある。一方、一般に衛星通信システムではユニークワードの不検出・誤検出は回線断規格符号誤り率(例えば10-4)において、4相PSK変調絶対同期検波方式を用い、符号化率 r = 1 / 2 , 拘束長 k = 4 のたたみ込み符号化、3 ビット軟判定ビタビ復号方式を用いた場合には、理論E、/N。は約2dB に相当し、4 8 ビットのユニークワード長では10-7程度の不・誤検出率が得られる(15)(16)。従って、この程度の不・誤検出率であれば回線品質劣化が位相誤差測定に与える影響は無視できると考えられる。ただし、1 つの基準局で回線断規格符号誤り率10-4を割るような回線品質劣化を生じた場合には他の基準局へ交替するシステム運用が必要である。

#### ②制御情報伝送の符号誤り特性

基準局にて検出したマスタクロック位相誤差にもとづき算出したマスタクロック周波数制御量ω。は基準局から衛星に向け送信される。この上り回線においても下り回線同様の変復調方式と誤り訂正方式を用いるため、回線断規格符号誤り率10~4は理論E。/N。=2dBに相当する。データ通信においては受信データのエラーフリーを保証するために通常HDLC(High Level Data Link Control)等が用いられており、本方式においても同様な制御手順を用いれば、制御情報伝送上の符号誤り率の影響は無視できる。しかし、①の場合と同様に回線断規格符号誤り率10~4を割るような回線品質劣化を生じた場合には基準局交替によるシステム運用が必要である。

以上から誤差要因として(c)の影響は方式構成上の工夫により無視でき、前述の2項目(a)及び(b)が制御誤差に影響を与えることが分かる。

### 5. 2. 4 最適制御間隔

前節で述べた理由によりマスタクロック位相差測定誤差e'。にもとづく正規化残留周波数誤差 $\delta$   $\omega'$ 。の標準偏差 $\sigma_{\delta\omega'n}$  は制御間隔1/T で小さくなる。一方図5.5に示すように制御間隔Tが大きくなれば、マスタクロックのドリフトによる残留周波数誤差は大きくなる 傾向にある。ここでマスタクロックに使用する水晶振動子の周波数経時変化特性が重要となる。一般に、水晶振動子は水晶振動体に発生した歪が原因となり数百日に及ぶ長期周波数エージング特性を有し、この期間はほぼ1次近似可能な周波数ドリフト特性を示し、その後は水晶振動体への温度変化や電極金属などの水晶振動体への拡散等が支配的となって緩やかな周波数ドリフトを生じることが知られている  $\Box$  ? 。 従ってマスタクロックのドリフトを 1 次近似するモデルの適用範囲は初期の数百日に対して最も有効である。その後の緩やかな周波数ドリフトに対しても短期的にみれば 1 次近似可能であるため、以下の検討ではマスタクロックのドリフトを $\rho_s(t)=\alpha$  t とする。この時のマスタクロック周波数制御ループに線形システムであるため、マスタクロックの総合正規化残留周波数誤差  $\Psi$  (T) は各要素の和で与えられ、次式を得る。

$$\Psi (T) = \frac{\sigma_{S'n}}{T} + \frac{\alpha T}{2}$$

(5 - 2 5)

但し上式では,D/A コンバータの量子化ビット数を16 ビット以上として, $\delta \omega$ 。の影響は無視している。 従って $\Psi$ (T)の極値を与える条件d  $\Psi$ (T)/dT=0より最適制御間隔 T は次式となる。

$$T = \int \frac{2 \sigma_{s'n}}{\alpha}$$

(5 - 2 6)

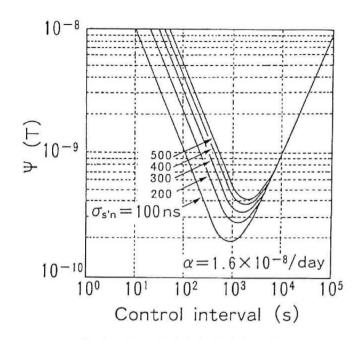

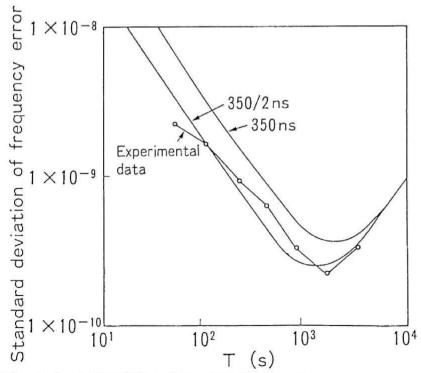

$\sigma_{\text{s'n}}$  をパラメータとし、マスタクロックの初期安定度を $\alpha=1.6 \times 10^{-8}/\text{day}$ とした場合の $\Psi$  (T) を図 5 . 9 に示す。

図5.9より1000~2000秒の点でΨ(T)を最小にする点が与えられる。すなわち本方式による最適制御周期は従来の1 恒星日より1 桁以上小さくなる。また、その時の制御精度は従来方式と比較して1 桁以上向上する。

一方、マスタクロックが数百日に及ぶ長期周波数エージング特性を経た後、緩やかな周

波数ドリフトを生じた場合には、最適制御間隔は図5.9で与えられる値より長くなる。但し、正規化位相誤差の標準偏差を $\sigma_{s'n}$  =300 ns と仮定した場合には、(5-26)式からマスタクロックが $\alpha=7 \times 10^{-12}/{\rm day}$  より安定度の低い範囲内において1恒星日よりも短い周期で制御する必要がある。

図5.9 周波数誤差と制御間隔

## 5.3 実験結果

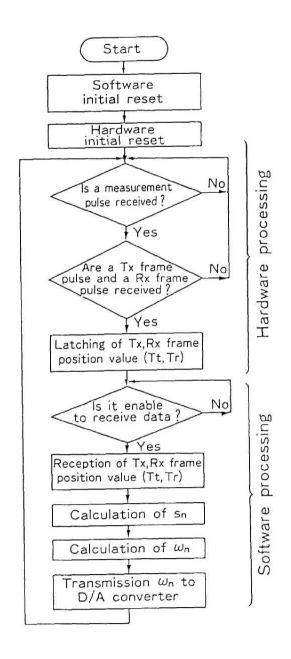

図5.1 に示す衛星上マスタクロック、変調器、基準局SS-TDMA装置及び従局SS-TDMA装置からなるネットワーク同期ループを構成し、マスタクロック周波数制御の実験を行った。基準局におけるマスタクロック周波数制御フローを図5.10に示す。

図5.10 マスタクロック周波数制御フロー

基準局では送受信フレームパルスを利用して、ドップラー効果を除去したマスタクロック 正規化位相誤差sn。を測定し、制御量 $\omega$ nを算出する。実験装置では測定パルスPsの基準発振器として $\pm 3 \times 10^{-2}$ 以下の長期安定度を有するセシウム発振器を用いており、送信フレームパルスPt、、受信フレームパルスPt、とPsの時間間隔は、4.096MHzの測定クロ・ックでハードウェア的に測っている。測定結果は8ビットマイクロプロセッサ6809によってソフトウェア処理され、約1msの処理時間の後に、制御量 $\omega$ nが16ビットD/A コンバータへ 出力される。

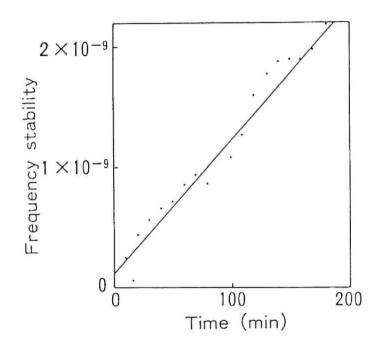

前節で最適制御間隔について述べたように、注目すべき安定度は約十分~数時間のVCX0の安定度である。実験で使用したマスタクロックは恒温槽入りもので図 5.11に示すような初期周波数安定度であり、1次ドリフトと近似すると1.6× $10^{-8}$ /day相当の安定度を有する。

図5.11 VCXOの周波数安定度

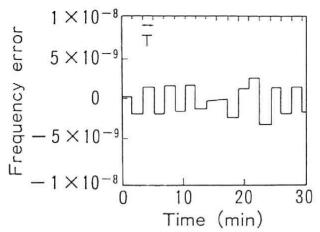

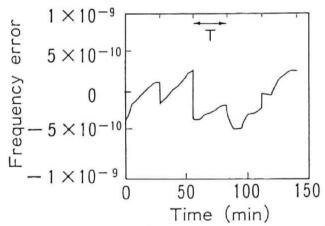

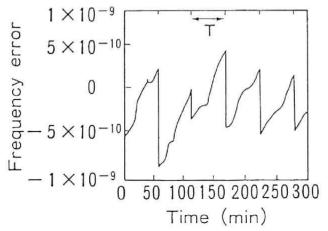

制御周期T=104 秒、1680秒、3360秒とした場合の定常状態におけるマスタクロックドリフト変化量を図5.12、13、14に示す。図5.12より、T=104 秒では測定クロックの分解能による誤差 $\delta$   $\omega$  '。が支配的となり、マスタクロックのドリフトの影響はほとんど見られない。一方、図5.14では $\delta$   $\omega$  '。の影響よりマスタクロックのドリフトの影響が顕者となっている。最適制御間隔付近のT=1680秒ではマスタクロックのドリフトに加え $\delta$   $\omega$  '。の影響もみられる。

図 5 . 12 定常状態でのマスタクロック 周波数誤差 (T=104sec)

図 5 . 13 定常状態でのマスタクロック 周波数誤差 (T=1680sec)

図 5 . 14 定常状態でのマスタクロック 周波数誤差 (T=3360sec)

一方、マスタクロックを制御するD/A コンバータとして16ビットのものを使用し、マスタクロックはa=2.7Hz/v の周波数感度を有するものを使用していることから、D/A コンバータの量子化誤差による正規化残留周波数誤差  $\delta$   $\omega$  の標準偏差は $\sigma$   $\delta \omega m$  は

$$\sigma_{\delta\omega n} = 4 \times 10^{-11} \tag{5-2.7}$$

となり無視できる。

以上から、4.096MHzによるマスタクロックのドリフト測定、16ビットD/A コンバータ、初期周波数安定度1.6 ×10<sup>-8</sup>/dayのマスタクロックという条件では、約1600秒程度の制御間隔が最適であるということを示している。この時には3 ×10<sup>-10</sup> 以下の短期安定度が実現できる。同様の条件にて従来の1 恒星日による制御では、8 ×10<sup>-9</sup>の短期安定度となることから、本制御方式により安定度が1/27に改善されることが分かる。

図5.15 制御周期下に対する周波数誤差の標準偏差(実験値)

## 5. 4 むすび

SS-TDMA方式または衛星上再生中継TDMA方式を実現するために、衛星上に搭載されたマスタクロックを地上の高安定なクロック網に同期させる必要がある。従来の方法では長期的には地上網の安定度10<sup>-11</sup> に同期させることができるが、短期安定度に対する考慮はなされていなかった。

本章では長期的には地上網の安定度10<sup>-11</sup> に同期させ、かつ短期安定度を高めるためマスタクロック制御間隔の最適化について検討を行った。また、実験によって、マスタクロックが初期安定度1.6 ×10<sup>-8</sup>/dayを有する場合には約1600秒の制御間隔で3 ×10<sup>-10</sup> の短期安定度を実現できることを示した。すなわち従来方式と比較し短期安定度を1/27に改善できることを明らかにした。

また本章の方法を用いればマスタクロック周波数安定度が数百日に及ぶ長期周波数エージング特性を経た後、緩やかな周波数ドリフトを生じた場合でも、マスタクロックのドリフト量が $\alpha=7\times10^{-12}/\mathrm{day}$  より安定度の低い範囲内においては1恒星日よりも短い周期で制御する必要がある。

### 第6章 時分割多元接続装置の小型・高信頼化

#### 6.1 まえがき

LSI技術の長足の進歩にともない、各種通信装置のLSI化が多くの機関で進められている。この目的は主として装置の小型化・経済化及び高安定化にある。装置規模が比較的小さい場合にはそのLSI化も容易であり、開発期間も多くを必要としない。一方、複雑な機能を実現する架構成となるような大規模通信装置のLSI化は、多数のLSIで装置としての機能を実現する必要があること及び、仮にLSIが開発されたとしてもメモリ等の汎用LSI又は端末LSI等と異なり、生涯生産数が著しく少ないことから、開発コストに見合う経済性の達成に疑問があり、現在までのところあまりなされていない。

本章では、まず時分割多元接続(TDMA)装置の構成について述べ、そのLSI化手法について検討を行う。次に衛星搭載用TDMA装置の構成法とそのLSI化手法について検討を行う。

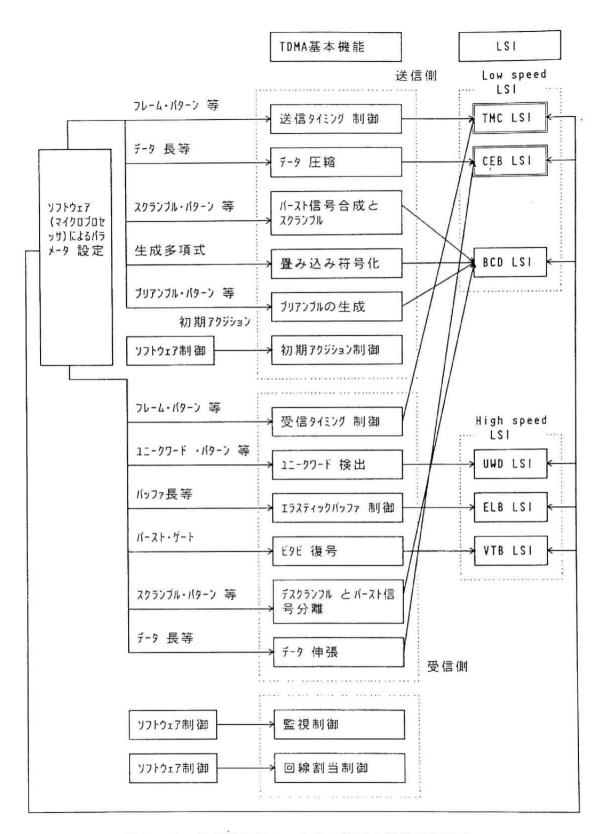

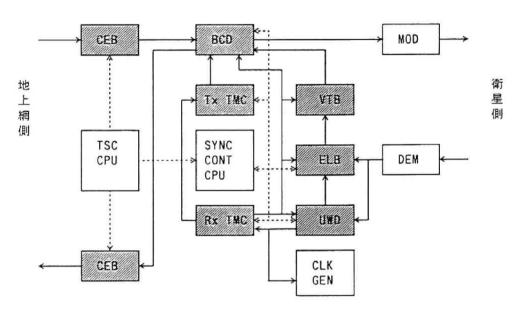

### 6.2 時分割多元接続 (TDMA) 装置構成

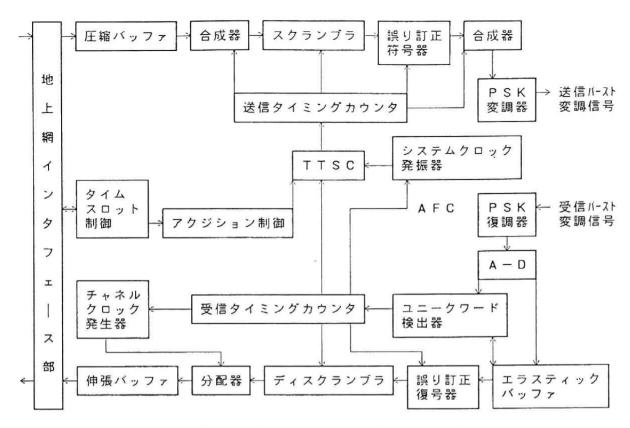

TDMA衛星通信方式は1960年代にその有効性・方式の実現性が確認されて以来、同期制御方式・装置構成法等種々の観点から検討されてきた。TDMA装置の構成例を図6・1に、主要諸元例を表6・1に示す(1)(2)(3)(4)。ここで対象とするTDMA方式はクロック速度25MHzで64kbps回線320chのデマンドアサインシステムである。一般にTDMA装置は変復調部(5)、同期制御部(6)および地上網インタフェース部(7)(8)から構成される。以下の検討は同期制御部を中心に行う。

AFC:自動周波数制御 TTSC:送信タイミング蓄積カウンタ

図6.1 TDMA装置の構成例

表 6. 1 TDMAシステムの主要諸元

| 地球局            | 基準局 : 2 局            |

|----------------|----------------------|

|                | 従局 : 2 1 0 局         |

| 変復調方式          | QPSK一同期検波            |

| 誤り訂正           | 畳み込み符号化─ビタビ復号        |

|                | (符号化率1/2,拘束長4)       |

| クロック速度         | 25. 024MHz           |

| 伝送容量           | 64kbps×320ch/トランスポンダ |

| 地上網<br>インタフェース | 8,192Mbps 局内インタフェース  |

| 回線割当           | チャネル単 位 デマンドアサインメント  |

|                |                      |

## 6. 2. 1 TDMA同期制御部における信号処理概要

#### (1) 送信部信号処理の概略

地上網または端末からの信号は圧縮バッファ (Compression Buffer) により圧縮され、コンバイナ (Combiner) にて制御信号等と合成される。

次にスクランブル・誤り訂正符号化の後、プリアンブルと合成される。合成信号は送信 タイミング制御信号に従い搬送波をバースト変調する。

#### (2) 受信部信号処理の概略

受信QPSK復調された信号は誤り訂正のため、3ビット軟判定(A / D変換)され、あおのMSBビットを用いてユニークワード検出器にてユニークワードを検出する。このユニークワード検出パルスをもとに受信フレーム同期を確立しデータバーストを受信するとともに、エラスティックバッファ(Elastic buffer)にて時間的なゆらぎのあるバーストクロックから高 S / N比のシステムクロックへ受信データを読み替える。次にビタビ復号器(Viterbi decoder)で誤り訂正後、デスクランブルを来ない、分配器にて通信信号と制御信号を分離する。この通信信号のみが伸張バッファ(Expansion buffer)にて伸張され地上網・端末へ連続信号として伝送される。

### 6.2.2 TDMA装置同期制御部の主な回路

## ① エラスティックバッファ

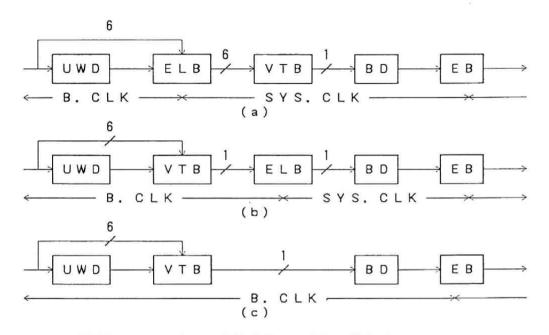

時間的にゆらぎがありまた位相ジッタのある再生バーストクロックかたTDMA装置のシステムクロックに受信データを読み替える(クロックリタイミング)回路であり、また受信フレーム上ガードタイム内の受信データ位置変動の修正(バースト位置リタイミング)を行う。受信での本エラスティックバッファの位置づけは図6.2に示すように一般に以下の3種が考えられる。

- (i) ユニークワード検出回路の直後

- (ii)誤り訂正回路の直後

- (iii) 伸張バッファと兼用

図 6. 2 は誤り訂正に 3 ビット軟判定信号(I, Q 計 6 系列信号)を使用した場合の例であり、(ii)方式によるエラスティックバッファのハードウェアは(i)方式に比較し約 1 / 6 になる。一方、 3 ビット軟判定を行わない場合には(i)方式と(ii)方式とのエラスティックファハードウェア上の差はない。(iii)は伸張バッファにエラスティック

バッファの機能を持たせる方式であり、最もハードウェア量は小となるが、ユニークワード検出後伸張バッファの入力までS/Nの悪いバーストクロックで動作することが必要となる。実際の装置では、これらを勘案しエラスティックバッファの位置づけを決める。エラスティックバッファの基本的構成は「直並列変換+並直列変換」回路であり直並列変換段数分のバースト位置誤差修正が可能である。

UWD:ユニークワード検出器 EB:伸張バッファ

ELB:エラスティックバッファ B. CLK:Burst clock

VTB: ビタビ復号器 SYS. CLK: System clock

BD:バースト分離回路

図 6 . 2 エラスティックバッファの位置づけ (QPSK, 3ビット軟判定処理)

#### ② ドップラーバッファ

衛星のドップラー変動を吸収するために使用されるバッファはドップラーバッファと呼ばれる。ドップラーバッファの容量は衛星軌道保持精度、衛星位置等によって異なり例えば CS-3クラスの軌道保持精度で日本をサービス域とする場合には約±100μsを考慮する必要がある。このようなドップラーバッファを実現する方法には以下の2種が考えられる。

- (i) ドップラーバッファ機能を個別ハードウェアとして実現する方法

- (ii)ドップラーバッファの機能を伸張・圧縮バッファに同時に持たせる方法 通常は(ii)の方法で構成されることが多い。

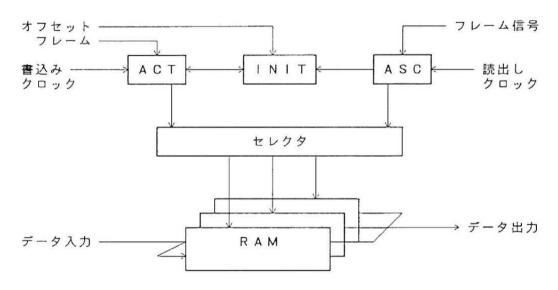

#### ③ 伸張/圧縮バッファ

通常これらバッファは2面または3面構成RAMにより実現され伸張/圧縮とも同様の構成である。伸張バッファを3面構成のRAMで実現する場合の構成例を図6.3に示す。地上PCM信号アドレスカウンタで書込み用RAMを選定すると同時に巡回する3面のRAMのうち地上側で選定したRAMからみて最も遠いRAMを衛星回線アドレスカウンタで選定する。このように3面のバッファを順次選択することにより、信号の欠落を伴わず圧縮を行う。

図6.3 圧縮(伸張)バッファの構成

#### ④ 受信/送信同期回路

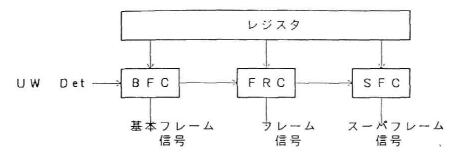

基本受信同期回路の構成例を図6.4に示す(3層フレーム構成の場合)。受信同期回路の基本はユニークワード検出(UW DET)信号でリセットされる基本フレームカウンタ、フレームカウンタ、および超フレームカウンタである。各フレームカウンタは自局が受信すべき受信フレーム時刻に対応してあらかじめ設定されたレジスタ値との一致時にそれぞれのフレームパルスを出力する。

送信同期回路の構成も基本的には受信同期回路の構成と同じであるが、カウンタのリセット信号がユニークワード検出信号でなく、受信同期回路を経て得られる送信フレーム開始信号となる。

UW Det:ユニークワード検出信号

BFC:基本フレームカウンタ

FRC: フレームカウンタ SFC: スーパフレームカウンタ

図6.4 基本受信同期回路の構成

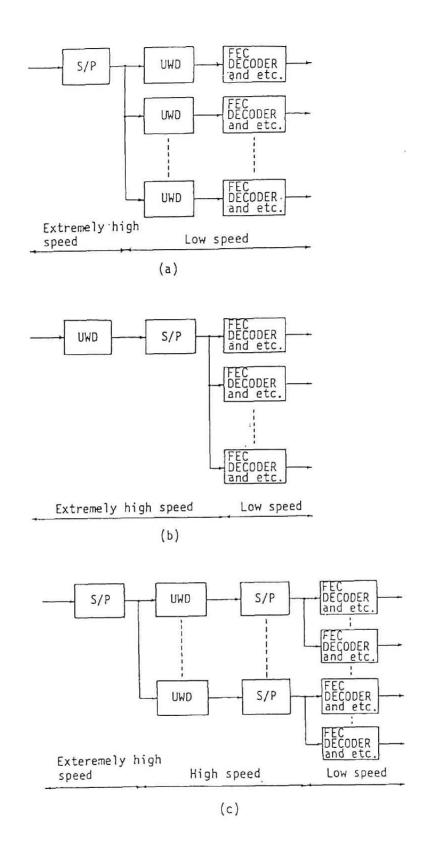

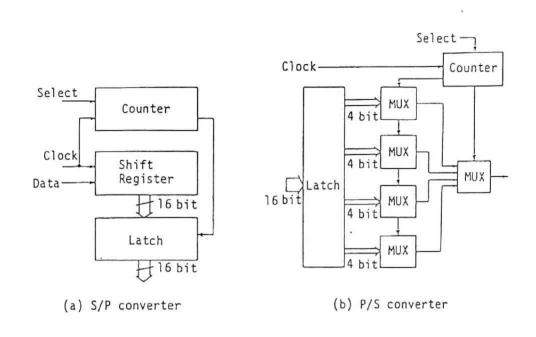

## 6.3 TDMA装置のLSI化手法(9)(10)