146

### ALGORITHMS FOR CERTAIN PACKING PROBLEMS

Takao Ozawa and Atsuyuki Kakehi 小澤 孝夫 鬼 宛 行 Department of Electrical Engineering, Kyoto University

### 1. Introduction

Procedures using rectangular dissection have been proposed for layouting an electronic circuit on a planar semiconductor chip(1)(2). In the procedures circuit modules(components) are assigned to elementary rectangles obtained by the dissection. Unfortunately very often the sizes of elementary rectangles become far larger than those of modules assigned to them. Therefore a compaction procedure (3) is necessary to reduce the whole chip size. The layout compaction can be regarded as a special packing problem(4) with certain extra constraints. Especially the compaction should not harm the planarity of the circuit. Although the final object is to minimize the size of the chip where the circuit is laid out, it seems there is little hope to find efficient algorithms for achieving this goal. Here two packing problems approximating the layout compaction are formulated, and heuristic algorithms for solving the problems are presented.

### 2. Problem Formulation

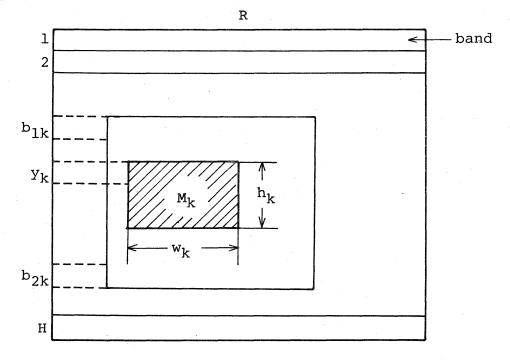

Let R be the rectangle representing the chip. We quantize R and divide it into H horizontal bands. A band is a rectangle with unit height and the width equal to that of R. See Fig. 1.

The bands are numbered from 1 to H, the uppermost band being No. 1 and the lowermost one, No. H. Let  $\mathbf{M}_k(k=1,2,\ldots,N)$  be a rectangular module with quantized height  $\mathbf{h}_k$  and width  $\mathbf{w}_k$ . We require  $\mathbf{M}_k$  be placed within the region which consists of bands from  $\mathbf{b}_{1k}$  to  $\mathbf{b}_{2k}$ . The horizontal edges of  $\mathbf{M}_k$  must be on the horizontal edges of some bands. If the height of the region (= $\mathbf{b}_{2k}$ - $\mathbf{b}_{1k}$ +1) is larger than that of  $\mathbf{M}_k$ , we have freedom to choose the bands on which  $\mathbf{M}_k$  is placed. Let  $\mathbf{y}_k$  be the uppermost of the bands on which  $\mathbf{M}_k$  is placed. We must have  $\mathbf{b}_{1k} \leq \mathbf{y}_k \leq \mathbf{b}_{2k} - \mathbf{h}_k + 1$ .

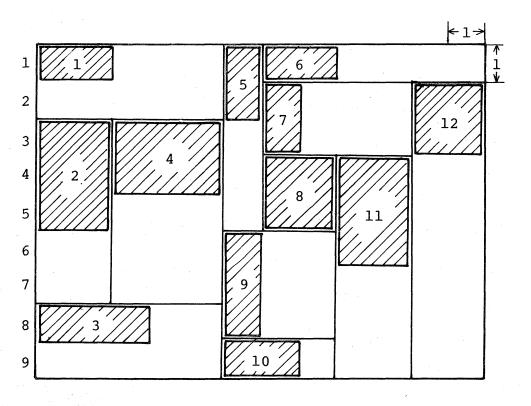

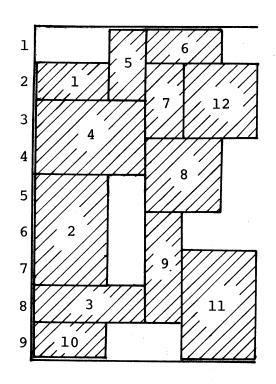

Suppose a rectangular dissection is obtained for the given circuit. This means that  $b_{1k}$  and  $b_{2k}$  for  $M_k(k=1,2,\ldots,N)$  are fixed as well as the relative position of the modules. An example of such a dissection together with modules assigned to elementary rectangles is shown in Fig. 2. The blank spaces in rectangles are redundant (Wires connecting the modules are laid out on the spaces, and therefore they are not totally redundant.), and we want to reduce such spaces by comaction.

Our first formulation approximating the layout compaction is as follows.

Pl. Choose  $y_1, y_2, ..., y_N$  to minimize

=0 otherwise

subject to  $b_{1k} \stackrel{\leq y}{=} k \stackrel{\leq b}{=} 2k^{-h}k^{+1}$  for k=1, 2, ..., N.

The condition  $y_k \le j \le y_k + h_k - 1$  means that module  $M_k$  is placed on band j, and  $W_j$  is the total of the widths of the modules placed on band j. When we determine  $y_1, y_2, \ldots, y_N$  by solving

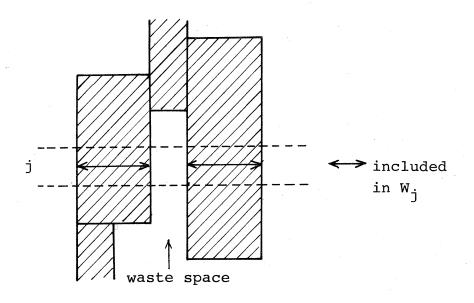

Pl, we move the modules to left(or right) as much as possible along the horizontal edges of bands while keeing their relative position as determined by the dissection. By doing this we remove redundant spaces between modules. In general the width of R thus achieved is more than the maximum of  $W_j$ 's, since there can be waste spaces between modules, as shown in Fig. 3, but  $W_j$  includes only the spaces occupied by the modules on band j.

In our second formulation the waste spaces stated above are taken into consideration. This is not an easy task and the cost for achieving this is to prefix the order in which the positions of modules are determined.

P2. Choose  $y_k$  for k=1, 2 ,.., and N to minimize

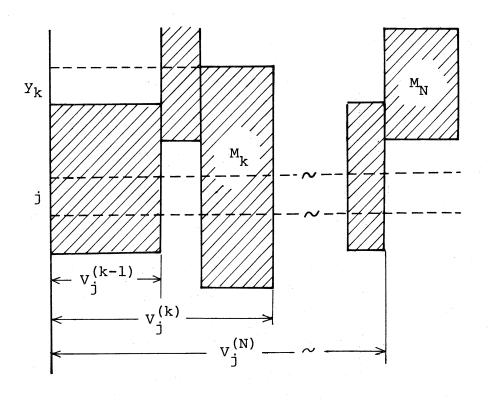

$$\begin{array}{ll} \max\limits_{1\leq j\leq H} \ V_j^{(N)} \text{, where } V_j^{(0)} = 0 \\ \\ V_j^{(k)} = \max\limits_{1\leq i\leq h_k} V_{y_k+i-1}^{(k-1)} + w_k \text{ if } y_k \leq j \leq y_k + h_k-1 \\ \\ = V_j^{(k)} \text{ otherwise,} \end{array}$$

subject to  $b_{1k} \leq y_k \leq b_{2k} - h_k + 1$  for k=1, 2, ..., and N.

In our second formulation modelu  $M_k$  is moved to right as much as possible along the horizontal edges of bands, as soon as its vertical position  $y_k$  is determined.  $V_j^{(k)}$  is the position, measured from the left edge of R, of the right edge of the leftmost module on band j after  $M_k$  is moved to right(See Fig. 4), and

$$\max_{1 \leq i \leq h_k} V_{y_k+i-1}^{(k-1)}$$

is the position of the right edge of the leftmost module on

bands  $y_k$ ,  $y_k^{+1}$ , ..., and  $y_k^{+h}$  -1 before  $M_k$  is placed on bands.

# 3. Algorithms

Since the number of modules in a circuit is very large, it is essential to use efficient algorithms for layouting them. Besides the formulations obtained in the previous section themselves are approximations of layout compaction. Therefore we do not stick to obtaining an optimal solution of Pl or P2, but rather aim to algorithms which can achieve good overall performance. Those presented in this section are so called heuristic algorithms.

We note that the vertical positions  $y_k$ 's of modules must be fixed one by one in any event. In fixing the position of one module, the problem is how can the remaining modules be taken into consideration. Because of the reasons stated above, we avoid iterative procedure, that is, once the position of a module is fixed, it will not be changed again. Instead we set up two types of criterion in fixing the position. The first one is the possible maximum of the total width of modules laid out on a band. This value, denoted by  $\mathbf{U}_j$  for band j, is first computed in step 1 (1) of Algorithms 1 and 2 below. When the position of a module is determined, this value is changed according to it.

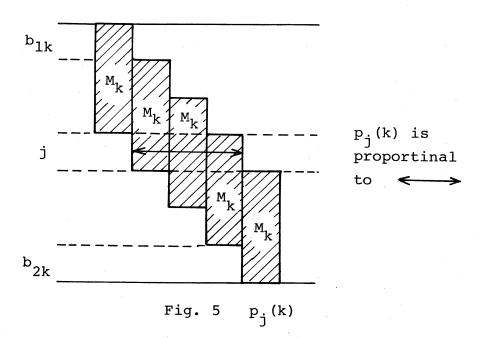

The second criterion is a probabilistic one. Let  $p_j(k)$  be the probability of module  $M_k$  being laid out on band j. We assume that the possibile positions of  $M_k$  one bands from  $b_{1k}$  to  $b_{2k}$  are equally probable, and we have:

150

$$\begin{array}{lll} p_{j}(k) &= (j-b_{1k}+1)/B_{k} & \text{if } b_{1k} \leq j \leq b_{1k}+h_{k}-1 \\ &= h_{k}/B_{k} & \text{if } b_{1k}+h_{k} \leq j \leq b_{2k}-h_{k} \\ &= (b_{2k}-j+1)/B_{k} & \text{if } b_{2k}-h_{k}+1 \leq j \leq b_{2k} \\ &= 0 & \text{otherwise} \end{array}$$

where  $B_k = b_{2k} - b_{1k} - h_k + 2$ . See Fig.5. Algorithms 1E and 2E below use this criterion.

Algorithm 1 for P1.

- step 1. (1) Set  $K \leftarrow \{1, 2, ..., N\}$ .

- (2) For  $j=1, 2, \ldots$ , and N compute

$$U_{j} = \sum_{k=1}^{N} w_{k}^{*} \quad \text{where } w_{k}^{*} = w_{k} \quad \text{if } b_{1k} \leq j \leq b_{2k}$$

$$= 0 \quad \text{otherwise}$$

step 2. Choose k ∈K such that

$$\max_{\substack{y_k \leq j \leq y_k + h_k - 1}} \text{U}_j \quad \text{subject to b}_{1k} \leq y_k \leq b_{2k} - h_k + 1$$

is minimum. Fix y<sub>k</sub>.

step 4. Set  $K\leftarrow K-\{k\}$ . If  $K=\emptyset$  stop. Otherwise go to step 2.

If there are more than one module which give the minimum of max  $U_j$  at step 2, the module which gives the minimum of the next to max  $U_j$  is chosen. Further ties are broken in the same way.

Algorithm 1E for P1.

step 1. (1) Set  $K \leftarrow \{1, 2, ..., N\}$ .

(2) For j=1, 2,..., and N compute

$$U_{j} = \sum_{k=1}^{N} w_{k} p_{j}(k)$$

step 2. Choose  $k \in K$  such that

$$\max_{\substack{y_k \leq j \leq y_k + h_k - 1}} \mathbf{U}_j \quad \text{subject to } \mathbf{b}_{1k} \leq y_k \leq \mathbf{b}_{2k} - \mathbf{h}_k + 1$$

is minimum.

step 3. For  $j=b_{1k}$ ,  $b_{1k}+1$ ,..., and  $b_{2k}$  set

step 4. Set  $K \leftarrow K - \{k\}$ . If  $K = \emptyset$ , stop. Otherwise go to step 2.

Algorithm 2 for P2.

step 1. For j=1, 2, ..., and H set  $Q_{j} \leftarrow 0$ . Set  $k \leftarrow 1$ .

step 2. Choose  $y_k$  so that

$$\max_{\substack{y_k \leq j \leq y_k + h_k - 1}} Q_j \quad \text{subject to } b_{1k} \leq y_k \leq b_{2k} - h_k + 1$$

is minimum. Fix y<sub>k</sub>.

step 3. For  $j=y_k$ ,  $y_k+1$ ,..., and  $y_k+h_k-1$  set

$$Q_{j \leftarrow \max_{y_{k} \leq i \leq y_{k} + h_{k} - 1}} Q_{i} + w_{k}.$$

step 4. If k=N, stop. Otherwise set k+k+1 and go to step 2.

Algorithm 2E for P2.

step 1. For  $j=1, 2, \ldots$ , and H set

(2)

$$P_{j} \leftarrow \sum_{k=1}^{N} w_{k} P_{j} (k)$$

(3)

$$U_{j} \leftarrow P_{j} + Q_{j}$$

.

Set k←l

step 2. Choose  $\mathbf{y}_{\mathbf{k}}$  so that

$$\max_{\substack{y_k \leq j \leq y_k + h_k - 1}} \mathbf{U}_j \quad \text{subject to } \mathbf{b}_{1k} = \mathbf{y}_k \leq \mathbf{b}_{1k} - \mathbf{h}_k + 1$$

is minimum. Fix  $y_k$ .

step 3. For  $j=b_{1k}$ ,  $b_{1k}+1$ , ..., and  $b_{2k}$  set

(1)

$$Q_{j} \leftarrow \max_{\substack{y_{k} \leq i \leq y_{k} + h_{k} - 1}} Q_{i} + w_{k} \quad \text{if } y_{k} \leq j \leq y_{k} + h_{k} - 1$$

$$\leftarrow Q_{j} \quad \text{otherwise}$$

(2)

$$P_j \leftarrow P_j - w_k p_j$$

(k),

step 4. If k=N, stop. Otherwise set k+k+1, and go to step 2.

If we apply Algorithm 1 to the example shown in Fig. 2, we obtain  $U_j$  as shown in Table 1 below, where I is the number of iterations of step 3. The modules chosen at step 2's and their vertical positions are given in the last two rows of Table 1. We get  $w_k p_j(k)$  as given in Table 2 for the example. Applying Algorithm 2E to the example, we get  $U_j$  as shown in Table 3. The layout of modules after compaction is shown in Fig. 6.

Table 1

K={1, 2, 3, 4, 5, 11, 12}

|   | I=      | 0  | 1            | 2   | 3   | 4 | 5  | 6   | 7 | _ |

|---|---------|----|--------------|-----|-----|---|----|-----|---|---|

|   | j=1     | 5  | 5            | 5   | 5   | 5 | 5  | 5   | 5 |   |

| ŋ | 2       | 6  | 4            | 4   | 4   | 4 | 4  | 4   | 4 |   |

|   | 3       | 9  | 9            | 8   | . 8 | 8 | 5  | 5   | 5 |   |

|   | 4       | 12 | 12           | 11  | 9   | 9 | 7  | 4   | 4 |   |

|   | 5       | 12 | 12           | 11  | 9   | 9 | 7  | · 7 | 7 |   |

|   | 6       | 10 | 10           | 10  | 8   | 8 | 6  | 6   | 4 |   |

|   | 7       | 10 | 10           | 10  | 8   | 8 | 8  | 5   | 3 |   |

|   | 8       | 8  | 8            | . 8 | 6   | 6 | 6  | 6   | 6 |   |

|   | 9       | 9  | 9            | 9   | 7   | 4 | 4  | 4   | 4 |   |

|   | k=      |    | 1            | 5   | 12  | 3 | 11 | 4   | 2 |   |

|   | $y_k =$ |    | , <b>1</b> , | 1   | 2   | 8 | 7  | 5   | 4 |   |

Table 2

|                                   | k=                                | 1    | 2                                    | 3 ,  | 4                                    | 5                                    | 11                           | 12                                                   |  |

|-----------------------------------|-----------------------------------|------|--------------------------------------|------|--------------------------------------|--------------------------------------|------------------------------|------------------------------------------------------|--|

| w <sub>k</sub> p <sub>j</sub> (k) | j=1<br>2<br>3<br>4<br>5<br>6<br>7 | 0.50 | 0.67<br>1.33<br>2.00<br>1.33<br>0.67 | 1.50 | 0.75<br>1.50<br>2.25<br>1.50<br>0.75 | 0.25<br>0.50<br>0.75<br>0.50<br>0.25 | 0.50<br>1.00<br>1.50<br>1.50 | 0.29<br>0.57<br>0.57<br>0.57<br>0.57<br>0.57<br>0.57 |  |

|                                   | 9                                 |      |                                      | 1.50 |                                      |                                      | 0.50                         | 0.29                                                 |  |

Table 3

|        | k=               | 1    | 2    | 3    | 4    | 5    | 6-10 | 11   | 12   |      |

|--------|------------------|------|------|------|------|------|------|------|------|------|

| U<br>j | j=1              | 3.25 | 2.25 | 2.25 | 2.25 | 2.25 | 5.00 | 5.00 | 5.00 | 5.00 |

|        | 2                | 2.79 | 3.79 | 3.79 | 3.79 | 3.79 | 4.29 | 4.29 | 4.29 | 6.00 |

|        | 3                | 3.74 | 3.74 | 3.07 | 3.07 | 5.32 | 4.57 | 4.57 | 4.57 | 6.00 |

|        | 4                | 6.40 | 6.40 | 5.07 | 5.07 | 6.57 | 6.07 | 6.07 | 5.57 | 5.00 |

|        | 5                | 8.07 | 8.07 | 8.07 | 8.07 | 5.82 | 5.57 | 6.57 | 5.57 | 5.00 |

|        | 6                | 5.90 | 5.90 | 6.57 | 6.57 | 5.07 | 5.07 | 6.07 | 4.57 | 4.00 |

|        | • . 7            | 4.49 | 4.49 | 5.82 | 5.82 | 5.07 | 5.07 | 6.07 | 6.57 | 6.00 |

|        | 8                | 4.07 | 4.07 | 4.07 | 5.57 | 5.57 | 5.57 | 5.57 | 6.57 | 6.00 |

|        | 9                | 4.29 | 4.29 | 4.29 | 2.79 | 2.79 | 2.79 | 2.79 | 6.29 | 6.00 |

|        | y <sub>k</sub> = | 2    | 5    | 8    | 3    | 1    |      | 7    | 2    |      |

154

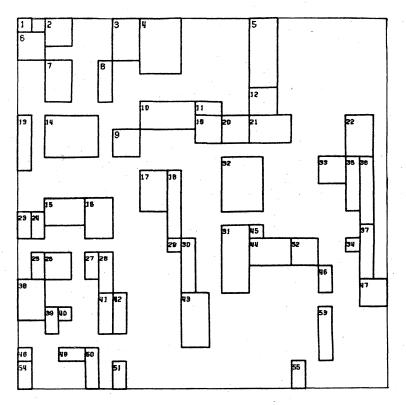

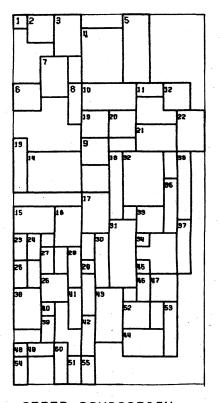

Algorithm 2E was computer programmed. An example of computer outputs is shown in Fig. 7.

## 4. Concluding Remarks

Mathematical modeling or problem formulation is the first step to be taken to accomplish automated circuit layout. This is an important but very difficult step, since there are many engineering restrictions to be observed in layouting a circuit. Especially, both the sizes of modules and the connection among them need be considered, that is, graph theoretical or combinatorial handling only is not enough. Here layout compaction is approximated by packing problems with regions for placing modules being specified. Only compaction in horizontal direction is described. Compaction in vertical direction which is to follow the compaction in horizontal direction needs another formulation.

Computer outputs of Algorithm 2E indicate usefulness of the algorithm, The crucial point with this algorithm is the order in which the positions of modules are determined. In our case this order can be obtained in a natural way from rectangle dissection. More waste spaces tend to appear as more positions of modules are fixed. Modification of the algorithm such as dividing the original rectangle into two or four subrectangles and then applying the algorithm to the subrectangles would result in better layouts.

### References

- (1) T. Ohtsuki, N. Sugiyama and H. Kawakita, "An optimization technique for integrated circuit design," Proc. Kyoto International Conference on Circuit and System Theory, pp. 67-68, 1970.

- (2) S. Nishikawa, K. Okada, K. Noshita, K Naemura and K. Hashimoto, "Algorithms of Musashino experimental design automation system for ic mask patterns MEDIC," Trans. Inst. Elect. and Commun. Eng. of Japan, vol. 55-A, No. 6, pp. 289-296, 1972.

- (3) M. K.Hsueh, "Symbolic layout compaction," in Computer Design Aids for VLSI Circuits, P. Antognetti, D. O. Pederson and H. Deman Edit. pp. 499-541, Sijthoff and Noordhoff, Alphen aan den Rijn, 1981.

- (4) B. S. Baker, E. G. Coffman and R. L. Rivest, "Orthognal packings in two dimensions," SIAM J. Computing, vol. 9, pp.846-855, 1980.

- (5) P. J. Federico, "Squaring Rectangles and Squares," in Graph Theory and Related Topics, J. A. Bondy and U.S. R. Murty Edit. pp. 173-196, Academic Press, N. Y., 1979.

Fig. 1 Quantization of R and  $\mathbf{M}_k$

Fig. 2 Example of dissection

Fig. 3 Waste space

Fig. 4 V<sub>j</sub><sup>(k)</sup>

Fig. 6 Layout after compaction

BEFORE COMPACTION

AFTER COMPACTION LENGTH\*\*1 AND WIDTH\*\*2

Fig. 7 Layout before and after compaction.