## Influence of uniaxial mechanical stress on the high frequency performance of metal-oxide-semiconductor field effect transistors on (100) Si wafer

Younggun Han,<sup>1,a)</sup> Masaaki Koganemaru,<sup>2</sup> Toru Ikeda,<sup>3</sup> Noriyuki Miyazaki,<sup>3</sup> Woon Choi,<sup>4</sup> and Hajime Tomokage<sup>4</sup>

<sup>1</sup>Knowledge Cluster Initiative Researcher, Fukuoka Science & Technology Foundation, 3-8-33 Momochihama, Sawara-ku, Fukuoka 814-0001, Japan

<sup>2</sup>Mechanics and Electronics Research Institute, Fukuoka Industrial Technology Center, 3-6-1 Norimatsu, Yahatanishi-ku, Kitakyushu 807-0831, Japan

<sup>3</sup>Department of Mechanical Engineering and Science, Graduate School of Engineering, Kyoto University, Yoshida-Honmachi, Sakyo-ku, Kyoto 606-8501, Japan

(Received 25 March 2010; accepted 19 April 2010; published online 27 May 2010)

The effects of uniaxial mechanical stress on the radio frequency performance of n- and p-metal-oxide-semiconductor field effect transistors (MOSFETs) are investigated up to 10 GHz. Under tensile stress, the gate transconductance (gm) increases in the n-MOSFETs while it decreases in the p-MOSFETs, whereas the results were vice versa for compressive stress. The total gate capacitance  $(C_G)$  extracted from scattering parameters increases (decreases) under tensile (compressive) stress for both n- and p-MOSFETs, which is explained by the variation in the effective mass perpendicular to the Si/SiO<sub>2</sub> interface. The cut-off frequency  $(f_T)$  varies in inverse proportion to the  $C_G$  variation. © 2010 American Institute of Physics. [doi:10.1063/1.3428793]

The continuous scaling down of metal-oxidesemiconductor field effect transistors (MOSFETs) has made it possible to extend the application area of MOSFETs into the rf performance ranges. However, it has also made the MOSFETs vulnerable to the performance degradation induced from short channel effects and process-induced mechanical stress, which is one of most critical factors in the reliability of short channel MOSFETs. The effect of mechanical stress on the direct current (dc) performance of MOSFETs such as drain current density, gate tunneling current, and gate transconductance (gm) have been studied extensively. 1-5 On the other hand, MOSFETs with a strained Si layer have also been investigated with respect to enhancement of the device performance. <sup>6-9</sup> The piezoresistive effect and deformation theory have been adopted to theoretically explain the stress-induced phenomena in a MOSFET. 10-12 Tensile and compressive stresses induce band splitting and electron/hole redistribution into the lower energy band, which triggers band gap narrowing, carrier scattering suppression, and variation in the electron/hole effective mass. However, direct research into the effect of stress on the device performance of MOSFETs in the rf region has not been performed. In order to obtain the stable performance of MOSFETs in rf region, lots of factors that trigger the performance fluctuation have to be considered carefully. Therefore, it is imperative to investigate and reduce the effects of stress on rf performance of MOSFET as well as dc performance. In this letter, we would like to discuss the effect of uniaxial mechanical stress on the rf performance parameters of MOSFETs such as gm, the gate extrinsic capacitance  $(C_G)$ , and the cut-off frequency  $(f_T)$  up to a frequency of 10 GHz.

Both n- and p-channel MOSFETs were fabricated on (100) silicon wafers with gate widths (W) and lengths (L) of 24  $\mu$ m and 0.5  $\mu$ m, respectively. Uniaxial mechanical stress was applied parallel to the  $\langle 110 \rangle$  drain current channels of the MOSFETs using a four-point bending system.<sup>4</sup> Each MOSFET was connected to pads in a ground-signal-ground configuration through a metal interconnect line for accurate microwave measurements. The gate and drain electrodes of the MOSFETs were connected to the input and output ports, respectively, while the source and substrate were grounded together. Scattering parameter measurements were performed between 0.01 and 10 GHz using a vector network analyzer (Agilent E8364B), with  $V_{ds} = \pm 1~V$  and  $V_{gs} = \pm 2.2~V$  for the n- and p-MOSFETs, respectively. The device tests were conducted after careful calibration steps using the openshort-load-through calibration method to minimize the measurement error.

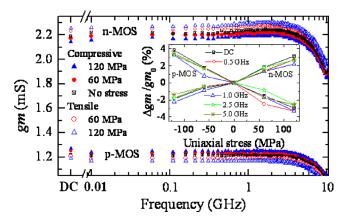

The rf parameters of the MOSFETs were extracted from the admittance Y-parameters converted from the deembedded scattering parameters using cold-FET measurement method.  $^{13}$  The gm was extracted from the real part of Y21. Figure 1 shows the variations in gm for the n- and p-MOSFETs with application of tensile and compressive mechanical stress in the frequency range from 0.01 to 10 GHz. The stress-induced variations in gm for dc operation were measured using different MOSFETs and were given together. The gm of the n-MOSFETs had higher values than those of the p-MOSFETs, due to the higher electron mobility and the abrupt decrease over 4 GHz could be attributed to gate resistance. 14 The gm of the n-MOSFETs were increased with tensile stress and decreased with compressive stress, whereas the results were vice versa for the p-MOSFETs. It has been well known that for n-MOSFETs, the variation in the effective carrier conductive mass and carrier mobility induced by electron repopulation into the lower energy twofold subbands and intervalley scattering suppression, due to widen-

<sup>&</sup>lt;sup>4</sup>Department of Electronics Engineering and Computer Science, Fukuoka University, 8-19-1 Nanakuma, Jonan-ku, Fukuoka 814-0189, Japan

a) Author to whom correspondence should be addressed. Electronic mail: young@lab-ist.jp. Tel.: +81-92-871-6631 Ext.: 6392. FAX: +81-92-865-6651.

FIG. 1. (Color online) Extracted gate transconductance vs frequency with change in the uniaxial mechanical stress for n- and p-MOSFETs. The inset is  $\Delta gm/gm_0$  on dc operation and at several radio frequencies as a function of the applied stress.

ing of band splitting after stress, could explain the phenomenon quite well. In the case of p-MOSFETs, it could be also explained by holes repopulation induced by valence band splitting after mechanical stress. These theories have been discussed extensively and approved as good approaches; therefore, we would like to confirm that the physical theories are also applicable up to the rf frequency region. It is quite reasonable that carrier generation and recombination in the MOSFET are able to keep up with the low gigahertz frequency change, because the MOSFETs had gate length of 0.5  $\mu$ m and could have  $f_T$  greater than 10 GHz. The dependency of gm on the stress is quite constant at the several operation frequencies including dc, as shown with the inset of Fig. 1. Consequently, it can be concluded that the transconductance of a MOSFET has constant dependence on stress from dc up to the cut-off frequency, which can be explained using the same piezoresistive effect as in the case of dc transconductance.

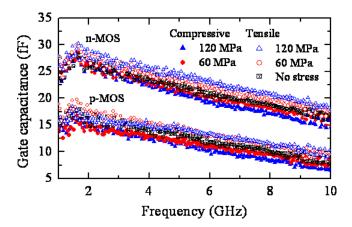

Figure 2 shows the stress dependence of the total extrinsic gate capacitance obtained from the imaginary part of  $Y11/\omega$ . <sup>14</sup> In contrast to the result for the gm, the opposite dependence on the mechanical stress was observed for the different types of MOSFETs, gate capacitance showed variation in the same direction irrespective of the carrier types of MOSFETs. That is, the gate capacitance of both types of MOSFETs was increased by tensile stress but decreased by

FIG. 2. (Color online) Extracted gate capacitance vs frequency with change in the uniaxial mechanical stress for n- and p-MOSFETs.

the compressive stress. The inconsistent values observed in the low gigahertz frequency region were related to the fluctuation of the phase of S12. These inconsistencies may be induced from the high impedance mismatch between the low capacitive input value of the small transistor and the internal reference impedance (50  $\Omega$ ) of the network analyzer. <sup>14</sup> The higher capacitance of n-MOSFETs is caused by the larger effective mass of electrons perpendicular to the Si/SiO<sub>2</sub> interface than that of holes. <sup>15</sup>

When the MOSFETs are operated at high frequencies, the gate capacitance  $(C_{\rm G})$  can be divided into the capacitance between the gate and the source  $(C_{\rm gs})$ , the capacitance between the gate and the drain  $(C_{\rm gd})$ , and the overlap capacitance between those electrodes  $(C_{\rm OL})$ . The source electrode is connected to the substrate as a common electrode and the gate is biased over the threshold voltage, therefore, the parasitic components related to the substrate can be neglected. Therefore, assuming a symmetric MOSFET structure, the total extrinsic gate capacitance is approximately expressed by

$$C_{\rm G} = C_{\rm gs} + C_{\rm gd} = 2C_{\rm OL} + \alpha C_{\rm g} ZL, \tag{1}$$

where  $\alpha$  is a constant less than one,  $C_{\rm g}$  is the gate capacitance per unit area, and Z and L are the width and the length of the gate, respectively. If the geometrical deformation of gate oxide and MOSFET electrodes are neglected, then the stress-induced variation in the total gate capacitance can be confined in the contribution from the inversion layer capacitance. For a strong inversion bias condition, the gate capacitance in a MOSFET can be expressed by  $^{16}$

$$C_{\rm g} = C_{\rm ox} \times \frac{1}{1 + C_{\rm ox}/C_{\rm inv}},\tag{2}$$

$$C_{\rm inv} = \frac{\varepsilon_{\rm Si}}{T_{\rm inv}} \approx \left(\frac{11\varepsilon_{\rm Si}^2 q^2}{72\hbar^2}\right)^{1/3} \times (m_{\perp}^*)^{1/3} \times N_{\rm S}^{1/3}$$

(3)

where  $\varepsilon_{Si}$  is the permittivity of Si,  $T_{inv}$  is the thickness of the inversion layer,  $\hbar$  is the Planck constant,  $m_{\perp}^*$  is the effective mass of electrons/holes of Si perpendicular to the Si/SiO<sub>2</sub> interface, and  $N_S$  is the surface carrier concentration. The total surface carrier density is almost constant for the strong inversion condition, even after the carrier redistribution into the lower energy subbands after the mechanical stress, therefore, the effect of stress on the inversion layer capacitance can be simply estimated at the point of the perpendicular effective mass. The variation in the effective mass will change the inversion layer capacitance in proportion to  $(m_{\perp}^*)^{1/3}$ . For n-MOSFETs, tensile stress induced electron repopulation into the  $\Delta_2$  subbands, which has an effective mass of  $m_{\perp}^* = 0.92m_0$  perpendicular to the interface of Si/SiO<sub>2</sub>, whereas compressive stress induced preferential electron population in the  $\Delta_4$  subbands, which has a perpendicular effective mass of  $m_{\perp}^* = 0.19m_0$ . By increasing the magnitude of the tensile strain, more electrons can possibly move to the  $\Delta_2$  subbands, which increases the effective mass of Si inversion layer in the direction perpendicular to the Si/SiO<sub>2</sub> interface and consequently increases the inversion capacitance. In a similar way, for the p-MOSFETs, it can be thought that tension (compression) induced carrier repopulation into the heavy (light) hole bands that have higher (lower) perpendicular effective mass  $m_{\perp}^* = 0.29 m_0$  (Ref. 17)  $(m_{\perp}^* = 0.2 m_0)$ can increase (decrease) the inversion capacitance. This pos-

TABLE I. Average stress-induced variation in transconductance (gm), gate capacitance  $(C_G)$ , and cut-off frequency  $(f_T)$  for n- and p-MOSFETs in the frequency range of 4–5 GHz. (-: compressive stress and +: tensile stress.)

| Stress | $\Delta gm$ (%) |       | $\Delta C_{ m G}$ (%) |        | $\frac{\Delta f_{\mathrm{T}}}{(\%)}$ |       |

|--------|-----------------|-------|-----------------------|--------|--------------------------------------|-------|

| (MPa)  | n               | p     | n                     | p      | n                                    | p     |

| -120   | -1.85           | 2.95  | -5.85                 | -11.51 | 4.32                                 | 16.61 |

| -60    | -0.67           | 1.13  | -3.09                 | -8.38  | 2.56                                 | 10.58 |

| 0      | 0               | 0     | 0                     | 0      | 0                                    | 0     |

| 60     | 1.59            | -1.94 | 4.09                  | 7.04   | -2.30                                | -9.42 |

| 120    | 2.69            | -3.51 | 7.89                  | 8.52   | -4.68                                | -9.69 |

tulation can explain the tendency of the stress-induced inversion capacitance variation but several questions still remain. For example, although the effective mass variation for n-MOSFETs was much bigger than that for p-MOSFETs, comparatively similar, or even larger, magnitude of inversion capacitance variation was observed for p-MOSFETs. The first possible reason for this could be the nonparabolic and anisotropic valence band structure, so that the stress can induce not only band splitting and carrier repopulation, but also the simultaneous variation in the perpendicular effective mass of each subband. That is, even if we postulate a constant perpendicular effective mass in each subband, the perpendicular effective mass itself could also change after the application of stress. The second possible reason is the higher sensitivity of the stress dependence for the p-MOSFETs, which could induce more abrupt changes, even in a smaller strain range. 12 However, the complexity of the valence band structure has hindered the exact evaluation of carrier behavior in strained p-MOSFETs.

From the relationship of  $f_T = gm/2\pi C_G$ , the effect of stress on the cut-off frequency was estimated from the average variation in the range from 4 to 5 GHz, which has the minimum data fluctuations considering both the gm and gate capacitance together. From Table I, it is apparent that for both types of MOSFETs the cut-off frequency can be increased by the application of compressive stress, and this is much more effective for p-MOSFETs.

In summary, the influences of mechanical stress on the rf performances of n-and p-MOSFETs up to 10 GHz were investigated. The stress dependency of gm on rf showed the

same results as that for gm with dc, and so could be explained by the variation in carrier mobility and in-plane effective mass due to band splitting. The variation in gate capacitance could be explained by the stress-induced variation in the effective mass perpendicular to the  $Si/SiO_2$  interface however, additional studies are required for a more exact explanation. The cut-off frequency was affected more by the gate capacitance variation. Comparing with the fluctuations of rf performance with different production lots,  $^{18}$  much more cautions have to be given to the variations by post-process induced stress.

This research was supported in part by a grant from the Fukuoka project of the Cooperation Link of Unique Science and Technology for Economy Revitalization (CLUSTER) sponsored by the Ministry of Education, Culture, Sports, Science, and Technology (MEXT) of Japan.

<sup>&</sup>lt;sup>1</sup>A. Hamada, T. Furusawa, N. Saito, and E. Takeda, IEEE Trans. Electron Devices **38**, 895 (1991).

<sup>&</sup>lt;sup>2</sup>K. Matsuda and Y. Kanda, Appl. Phys. Lett. **83**, 4351 (2003).

<sup>&</sup>lt;sup>3</sup>W. Zhao, A. Seabaugh, D. Jovanovic, and B. Winstead, IEEE Electron Device Lett. **26**, 410 (2005).

<sup>&</sup>lt;sup>4</sup>M. Koganemaru, T. Ikeda, N. Miyazaki, and H. Tomokage, J. Electron. Packag. **132**, 011003 (2010).

<sup>&</sup>lt;sup>5</sup>Y. S. Choi, T. Numata, T. Nishida, R. Harris, and S.-E. Thompson, J. Appl. Phys. **103**, 064510 (2008).

<sup>&</sup>lt;sup>6</sup>S. Takagi, J. L. Hoyt, J. J. Welse, and J. F. Gibbons, J. Appl. Phys. **80**, 1567 (1996).

<sup>&</sup>lt;sup>7</sup>G. F. Formicone, D. Vasileska, and D. K. Ferry, Solid-State Electron. **41**, 879 (1997).

<sup>&</sup>lt;sup>8</sup>Y.-J. Song, S.-H. Kim, S.-H. Lee, H.-C. Bae, J.-Y. Kang, K.-H. Shim, J.-H. Kim, and J.-I. Song, Solid-State Electron. 48, 315 (2004).

<sup>&</sup>lt;sup>9</sup>S. H. Olsen, A. G. O'Neill, P. Dobrosz, S. J. Bull, L. S. Driscoll, S. Chattopadhyay, and K. S. K. Kwa, J. Appl. Phys. 97, 114504 (2005).

<sup>10</sup>C.-S. Smith, Phys. Rev. 94, 42 (1954).

<sup>&</sup>lt;sup>11</sup>Z. Z. Wang, J. Suski, and D. Collard, Sens. Actuators, A 37–38, 357 (1993).

<sup>&</sup>lt;sup>12</sup>M. V. Fischetti and S. E. Laux, J. Appl. Phys. **80**, 2234 (1996).

<sup>&</sup>lt;sup>13</sup>D. Lederer J.-P. Raskin, Journal of Telecommunications and Information Technology, 2/2007, p. 69.

<sup>&</sup>lt;sup>14</sup>J.-P. Raskin, D. J. Pearman, G. Pailloncy, J. M. Larson, J. Snyder, D. L. Leadley, and T. E. Whall, IEEE Electron Device Lett. 29, 396 (2008).

<sup>&</sup>lt;sup>15</sup>S. Takagi, M. Takayanagi, and A. Toriumi, IEEE Trans. Electron Devices 46, 1446 (1999).

<sup>&</sup>lt;sup>16</sup>S. Takagi and A. Toriumi, IEEE Trans. Electron Devices **42**, 2125 (1995).

<sup>17</sup>C. Moglestue, J. Appl. Phys. **59**, 3175 (1986).

<sup>&</sup>lt;sup>18</sup>H. S. Kim, C. Chung, J. Lim, K. Park, H. Oh, and H. K. Kang, IEEE Electron Device Lett. 30, 855 (2009).