集積回路の統計的階層化設計手法に関する研究

# 目次

| 日次                              |                                                                                                                           | ,                                                  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 第1章                             | 序論                                                                                                                        | 1                                                  |

| 1.1                             | はじめに                                                                                                                      | 1                                                  |

| 1.2                             | 歩留まり最適化問題の定式化                                                                                                             | 2                                                  |

| 1.3                             | 設計の階層構造                                                                                                                   | 4                                                  |

|                                 | 1.3.1 アナログ回路の階層構造                                                                                                         | 4                                                  |

|                                 | 1.3.2 ディジタル回路の階層構造                                                                                                        |                                                    |

| 1.4                             | <b>従来研究</b>                                                                                                               | 9                                                  |

|                                 | 1.4.1 アナログ回路の統計解析                                                                                                         | 9                                                  |

| •                               | 1.4.2 システム特性の統計解析                                                                                                         | 12                                                 |

|                                 | 1.4.3 ディジタル回路の統計解析                                                                                                        |                                                    |

| 1.5                             | 本論文の概要と構成                                                                                                                 | 13                                                 |

|                                 |                                                                                                                           |                                                    |

|                                 |                                                                                                                           |                                                    |

| 第2章                             | 小規模回路の統計的歩留まり最適化手法                                                                                                        | 15                                                 |

| 第 <b>2</b> 章<br>2.1             | 小規模回路の統計的歩留まり最適化手法<br>はじめに                                                                                                |                                                    |

| 210                             |                                                                                                                           | 15                                                 |

| 2.1                             | はじめに                                                                                                                      | 15<br>17                                           |

| 2.1                             | はじめに                                                                                                                      | 15<br>17<br>18                                     |

| 2.1                             | はじめに                                                                                                                      | 15<br>17<br>18<br>21                               |

| 2.1                             | はじめに                                                                                                                      | 15<br>17<br>18<br>21<br>23                         |

| 2.1<br>2.2                      | はじめに                                                                                                                      | 15<br>17<br>18<br>21<br>23<br>25                   |

| 2.1<br>2.2<br>2.3               | はじめに<br>確率過程モデルによる応答曲面生成と大域的最適化<br>2.2.1 確率過程モデルによる応答曲面法<br>2.2.2 大域的最適化手法<br>2.2.3 確率過程モデルの適用例<br>歩留まり最適化手法              | 15<br>17<br>18<br>21<br>23<br>25<br>26             |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | はじめに                                                                                                                      | 15<br>17<br>18<br>21<br>23<br>25<br>26<br>28       |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | はじめに<br>確率過程モデルによる応答曲面生成と大域的最適化<br>2.2.1 確率過程モデルによる応答曲面法<br>2.2.2 大域的最適化手法<br>2.2.3 確率過程モデルの適用例<br>歩留まり最適化手法<br>実験<br>まとめ | 15<br>17<br>18<br>21<br>23<br>25<br>26<br>28       |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | はじめに                                                                                                                      | 15<br>17<br>18<br>21<br>23<br>25<br>26<br>28<br>31 |

ii 目次

| 3.3              | 階層的統計解析手法                | 32 |

|------------------|--------------------------|----|

| 3.4              | 実験                       | 35 |

|                  | 3.4.1 PLL の機能記述モデル       | 33 |

|                  | 3.4.2 機能記述モデルの精度         | 37 |

|                  | 3.4.3 階層的統計解析            | 38 |

| 3.5              | まとめ                      | 46 |

| 第4章              | 階層的歩留まり最適化手法             | 47 |

| 4.1              | はじめに                     |    |

| 4.2              | 階層的設計と制約生成               |    |

| 4.3              | 提案手法                     |    |

| 4.4              | 実験                       |    |

| 4.4              | まとめ                      |    |

| 4.5              | \$ C ∞ J                 | 56 |

| 第5章              | ベクトル合成モデルによる統計的遅延解析      | 59 |

| 5.1              | はじめに                     |    |

| 5.2              | ワーストケース解析と1次係数ベクトル       |    |

| 5.3              | セルの遅延特性のワーストケースと応答曲面     | 63 |

| 5.4              | 応答曲面の合成                  | 64 |

| $5.\overline{5}$ | 実験                       | 66 |

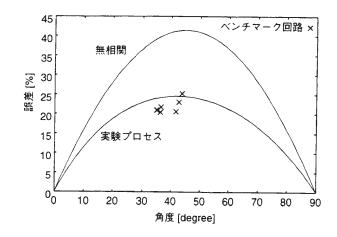

|                  | 5.5.1 1次係数ベクトルの方向        | 66 |

|                  | 5.5.2 応答曲面の合成とワーストケース解析  | 67 |

|                  | 5.5.3 電流モデルとベクトル合成モデル    | 70 |

| 5.6              | まとめ                      | 71 |

| 第6章              | テーブル参照による大規模集積回路の統計的遅延解析 | 73 |

| 6.1              | はじめに                     | 73 |

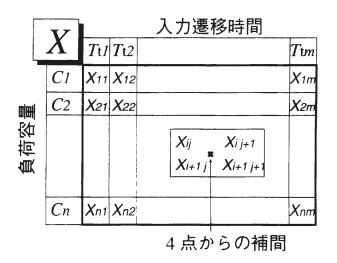

|                  | テーブル参照モデルによる応答曲面生成       |    |

| 6.3              | 実験                       |    |

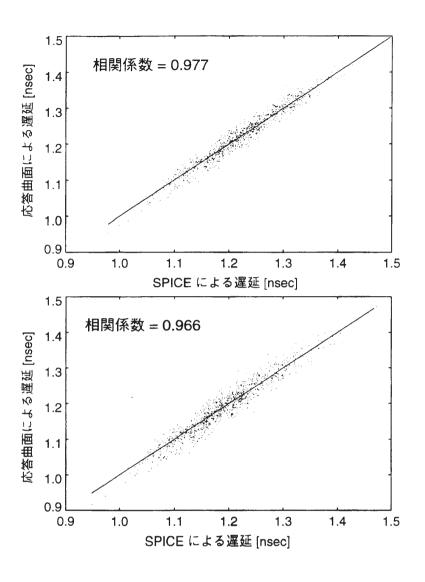

| 0.5              | 6.3.1 テーブルによる応答曲面生成実験    | 76 |

|                  | 6.3.2 提案手法の誤差の評価         |    |

| C 4              |                          | 80 |

| 6.4              | まとめ                      | 82 |

| 第7章              | 結論                       | 83 |

| 謝辞               |                          | 87 |

| 参考文献             | <b>₹</b>                 | 89 |

| 本研究に             | こ関する発表                   | 97 |

| 目次  |                                 | iii |

|-----|---------------------------------|-----|

|     |                                 |     |

| 付録A | 階層間のモデル化手法の詳細                   | 99  |

| A.1 | 統計的デバイスモデル                      | 99  |

|     | A.1.1 中間モデル                     | 99  |

|     | A.1.2 MOSFET モデルパラメータの統計情報の抽出手順 | 100 |

| A.2 | 応答曲面法                           | 102 |

|     | A.2.1 最小二乗法と正規方程式               | 103 |

|     | A.2.2 応答曲面の応用例—モンテカルロ解析         | 105 |

## 第1章

## 序論

#### 1.1 はじめに

半導体集積回路の発展はとどまるところを知らず、その開発の初期から今日に至るまでほぼムーアの法則に従い、18カ月で集積度、処理速度が2倍のペースで進歩している。例えば、回路規模で見た場合、最新のプロセッサにおいて数千万トランジスタを数え、また、アナログ集積回路においてもアナログ単体で2万トランジスタを越える集積回路が実品種として製作されている例もある。アナログ集積回路に関してさらに言えば、システム全体を1つの集積回路上で実現するシステムLSIの要請からもアナログ・ディジタル混載が増え、大規模回路の中でアナログ回路が用いられる機会が今後も増えるであろう。

一方,大規模化を支える基盤技術に目を向けると,デバイス製作の微細化技術がある。年々ゲート長の最小寸法は短くなってきており,2000年時点において,商業ベースにおいて  $0.18\mu\mathrm{m}$  からさらには  $0.13\mu\mathrm{m}$  へと微細化が進んでいる状況である。微細化技術がチップ面積の縮小と回路大規模化をもたらしたが,同時にこの技術により従来のトランジスタでは見られなかった種々の問題が顕在化している。本論文で取り上げるトランジスタ特性のばらつきもこうした問題の顕著な一例である。微細化の進展とともにばらつきが顕著となった原因として,寸法の微細化と比較して同じ割合でプロセスのばらつきを制御できないことがあげられる。例えば,ゲート寸法の微細化にともないチャネル領域中のイオン注入の絶対量が少なくなっており,イオン注入量のばらつきがわずかであっても相対的な濃度のばらつきが大きくなってよう。また,リソグラフィ工程やエッチング工程においては寸法に対する要求精度が高く,ばらつきの大きな要因となっている。

このようなプロセスのばらつきに起因してトランジスタ特性がばらつき、結果として回路特性がばらついてしまう。そのため、与えられた仕様を満たさない回路が得られてしまい、歩留まりの低下につながる。そこで、本論文では、このようなプロセス特性のばらつきが回路にどのような影響を及ぼすのか、それに対してどのよ

うな対策を取ることができるのかを、計算機設計支援(CAD)技術の立場から論ずることを目的とする.

冒頭でふれたように、ディジタル、アナログに関わらず大規模化の傾向は顕著である。そこで本研究でも、大規模回路においてばらつきを考慮した設計をいかに行なうかに焦点をあてる。ところで、大規模集積回路に対する設計手法として、階層化設計と呼ばれる手法が主流となっている。階層化設計とは、上位から下位へと連なる階層構造において、全体から細部、抽象から具体へと記述の度合を変えつつ、回路を記述、設計する手法である。本研究でも大規模集積回路の設計概念として、階層化設計を中心に据えることにする。つまり、階層化設計の枠組の中に統計的設計手法を取り込むことで、大規模集積回路の統計的設計を実現することを目標とする。

本章の構成は以下の通りである。本論文で取り組む課題を明確にするために1.2節で問題の定式化を行なう。次に本論文で取り扱う設計の階層構造の定義を1.3節で行なう。これらの定式化と定義を踏まえて、この分野における従来研究を1.4節で述べる。1.5節で本論文の具体的な目標ならびに概要と構成を述べる。

## 1.2 歩留まり最適化問題の定式化

従来から,回路素子のばらつきから回路特性のばらつきを解析する統計解析,さらに歩留まりの指標を目的関数とし,回路定数を合わせ込む歩留まり最適化技術などの研究が行なわれてきた.ここでは,これらの研究がとり扱ってきた問題を説明し定式化する.

まず、回路特性を決定する 2 種類のパラメータを定義する.一つは製造プロセスの定数やトランジスタの電気的特性(例えばしきい値電圧)である.これらは設計者が回路設計時に変更できない.また、製造時の条件によりばらつくという性質を持つ.そこで、このパラメータを回路の変動の源という意味で変動変数と呼び、 $n_p$  個存在するとしてベクトル  $\mathbf{p}=(p_1,p_2,\ldots,p_{n_p})^T$  で表す.もう一つのパラメータは、設計者が回路設計時に設計可能な変数で、設計変数と呼ぶ.設計変数にはトランジスタの寸法 $^1$  (ゲート幅、長さ)、抵抗値、容量値などがある. $n_d$  個の変数があるとして、これをベクトル  $\mathbf{d}=(d_1,d_2,\ldots,d_{n_d})^T$ で表す.

注目する回路特性が $n_c$  個存在するとして,これをベクトル $\mathbf{c}=(c_1,c_2,\ldots,c_{n_c})^T$ で表す.以下のように,それぞれの回路特性 $c_i$  に対して仕様の上限 $c_i^U$  と下限 $c_i^L$  が決まっているものとする.

$$c_i^L \le c_i \le c_i^U, i = 1, \dots, n_c$$

(1.1)

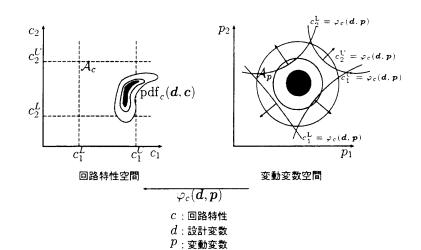

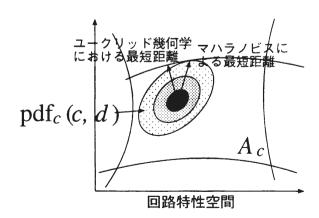

$n_c$  次元の回路特性空間において仕様を満たす容認領域(acceptability region) $A_c$  を 次のように定義する(図 1.1 左参照).

$$\mathcal{A}_{c} = \{ c \mid c_{i}^{L} \leq c_{i} \leq c_{i}^{U}, i = 1, \dots, n_{c} \}$$

(1.2)

図 1.1: 歩留まりと歩留まり最適化の概念

このとき、特性空間における回路特性の確率密度関数を  $pdf_c(\boldsymbol{d}, \boldsymbol{c})$  とする.このとき特性  $\boldsymbol{c}^0$  をとる確率は  $pdf_c(\boldsymbol{d}, \boldsymbol{c}^0)$  dc となる.設計変数を変更すると,その特性をとる回路の出現確率も変化するので,確率密度関数は  $\boldsymbol{d}$  の関数になる.歩留まりは容認領域内に出現する確率であるので以下のように表される.

$$Y = \text{Prob}\{\boldsymbol{c} \in \mathcal{A}_c\} = \int_{A} \text{pdf}_c(\boldsymbol{d}, \boldsymbol{c}) d\boldsymbol{c}$$

(1.3)

これが、回路特性空間で定義される歩留まりである.

1.2. 歩留まり最適化問題の定式化

一般に  $pdf_c$  を求めることは困難であるため,式(1.3)が統計解析に用いられることは少ない.その代わりに変動変数空間で歩留まりを考え,統計解析ならびに歩留まり最適化に利用することがより一般的に行なわれる.そこで変動変数空間で歩留まりを定義する.回路特性空間において定義した概念を変動変数空間に移す.この目的のために,変動空間と特性空間を結びつける変換  $\varphi_c(d,p): p \to c$  を利用する.これを用いると変動変数空間での容認領域は

$$\mathcal{A}_{p}(\boldsymbol{d}) = \{ \boldsymbol{p} \mid \boldsymbol{c}^{L} \leq \boldsymbol{\varphi}_{c}(\boldsymbol{d}, \boldsymbol{p}) \leq \boldsymbol{c}^{U} \}$$

(1.4)

となる. 回路特性空間では確率密度関数が設計変数の関数になったが、今度は容認領域が設計変数 d の関数になる (図1.1 右参照). 歩留まりは次のように再定義できる.

$$Y = \operatorname{Prob}\{\boldsymbol{p} \in \mathcal{A}_{p}(\boldsymbol{d})\} = \int_{\mathcal{A}_{p}(\boldsymbol{d})} \operatorname{pdf}_{p}(\boldsymbol{p}) d\boldsymbol{p}$$

(1.5)

ここで  $pdf_n(p)$  は変動変数の確率密度関数を表す.

<sup>1</sup>トランジスタの寸法は、同時に変動変数でもある.

以上で変動変数空間中で歩留まりを定義できたので、さらに歩留まりの最適化問題を以下のように定式化する.

$$\max_{\mathbf{d}} \{Y = \int_{\mathcal{A}_p(\mathbf{d})} \mathrm{pdf}_p(\mathbf{p}) \mathrm{d}\mathbf{p}\}$$

(1.6)

式 (1.6) の意味は、設計変数 d を変化させることで容認領域  $A_p(d)$  を変化させ、歩留まりを最大にするということである。ただし、設計変数 d を変化させる際に変動変数の確率密度関数  $pdf_p(p)$  は変化しない。

#### 1.3 設計の階層構造

この節では、本論文で取り扱う設計の階層構造について説明する。階層構造といっても問題のとらえ方によりさまざまな構造が定義できる。ここでは本論文で取り扱う統計解析の立場で、回路解析から見た定義を行なう。アナログ回路とディジタル回路では類似の階層モデルを用いるが、まずアナログ集積回路のためのモデルを1.3.1節に、次にディジタル集積回路のものを1.3.2節に述べる。

#### 1.3.1 アナログ回路の階層構造

先に述べたように、集積回路の素子数の増加傾向はアナログ回路においても例外ではなく、2万トランジスタを越える集積回路が実際の製品として開発されている。また、システム全体を1つのチップ内に納めるシステムLSIが実現されるようになり、ディジタル回路と混在設計を行なう事例が増えており、大規模回路の中にアナログ回路が組み込まれる機会も増えている。このような背景から、アナログ回路の設計方法にもさまざまな問題が生じている。例えば、1万素子程度を越えると設計者が回路の詳細まで気を配ることが難しく、設計が困難となる。また、回路特性の検証においてもSPICE系2のシミュレータでの回路解析には膨大な時間がかかり、実用上適用不可能であることが多い。

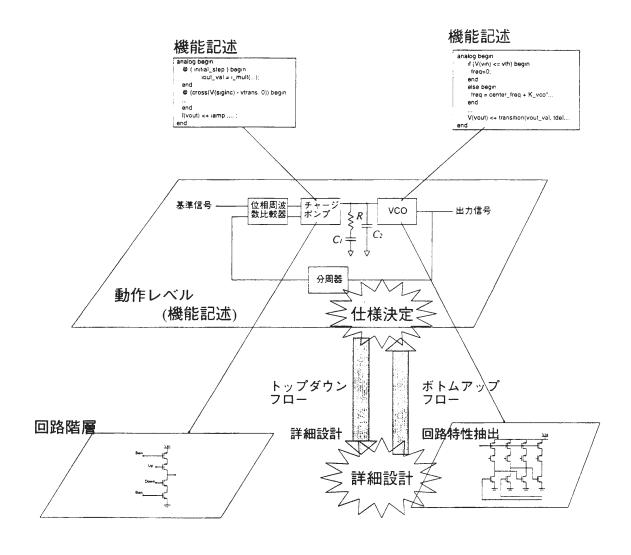

このような問題を解決する手法として近年用いられているのが、階層化設計である。これは、大規模回路を階層的に取り扱い、上位階層に行くほどシステム全体を抽象的な動作の記述で表現し、下位階層に行くに従い、より細く分割した回路の機能ブロックに対し具体的な素子の電気的接続関係で表現する。上位階層の動作記述では、この回路の動作を線形あるいは非線形の方程式、伝達関数、微分方程式などで書き表す。記述には、C言語などの汎用のプログラミング言語やこの目的のための専用の記述言語が用いられる。このように記述方法の抽象度にあわせて動作レベルと回路階層という2つの階層が存在する。各階層の記述の抽象度を表1.1に示す。

| 表 1.1: アナログ回路における階層の抽象層 | 表 1 | 1. | アナ | - 🏻 | ゲロ | 引路 | こお | :17 | 3 | 階層 | Ø. | 抽 | 象 | 度 |

|-------------------------|-----|----|----|-----|----|----|----|-----|---|----|----|---|---|---|

|-------------------------|-----|----|----|-----|----|----|----|-----|---|----|----|---|---|---|

| 抽象度   | 表現     | 記述に使用する概念               |

|-------|--------|-------------------------|

| 動作レベル | 言語記述   | 線形/非線形(微分)方程式, 伝達関数     |

| 回路階層  | アナログ素子 | 素子の電気的接続関係.素子の特性を表すモデル式 |

この概念を PLL (Phase Locked Loop) を例にとり図1.2 に示す. 動作レベルでは、例えば電圧制御発振器 (Voltage Control Oscillator: VCO) の発振周波数は入力電圧と周波数利得の積といったように、数式などを用いて書き表わされる. これに対して、回路階層においてはトランジスタなどの素子により具体的な回路の接続関係を記述する.

アナログ機能記述言語はディジタル回路の言語記述をもとにした動作検証に対して親和性があり、ディジタル回路との混載設計における動作検証を容易にする. また、SPICE系のシミュレータを用いた解析に対して2桁以上の速度で解析が可能である[1]. このように従来解析が不可能であったアナログ/ディジタル混在回路や、SPICE系の回路シミュレータでは実用時間で検証できなかったPLL回路などの解析に道を開いた.

このようなアナログの機能を言語により記述し、シミュレーションするという手法は古くから行なわれてきた[2].加えて近年、機能記述言語のいくつかが標準化され、急速に利用の広がりを見せている。現在までに標準化されている言語は Verilog のアナログへの拡張である Verilog-A と VHDLのそれにあたる VHDL-Aがある。これらは近年アナログ/ディジタル混在モデルへの対応にともない、Verilog-AMS [3]、VHDL-AMS [4] となっている。

ここで、この階層構造を用いた設計手法について説明する.階層を用いた設計手法にはトップダウン、ボトムアップの二通りの方法がある.これらを順に説明する.トップダウン設計において、上位階層は下位階層に対して仕様を与える働きをする.すなわち、システム階層で要求される仕様を満たすように、回路特性の仕様を検討する.このとき、下位階層で実現できる回路の特性、面積、コストなどを検討し、各回路の仕様を決めなければいけない.与えられた仕様をもとに、回路階層で回路設計が行なわれる.この概念を図1.2に下向きの矢印として示した.

逆にボトムアップによる方法とは、下位階層の特性から上位階層の特性をシミュレーションする手法で、階層構造を一つづつ上がっていくことでデバイスの特性からシステムの特性を得る。つまり、デバイス特性を表すモデルパラメータを使い SPICE により各機能ブロックの回路特性を求め、さらに、各回路の特性値をシステムの機能記述に適用し、システム解析により特性を求める。このボトムアップによるシステムの動作検証は、従来の SPICE 系のシミュレータでは計算コストの問題で解析できないシステムを、実用的な速度で解析可能とする点で有効である。ボトムアップ

<sup>&</sup>lt;sup>2</sup>Simulation Program with Integrated Circuit Emphasis: 米国のエレクトロニクス研究所 (Electronics Research Laboratory) とカルフォルニア大学バークレー校により開発された汎用回路シミュレータ. このシミュレータを元に商用に開発された製品が複数出ている.

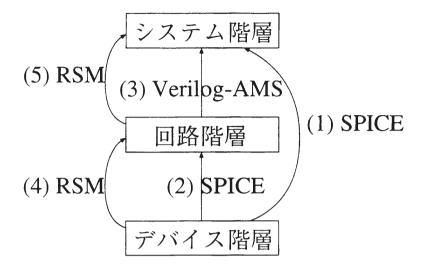

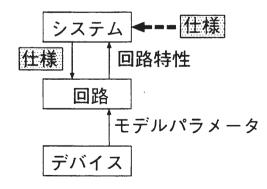

図 1.2: アナログ回路の階層設計の概念図

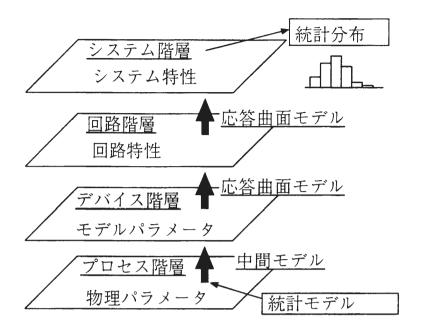

図 1.3: アナログ回路の階層構造

による解析の概念を図1.2の上向きの矢印で示す.

1.3. 設計の階層構造

通常,アナログ回路の階層設計では図1.2の下向きと上向きの矢印の行き来を何回 も繰り返すことで設計が進められる.

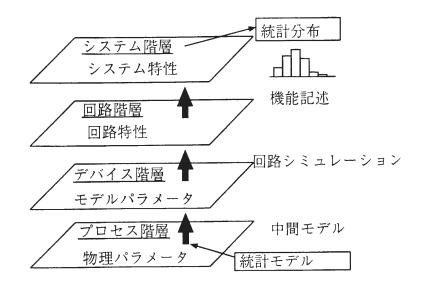

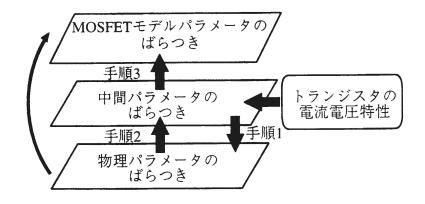

以上は記述の抽象度ならびにシステム全体から細部への分割という観点から、機 能記述の動作レベルとトランジスタ記述の回路階層に分けて考えた. 本論文では,こ の階層構造をさらにプロセスの物理特性にまで拡張したモデルを用いる. 取り扱う 階層モデルを図1.3に示す。それぞれの階層には、その記述方法に応じたモデルが存 在し、そのモデルの特性を記述するパラメータが存在する. これらを下の階層より 順に説明していく.

最下位層はプロセス階層である. ここでのパラメータは製造プロセスの物理パラ メータである。例えば、チャネル領域の不純物濃度や酸化膜厚である。また、設計 パラメータであるトランジスタの寸法もこの階層のパラメータに含まれる.

次の階層として、デバイス階層がある.この階層のパラメータは、デバイス特性を 表現するモデルのパラメータである. たとえば、SPICE などの回路シミュータにお ける素子モデルのパラメータがそれである. 通常. プロセス階層の物理パラメータ は、素子モデルの中に複雑に取り込まれており、モデルパラメータと物理パラメー タの関係が明らかでない場合が多い. そこで, 両者を関係付けるため, 単純な構造 の素子モデル (中間モデル) が提案されている [5]. 物理パラメータの統計情報は, 中間モデルパラメータの統計情報として表現し、デバイス階層のパラメータは中間 モデルパラメータからの変換操作で求めることができる。本論文でも物理パラメー タとモデルパラメータの関係付けに中間モデルを採用する.この手法の概要は付録 A.1 で説明する.

デバイス階層の上位には、回路階層が存在する、この階層は先の記述の抽象度によ る階層構造における回路階層と等しい. ここでのパラメータは回路特性である. PLL 回路を例にとると、構成要素である VCO の発振周波数利得やチャージポンプ回路の電流特性があげられる。通常、デバイス階層の素子モデルのパラメータを使って、回路シミュレーションによりこれらの値を求めることができる。

最上位に位置するのはシステム階層である.この階層は先の記述の抽象度による 階層構造における動作レベルと同一のものであるが,システム全体の動作を検証す ることからシステム階層と呼ぶことにする.ここでのパラメータはシステム全体の 特性である.PLL 回路を例にとるとロックアップ時間や位相雑音(ジッタ特性)な どがある.システム階層の動作記述では,下位の回路特性のパラメータをもとにシ ステム特性が記述される.

以上,ここで示したモデルでは下位のパラメータを入力として上位のパラメータが決定される.

この節の最後にばらつきを考慮した階層的解析手法ついて述べる。すべてのばらつきの源は、製造工程におけるプロセス階層の物理パラメータのばらつきである。ここで各階層の特性は、下位階層の特性から求めることができるため、下位階層から順に統計的な解析を行なうことで、原理的には物理パラメータのばらつきをもとに、これらのばらつきを求めることが可能である。

ここで2つの点に注意する必要がある。一つは回路階層の各個別の回路ブロックで独立にばらつきを計算し上位に渡す方法では、正確な統計解析が行なえない。つまりこの方法では各回路ブロック間の特性の相関が、上位階層の特性を解析する際に考慮されないからである。これを解決するためには、物理パラメータをもとに個々の回路の特性間の相関も含めた統計情報を解析する必要がある。また、階層構造を用いることで計算コストの軽減がはかられるが、統計解析では多数のシミュレーションが必要となり、依然、計算コストがかかる。そこで、いかに計算コストの軽減をはかるかがもう一つの注意すべき点である。以上をまとめると、統計的階層化設計では相関関係まで含めた統計情報を計算コストをかけずに階層間で受渡しする方法が必要である。

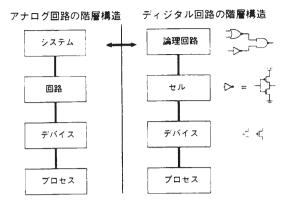

#### 1.3.2 ディジタル回路の階層構造

本論文ではディジタル回路の遅延時間の統計的解析手法を取り扱う.このためのディジタル回路の階層構造を図1.4のように定義する.この構造で、下の2つの階層はアナログ回路において定義したものと同じである.ディジタル回路の設計における基本単位はセルであり、セルライブラリ中のセルの組合せにより論理回路が構成される.そこで、上2つの階層は論理回路階層とセル階層とした.これら2つの階層における特性は遅延時間となる.最上位の論理回路の経路の遅延時間は構成セルの各遅延時間の和で表される.この点でこれらの特性を階層間でつなぐ定式化は容易と言える.これに対して、各セルの遅延時間はトランジスタ特性により決定されるため、両者をつなぐモデルが必要である.本論文では特にトランジスタの電流特性との関係に着目し、この階層間の関係をモデル化している.

図 1.4: ディジタル回路の階層構造

#### 1.4 従来研究

1.2節で述べた歩留まり及びその最適化問題の定式化と1.3節の設計の階層構造をもとに、従来のこの分野における研究について説明する。統計解析では、一般的に歩留まりの見積り精度と計算コストはトレードオフの関係にある。これまでの研究では、いかに精度の高い歩留まりの見積りを少ない計算コストで実現するかに焦点があてられており、ここでもこの観点からこれらの評価を行なう。また、もう一つの観点として、階層設計への親和性を取り上げる。

#### 1.4.1 アナログ回路の統計解析

ここでは、小規模な回路を対象とした歩留まり最適化問題に対する解法を概説する.これは、1.3節で説明した階層構造における回路階層の小規模に分割された回路に対する歩留まり最適化に相当する.この分野では古くから種々の方法が提案されている.これらは大きく分けて、歩留まりを直接計算しこれを最適化する直接法と、歩留まりの代わりとなる指標を使って最適化を行なう間接法がある.

直接法の代表的な手法としてモンテカルロ解析 [6] がある.式 (1.5) の積分を変動変数の確率密度関数に従う乱数を使って求める.この手法は、プログラム化が容易であり古くから行なわれてきた.また、解析精度が変動変数の数に依存しない性質があり、変動変数の数が多い場合はこの手法をとらざるを得ない.しかし、推定した歩留まりの信頼区間はサンプル数の平方根でしか比例して縮まらない.そのため十分な精度を保証するためにはたくさんのシミュレーションが必要である.また、乱数を生成し利用するため雑音が混入してしまい、最適化の過程において終了判定が難しいなど問題も多い.近年はラテン超立方(Latin Hypercube)[7] をサンプリング手法に採り入れ、少ないサンプル数で精度の良い解析を行なう手法が提案されている[8].

直接法を用いた最適化手法として,重心法 (Center of Gravity Method) [9] があ

る.この手法は次のような手順で進められる.設計空間内に、ある探索領域を設けモンテカルロ解析を行なう.次に領域中で仕様を満たす設計変数の重心と、満たさない変数の重心を求める.これら両重心を結ぶ線分の方向に探索領域を移して行き、最終的に高歩留まりの回路を得る手法である.アルゴリズムの簡便さが利点であるが、モンテカルロ法を基にしていることから、この方法も同様に多くのサンプル点を必要とし最適化アルゴリズムとしては不利である.このため、サンプルの再利用[6]や応答曲面[9]を用いる方法が提案されている.重心法では、モンテカルロ解析の結果を回帰分析するなどして、プロセス階層の物理パラメータと回路階層の特性を結びつけるモデルを生成することができる.このモデルを利用すると階層間での統計情報の受渡しを容易に行なうことができる.したがって、階層設計への親和性は高いと言える.

間接法の代表的な解析手法としてワーストケース解析がある。これは回路が最も悪い特性になる場合をワーストケースとして、その時の値を歩留まりの代わりのばらつきの指標とするものである。従来は頂点解析と呼ばれる手法が広く行なわれてきた[6]。これは変動変数のばらつきの範囲の端の点を組み合わせて回路解析を行ない、これらの値の最悪値をワーストケース値とする。この方法は簡便であるものの、悲観的な結果になりやすい傾向がある。これに対して、実際に変動変数の出現確率を考慮した、現実的なワーストケース(Realistic Worst-Case)解析も提案されている[10-12]。一般に、ワーストケースは回路ごとに異なる。そのため、階層設計中の分割された小回路ごとにワーストケースを求め、それらを組み合わせても、システム全体の特性のワーストケースとはならない。つまり、システム全体のワーストケースを知るためには、回路特性間の分布の相関などが必要であり、統計情報としては不十分である。この点からこの手法は階層設計には向かない。

間接法のもう一つの例としてデザインセンタリング法 [13-19] をあげる. 設計点を容認領域の中心になるように最適配置する手法である. 言い換えると設計点から容認領域への最小距離を最大にする最適化問題となる. この方法を幾何学的に図 1.1 (右)を使って考える. 1.2 節で説明した通り, 歩留まり最適化問題では, 容認領域内に変動の分布がなるべく収まるように, 設計変数を変化させて容認領域の境界を変化させる. このためにデザインセンタリング法では, 図 1.1 の変動変数の分布の中心から容認領域の境界までの最小距離を最大化する最小値最大化問題 (min-max 問題)を解くことになる. これを実現するためには容認領域を何らかの形で表し, その距離を計算する必要がある. これまでに報告されている手法は, この容認領域の表現方法に対しそれぞれ提案を行なっている.

デザインセンタリングの代表例として文献 [15] があげられる。これは容認領域を 多面体で表現する、変動変数の確率密度関数の等高面が楕円体であるとし、近似容 認領域に内接する最大の楕円体の中心を設計点とする。近似多面体は、頂点数の少 ない簡単なものから始め、頂点数を増やし実際の容認領域の形状に近付ける。新た な頂点は、多面体の最大面の中心から法線方向に容認領域の境界点を探索し得られ た点とする。ここで、境界点の探索には複数回の回路シミュレーションが必要であ り、計算コストがかかる原因となる。このように、多面体の頂点を増やしていき最終的に設計点の更新が起こらなくなった時点で最適化を停止する。この方法は幾何学的に分かりやすい手法である。しかし、この多面体による近似は容認領域が凸集合だけにしか適用できない欠点がある。また、設計変数の数の増加に対して計算コストが指数関数的に増える。

容認領域の別の近似手法として、回路の特性を変動変数の1次多項式で近似し、容認領域を求める手法も提案されている[13.17].この手法は特性の変動変数に対する感度(勾配)を、最適化の繰り返しごとに求める必要があり、計算コストの増大につながる.文献[13,17]で提案されている手法では特別なシミュレータを使うことで、感度解析にかかる計算コストを削減している.この点でこれらの手法は一般性に欠ける.

間接法の最後の例として面積分法をあげる. 歩留まりは,式(1.5)のように変動変数空間内の体積積分で表されるが,これをストークスの定理を用いて容認領域の境界の面積分に書き換えて計算するのがこの手法の特徴である[20].この手法を用いると,歩留まりの勾配も同じく面積分で計算できるため,最適化にこれを利用することができる.しかし,この手法の欠点は,容認領域の境界上で多数のシミュレーションを行なう必要があることと,最適化の収束が遅いことである.

一般論として、間接法は回路特性の分布を求めないため、階層設計において統計情報のやり取りを行なうことができない。ゆえに階層設計への親和性は高くない。

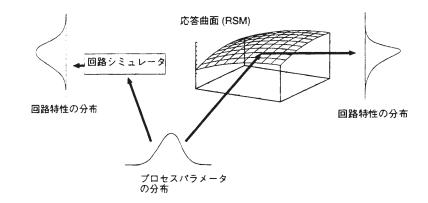

直接法,間接法の分類とは別に,応答曲面を用いた手法も多く提案されている[21-34].この手法は回路をブラックボックスとみなし,回路特性を説明変数の関数で近似する手法である.ここで,説明変数には変動変数のみが用いられる場合や変動変数と設計変数が用いられる場合がある.また,近似関数には主に低次の多項式が使われる.特性値を近似することから,シミュレーションを行なわずに少ない計算コストで特性値を得ることができる.このため,直接法として用いることができる.また,容認領域の境界の表現に使用できるため,間接法のデザインセンタリングにも利用できる.なお,応答曲面法に関する詳細は付録 A.2 で説明している.

応答曲面は、いくつかのサンプル点をとりその点での回路シミュレーションの結果から回帰分析することにより生成される。応答曲面自体はシミュレーションコストの削減に寄与するが、応答曲面の生成にはシミュレーションが必要である。したがって、生成に必要な計算コストを十分に考慮しなければならない。この計算コストを増大させる要因は、説明変数の数と近似多項式の次数や必要な項の数である。これらの要因が増すと計算コストが増え、この方法は実用的でなくなるため、これに対応する種々の提案がなされている。例えば、近似多項式の項を必要なもののみにふるい分けしたり、必要な項のみを選択し追加することで応答曲面を構築する手法が提案されている[27,30-32]。また、サンプルのとり方も、必要な項の選択と同じくらい応答曲面の精度と計算コストに影響があり、これらに関する研究も行なわれている[27,31]。

以上のような提案手法のいくつかを説明する. 2次多項式は n 個の説明変数に対

して項数が (n+1)(n+2)/2 個となり,通常の回帰ではこの数以上のサンプルが必要である。しかし,文献 [29.35] においては 2 次の項の影響が最小となるような制約条件をつけて,より少ないサンプル数で 2 次多項式の生成を行なっている。また,文献 [27.30] においては,1 次の多項式からはじめ,1 次同士の積項さらには 2 次項へと必要に応じて逐次項を追加し,精度をあげる手法が提案されている。ここでは,応答曲面の誤差を統計的に定式化しこの誤差の最小化問題を解くことで最適サンプルを生成している。同様に文献 [31.32] でも多項式の項の選択,サンプル手法の提案がされている。これらの提案により応答曲面の動的な項の追加とサンプルの追加を可能としているが,手法が複雑になっていることは否めない。

応答曲面法は計算コストをかけずに直接法による特性分布を求めることができるため、階層設計による統計解析との親和性は極めて高い.これまで述べてきた統計解析の手法の中では計算コスト、階層設計との親和性の面で一番利点がある.そこで、この論文でも応答曲面を用いた階層的統計解析手法を検討する.

#### 1.4.2 システム特性の統計解析

1.4.1節で説明した方法はすべて小規模の回路を対象としたものであった。なぜならば、シミュレーション時間のかかる大規模回路では計算コストの問題があり、統計解析が満足に行なえないからである。そのような中で、計算コスト削減を目的に、階層的解析を用いた統計解析手法が提案されている [36-40]。これらは 1.3 節で説明したボトムアップによる解析方法であり、プロセス階層の特性ばらつきをもとに、上位階層の回路特性のばらつき、システム特性のばらつきへと順に解析を進める。ここで、1.3 節でも述べたように、階層的な手法を用いる際には、階層間でいかに統計的な情報をやり取りするかが問題となる。これは、階層間で上位階層のパラメータと下位階層のパラメータの関係のモデル化を、いかに行なうかという問題でもある。これまでにモデル化手法として感度行列を元にした方法 [37]、回帰分析による手法 [36,38] さらに応答曲面による手法 [40] が提案されている。これらはいずれも、2次程度の簡単な多項式モデルを利用している。本研究は 1.4.1 節で説明したように応答曲面を用いた回路最適化を行なうので、ここであげた方法とは類似の手法である。

ところで、これらの手法は大規模回路の統計解析を可能としているが、本研究で 目標とする最適化設計までは到達していない。つまり、ボトムアップ手法では上位階 層のシステム階層で与えられた仕様を満たすための最適化設計は不可能であり、トッ プダウンによる方法論を持ち込まなければならない。そこで本研究では従来手法の ボトムアップによる階層的統計解析手法を用いつつ、さらにトップダウン設計手法 を採り入れ最適化技術の実現を目指す。

#### 1.4.3 ディジタル回路の統計解析

ディジタル回路においてもプロセスのばらつきに起因する遅延特性のばらつきの影響は無視できなく、遅延特性の統計的解析手法に対して種々の提案がある. 文献 [41] は入力信号の遷移時間の分布を元に出力の遷移時間の確率を求めている. しかし、確率を求めるために各ゲートごとに数値積分を逐次行なわなければいけないため、実際の解析としては現実的でない. これに対してより現実的な解析手法として、経路の遅延を数式的に表現した上で最長遅延となりうる経路の候補を選び出し、これらの遅延を統計的に計算する手法が提案されている [42]. この方法は各セルの遅延は互いに相関係数1でばらついているという仮定を行なっているのに対して、文献 [43] ではセル間における遅延の実際の相関までを考慮した手法を提案している. また、経路の遅延の分布をオペレーションズ・リサーチの PERT の技法をもとに解析する手法が提案されている [44].

以上の手法は経路の遅延分布をいかに見積もるかに主眼をおいた研究である.これらは,経路の遅延計算時に,各ゲートの遅延時間をあらかじめ何らかの分布で仮定している.しかし,本研究の階層的統計解析という立場から見ると,これはセル階層の遅延特性と回路階層の遅延特性のみを結びつけただけである.プロセスの物理特性を解析結果に反映させるためには,さらに下位のプロセス階層,デバイス階層のばらつきをセル階層の遅延に結びつける方法を検討する必要がある.そこで本研究では,トランジスタの物理パラメータのばらつきをセルの遅延に結びつける簡便かつ計算効率の高いモデルを提案する.この手法によりプロセス階層から論理回路の経路の遅延まで,階層構造を下から上へとたどる統計解析を実現する.

類似の研究として文献[45]では、トランジスタの簡単な解析モデルを提案し、これを利用し微分方程式を数値的に高速に解くシミュレータを開発している。トランジスタモデルは物理パラメータをパラメータとして持ち、統計的パラメータの構築を容易に行なえる。この手法もトランジスタのばらつきを遅延に結びつける点で、本研究と同じ目的である。しかし、独自のモデルとシミュレータを用いている点で既存の技術をそのまま用いることができない。本研究では、既存のパラメータをそのまま利用でき、かつシミュレーション環境も従来のものを利用した簡便な解析手法を目指す。

## 1.5 本論文の概要と構成

1.4節で紹介した従来研究を踏まえた上で、本研究の概要を述べる。本論文では大規模回路を階層的に取り扱うことで、統計的設計を実用的な計算コストで行なう手法を提案する。特に、階層間でどのような統計情報をいかにやり取りするかに焦点をあてる。ここでの課題は、精度と計算コストであり、これを実現する方法として1.4節で説明した応答曲面モデルを用いる。アナログ回路、ディジタル回路それぞれについて統計解析手法を論じている。アナログ回路においては、歩留まり最適化手

法を取り上げ、小規模の回路ブロックに適用する手法からはじめて大規模な階層的 最適化手法を提案している。また、ディジタル回路においては、経路の遅延時間の ばらつきを取り上げ、統計的解析手法を提案する、以下に構成を述べる。

第2~4章はアナログ回路に関する内容である。第2章において、小規模な回路に対する歩留まり最適化を行なう。これは、本論文においては、回路階層において分割された小規模な回路に適用される手法と位置付けされる。ここでは、回路の歩留まりを計算コストをかけずに見積り、さらに、最大の歩留まりを得るよう回路定数を合わせ込み、最適化を行なう。本論文では、後の章で説明する階層的設計におけるモデル化と親和性の高い手法の提案を行ない、階層間の統計情報の受渡しを容易にする。第3章では階層的な統計解析手法を検討する。ここでは、いかにプロセスの物理的なばらつき情報を設計階層の上位に伝えるかが課題となる。この際、考慮すべき点は計算時間と取り扱う統計情報の精度である。この2点について、提案手法の評価を行なった。第4章では第2、3章の検討結果に基づき、大規模集積回路の階層的最適設計について検討する。階層設計のトップダウン、ボトムアップの流れに統計情報のやりとりを組み入れ、ばらつきを考慮にいれたシステムレベルの設計の実現を目指す。

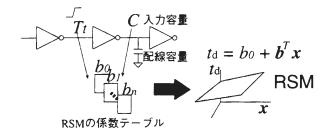

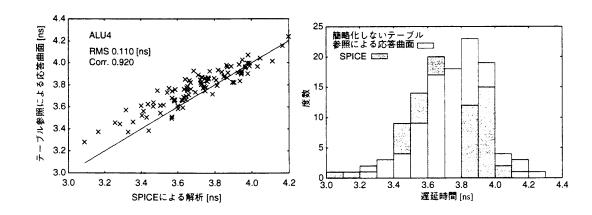

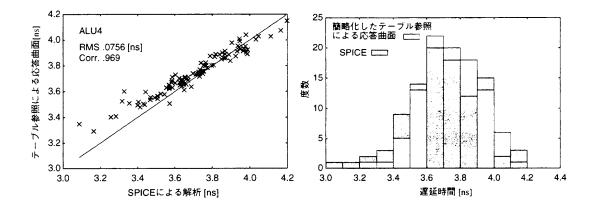

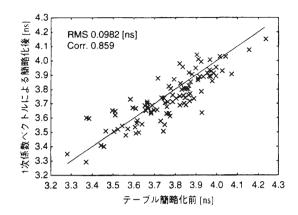

第5,6章はディジタル回路の遅延の統計的解析手法を取り扱う。まず、ディジタル回路の遅延時間とプロセスの物理パラメータのばらつきを関係づけるモデルを提案する。本手法では、トランジスタの電流特性と遅延時間の関係に着目し、そこから導かれる仮定をもとに1次係数ベクトルという遅延時間のばらつきを決める量を導く。これを使いベクトル合成モデルという遅延計算のためのモデルを提案する。以上が第5章の内容である。ベクトル合成モデルを使えば、計算コストをかけることなく遅延の統計解析を行なうことができるが、大規模集積回路においては、さらに簡便で高速な方法でこれを見積もる必要がある。そこで第6章では、ベクトル合成モデルの生成においてテーブル参照モデルを利用する方法を提案している。

第7章で本論文のまとめを行なう.

## 第2章

## 小規模回路の統計的歩留まり最適化手法

#### 2.1 はじめに

この章では小規模な回路の歩留まり最適化を取り扱う。これは続く2つの章で階 層的な統計解析、歩留まり最適化を行なうための基礎になる. ここでの問題の定式 化と従来の提案手法については第1章で述べた通りである。すなわち、この章におけ る課題もいかに計算時間をかけることなく最適化を行なうかにある. さらに、本論 文で主張する階層的最適化の枠組の中で考えるなら、ここで議論する最適化は、第1 章で説明した階層構造の回路階層において小規模に分割された回路への適用と位置 づけられる、階層的設計への組み込みを考えるならば、最適化の手法自体も階層的 な方法と親和性が高いことが望ましい、次の第3章でも述べるように、階層間の統計 情報の受渡しには第1章で説明した応答曲面モデルを用いる。このことから、ここで 提案する手法も応答曲面モデルを利用した最適化手法であることが望ましい。なぜ なら、最適化のために応答曲面を生成し利用するとともに、生成した応答曲面はそ のまま階層的な解析に利用できるからである. このことは、この章で議論する最適 化手法にもう一つの要求を付け加える。すなわち、最適化の過程で生成される応答 曲面は、階層的統計解析に利用できる程度の精度を持つのものでなければならない. 回路シミュレーションの代わりに応答曲面を利用し計算時間を削減する最適化手 法は、これまでにもいくつか提案されてきた[34,46].これらは応答曲面の生成方法 により2通りに分類される.

一つは設計変数、変動変数の両者を説明変数とした応答曲面を用いる方法である [34].この応答曲面は設計変数空間中の大域的な特性変動を考慮していることから、大域応答曲面と呼ばれる.この方法の利点は、応答曲面の説明変数として設計変数 が含まれているため、最適化過程での設計変数の探索の繰返しにおいてシミュレーションを行なう必要がないことである.逆に欠点は最適解の精度が悪く、最適点近傍の応答曲面の精度という点でも劣ることが挙げられる.これは以下のような理由 による、大局応答曲面の説明変数は設計変数と変動変数であり、その数は多い、その

ため、多項式の次数を上げると必要なシミュレーション回数が増加するので、2次多 項式程度が実用上の上限である. しかし,設計変数空間は広いため非線形性が強く なり、2次程度の多項式による当てはめでは不十分である場合が多い. 従って大域応 答曲面を精度良く生成することは困難であり、最適化の解の精度にも問題が生じる.

もう一つの応答曲面の生成方法として、設計変数空間中の点を指定し、その点にお いて変動変数のみを説明変数とする応答曲面を生成する手法が提案されている[46]. これは設計変数空間内のある点における局所的な応答曲面であることから、局所応 答曲面と呼ぶ、この手法は、応答曲面の精度が大域応答曲面より良く、したがって、 最適値と最適点における応答曲面の精度もこの手法の方が良い、しかし、この手法 は最適化過程における設計変数空間での探索の繰返しごとに、新しい設計点で応答 曲面を生成しなおす必要がある.よって、この繰返し回数の増加につれて計算コス トが増大する. そこでシミュレーション回数を削減する工夫が必要であり、例えば 文献 [46] では設計変数に対する回路特性の微分値を応答曲面生成と同時に得られる ように工夫している. こうすることで, 最適化に必要な微分値を新たにシミュレー ションを追加せずに計算することができる. しかし, 最適化の目的関数は必ずしも 微分可能とは限らず、また微係数を用いる準ニュートン法のような手法では局所的 な解に捕まる可能性もある.したがって、この手法の適用範囲には制限がある.

本論文においては、精度面での優位性から局所応答曲面を用いることにする.そ のため、最適化手法に効率の良い方法を用い最適化過程における最適解の探索の繰 返し回数を少なくしたい、この目的のために確率過程モデルによる応答曲面を使っ た最適化手法を適用する.ここで、確率過程モデルとは関数の振舞いを確率過程に より表し、ある点での関数値を推定するものである.

ここで用いる大域的最適化手法は目的関数値を直接用いて探索するのではなく, 確 率過程モデルから目的関数値を推定しながら最適解の候補となる設計点を探索する. このように応答曲面を利用し目的関数の形状を推測しながら最適化するので、目的 関数の評価回数の少ない、効率の良い最適化が行なえる。この最適解の候補の探索 には文献[47]で提案している改善期待関数を用いている。また、ここでは統計解析固 有の問題に対応するため、文献[47]で用いられているモデルの拡張を行なっている.

同じ確率過程モデルを用いた方法として文献[48]で提案されている方法がある.こ れは、解の存在しそうな領域にサンプル点を追加することでその領域の応答曲面の 精度を向上させ、最適解を得る手法である. しかし、この方法にはいくつかの問題 点を指摘することができる。一つは大域応答曲面を確率過程モデルを用いて生成し ている点である. 確率過程モデルでは、その振舞を決めるパラメータの推定が必要 であるが、考慮する空間の次元が上がるほど、またサンプル点の数が増えるほどモ デル生成にかかる計算コストが増加する.従って、大域応答曲面にこのモデルを適 用するのは実用的ではない.この点で、提案する手法は設計変数空間のみを考慮し ており、空間の次元を減らすことができる.また、文献 [48] では最適解の存在する 位置の推定方法が十分でなく、精度向上が見込めそうな領域を設計者が逐一指定し なければいけない点も問題である. つまり、アルゴリズムが自動化されてない. こ

れに対して、提案する手法は改善期待値関数を用いて自動化を可能にしている.

2.2. 確率過程モデルによる応答曲面生成と大域的最適化

本章は以下の構成になっている。まず、次の2.2節で確率過程モデルを用いた応答 曲面法とこれを用いた大域的最適化手法について述べる. 続いて 2.3 節で歩留まり最 適化問題の適用方法について説明する、2.4節でオペアンプに対する歩留まり最適化 の実験について述べる.

### 2.2 確率過程モデルによる応答曲面生成と大域的最適化

提案手法は計算コストを削減するために、設計変数空間に目的関数の応答曲面を 描き、目的関数値を推定しながら最適化を行なう、ここで、確率過程モデルについ て述べる前に、この目的のために多項式による応答曲面を利用したとしたら、どの ような問題点が存在するかを考える(多項式による応答曲面の生成方法の詳細は付 録A.2を参照.)まず、設計変数空間の大きさは変動変数空間のそれと比べて大きく、 この空間の関数は簡単な多項式で近似できない可能性がある、特に、計算コストの 制限から多項式の次数は2次程度が限度である.したがって、設計変数を含む空間で 精度の良い近似を行なうのは難しい、次に、回帰による当てはめを行なうので、サ ンプルの取り方は実験計画法などを用いてその配置を十分考慮する必要がある. と ころで、最適化の過程において、解の存在が見込まれる領域で応答曲面の精度を向 上させたい場合がある.しかし、実験計画法に基づいたサンプルの取り方への制約 から、特定の領域の精度をあげる目的でサンプル点を動的に追加するという操作は、 必ずしも期待通りの成果が得られない.

以上の問題を解決する方法として確率過程モデルを用いた応答曲面法が提案され ている [49-51]. この方法は、比較的少ないサンプル数で複雑な曲面のあてはめを行 なうことができる。また、動的なサンプルの追加も可能であり、精度をあげたい領 域にサンプルを追加することで任意の精度で推定が可能となる。この手法の特徴を 一言で言えば、多項式の回帰モデルが「関数の形」を推定するのに対して、確率過 程モデルでは「関数のふるまい」を推定する. 本研究でも、設計変数空間のような 広い空間での関数の当てはめには確率過程モデルを使うことにする. なお, 従来の 多項式の応答曲面は生成が簡単であるため、局所応答曲面のような狭い領域での当 てはめに用いる.

これまでにも確率過程モデルを用いた回路定数最適化手法の提案が行なわれてき た [48,52-55]. Groch らはウィーナー過程によるモデルを提案し回路の最適化を行 なっている [52]. Luらは確率過程モデルとして Schagen のモデル [49] を用い、更に 最適化のためのサンプルの追加方法や確率過程モデルのパラメータの推定方法を提 案している [53,54]. 先に説明したとおり Bernardo らは, Schagen と類似の Sacks ら によるモデル [50,51] を用いて、サンプル点を最適点近くに逐次追加することで歩留 まり最適化を行なっている[48]. この方法は Aslett らによって、出力バッファの設 計に用いられている[55].

このような中で、Jones らは Sacks らのモデルを用い、さらに大域的最適化の解の候補を確率的に求め、その点に新たにサンプルを追加していき最適点を求めるという手法を提案した [47]. この方法は効率も良く、しかも最適点の候補を捜し出してサンプルを追加する点で、提案手法の目的とも合致する. そこでこの最適化法を歩留まり最適化問題に適用することにした. 以下に簡単にこの手法の説明を行なう. なお、歩留まり最適化問題への適用のため、ここでは文献 [47] で用いたモデルの拡張を行なっている.

#### 2.2.1 確率過程モデルによる応答曲面法

k次元の空間にサンプル点  $\mathbf{x}^{(1)},\ldots,\mathbf{x}^{(n)}$  をとり、それらの点でのシミュレーション結果を  $y^{(i)}=y(\mathbf{x}^{(i)})$  とする.ここでモデル式として文献 [47] では次のようなものを考えている.

$$y(\boldsymbol{x}^{(i)}) = \mu + Z(\boldsymbol{x}^{(i)}) \tag{2.1}$$

このモデルは、平均 $\mu$ とその値からの関数値の残差をxの関数 $Z(x^{(i)})$ で表している。ここで関数Z(x)を確率過程モデルで表現することにする。すなわち $Z(x^{(i)})$ に対して、次の確率的性質を持つと仮定する。

$$Z \sim N(0, \sigma_Z^2) \tag{2.2}$$

$$\operatorname{Corr}[Z(\boldsymbol{x}^{(i)}), Z(\boldsymbol{x}^{(j)})] = e^{-d(\boldsymbol{x}^{(i)}, \boldsymbol{x}^{(j)})}$$

(2.3)

$$d(\boldsymbol{x}^{(i)}, \boldsymbol{x}^{(j)}) = \sum_{h=1}^{k} \theta_h |x_h^{(i)} - x_h^{(j)}|^{q_h} \ (\theta_h \ge 0, q_h \in [1, 2])$$

(2.4)

式 (2.2) は各点における残差項 Zが平均値 0,分散  $\sigma_Z^2$  の正規分布であることを示す。式 (2.3),(2.4) は,各点間の Z の相関関数を定義している。ここで Corr は 2 つの確率変数の相関を取るものとする。これらの相関関係の性質は後ほど説明する。

式(2.1)のモデルをそのまま統計解析の結果得られる目的関数に適用するには問題がある.これは、計算機内で統計的な解析を行なう際に不可避な誤差が、目的関数に含まれるためである.式(2.1)にはこのような誤差が考慮されておらず、新たに誤差を表す項の追加が必要である.そこで、用いるモデル式は次式のようになる.

$$y(\boldsymbol{x}^{(i)}) = \mu + Z(\boldsymbol{x}^{(i)}) + \epsilon(\boldsymbol{x}^{(i)})$$

(2.5)

式 (2.5) で追加された  $\epsilon(x)$  が雑音を表す項である。雑音項  $\epsilon(x)$  に対して、次の確率的性質を持つと仮定する。

$$\epsilon \sim N(0, \sigma_{\epsilon}^2) \tag{2.6}$$

$$\operatorname{Corr}[Z(\boldsymbol{x}^{(i)}), \epsilon(\boldsymbol{x}^{(j)})] = \operatorname{Corr}[Z(\boldsymbol{x}^{(i)}), Z(\boldsymbol{x}^{(j)})] = 0$$

(2.7)

式 (2.6) は雑音項が平均値 0,分散  $\sigma_{\epsilon}^2$  で正規分布をすることを,式 (2.7) は  $\epsilon$  がすべての観測点の Z とも,また他の観測点の  $\epsilon$  とも相関を持たないことを表す.

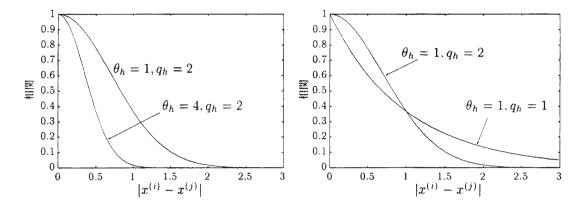

図 2.1: 一次元の場合の Z の相関関数

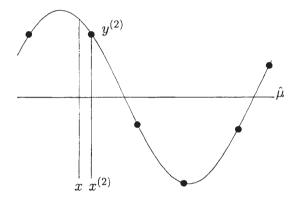

図 2.2: 確率過程モデルの性質

ここで、Zの確率的性質について説明する.相関関数は式(2.4)による一般化した距離の関数で表されている.ここで図 2.1 に 1 次元での相関関数を示す.式(2.4)の距離の関数として相関関数を図示している.ここでは,異なるパラメータ  $q_h$ , $\theta_h$  において,相関関数の変化を示している.図 2.1 (左)から分かるように, $\theta_h$  は確率変数 Z の活性をあらわす.つまり  $\theta_h$  が大きいほど活性が高く,距離に対して相関の減衰が速い.すなわち,観測点から少し遠ざかるだけで無関係に値をとるものと解釈される.つまり,起伏の激しい曲面がこれに相当する. $q_h$  は曲面の滑らかさを表すパラメータで  $q_h=2$  のときもっとも滑らかな曲面となる.

次に確率過程モデルの直観的な説明を行なう。図 2.2 にその概念を示す。図中の点 $x^{(2)}$  の近傍の点x での推定を考える。図からも明らかなように $x^{(2)}$  における値 $y^{(2)}$  は推定した $\hat{\mu}$  から正の方向に離れれているため,残差の項Z は正の値をとる。先ほどのZ の相関関数の性質をから,相関が及ぶ距離にある点は観測点と関連した値の「ふるまい」を見せる。したがって,近傍の点x の値を考えると $x^{(2)}$  での残差の値同様。正の値を取ることが考えられる。

以上で確率過程モデルの性質の説明を終り、次に観測データとモデルから、ある点 でのシミュレーション値の推定方法を説明する、確率過程モデル、式 $(2.2) \sim (2.4)$ が既知であるとして、x における関数値の推定値 y(x) を考える。推定方法の詳細は 文献 [50] に述べられており、ここでは推定式のみを次の式 (2.8) で与える $^1$ .

$$\hat{y}(\boldsymbol{x}) = \hat{\mu} + \boldsymbol{r}^T \boldsymbol{R}^{-1} (\boldsymbol{y} - \mathbf{1}\hat{\mu})$$

(2.8)

ここで.

$$R_{ij} = \operatorname{Corr}[\boldsymbol{x}^{(i)}, \boldsymbol{x}^{(j)}]$$

$r_i = \operatorname{Corr}[\boldsymbol{x}, \boldsymbol{x}^{(i)}]$

$\boldsymbol{1} = (1, 1, \dots, 1)^T$

である. また、 $\hat{\mu}$ は $\theta$ 、qから求まる $\mu$ の推定値であり、具体的な推定法は後で述べ る.式(2.8)を見れば、各サンプル点同士の相関、推定する点での相関、データと 平均値の残差を考慮して推定していることがわかる。推定値は確率変数より得られ た値であるため、推定値も確率変数となりその分散値も計算できる. これは次式の ようになる。

$$s^{2}(\boldsymbol{x}) = \sigma_{Z}^{2} \left[ 1 - \boldsymbol{r}^{T} \boldsymbol{R}^{-1} \boldsymbol{r} + \frac{(1 - \boldsymbol{1}^{T} \boldsymbol{R}^{-1} \boldsymbol{r})^{2}}{\boldsymbol{1}^{T} \boldsymbol{R}^{-1} \boldsymbol{1}} \right]$$

(2.9)

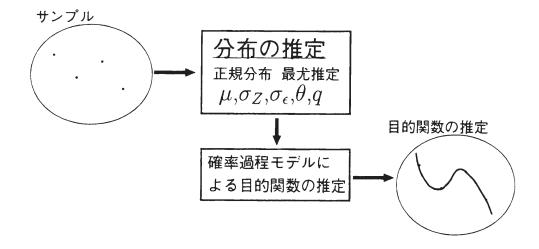

次に、確率過程モデルにおいて、データの確率的な性質をどのように知り得るの かを説明する. 言い換えると、このモデル中の $\mu$ ,  $\sigma_Z$ ,  $\sigma_\epsilon$ ,  $\boldsymbol{\theta} = (\theta_1, \dots, \theta_k)^T$ ,  $\boldsymbol{q} =$  $(q_1,\ldots,q_k)^T$  という 2k+3 個の未知のパラメータをどのように求めるかである. こ こでは最尤推定法[56]により求めることにする. 観測値は確率過程のモデル項 Zと 雑音の項 $\epsilon$ の和であり、それぞれ正規分布を仮定しているので、観測データも正規分 布をとる.

$$\mathbf{y} \sim N(\mu, \sigma_0^2 \mathbf{R}_0)$$

(2.10)

$$\sigma_0^2 = \sigma_Z^2 + \sigma_\epsilon^2 \tag{2.11}$$

$$\sigma_{o}^{2} = \sigma_{Z}^{2} + \sigma_{\epsilon}^{2}$$

$$\mathbf{R}_{o} = \frac{1}{\sigma_{o}^{2}} (\sigma_{Z}^{2} \mathbf{R} + \sigma_{\epsilon}^{2} \mathbf{I})$$

$$(2.11)$$

I は  $n \times n$  の単位行列であり、 $\sigma_o$ 、 $R_o$ は観測データの分散と相関行列である. した がって尤度関数 L は次式で与えられる.

$$L(\boldsymbol{\theta}, \boldsymbol{q}, \mu, \sigma_{o}) = \frac{1}{(2\pi)^{n/2} (\sigma_{o}^{2})^{n/2} |\boldsymbol{R}_{o}|^{1/2}} \exp\left[-\frac{(\boldsymbol{y} - \boldsymbol{1}\mu)^{T} \boldsymbol{R}_{o}^{-1} (\boldsymbol{y} - \boldsymbol{1}\mu)}{2\sigma_{o}^{2}}\right]$$

(2.13)

$\mu$ ,  $\sigma_0$  は  $R_0$  (すなわち  $\theta$ , q) が与えられているとすると、最尤推定により以下のよ うに推定できる.

$$\hat{\mu} = \frac{\mathbf{1}^T \mathbf{R}^{-1} \mathbf{y}}{\mathbf{1}^T \mathbf{R}^{-1} \mathbf{1}} \tag{2.14}$$

図 2.3: パラメータ, 関数値推定手順

$$\hat{\sigma_o}^2 = \frac{(\boldsymbol{y} - \mathbf{1}\hat{\mu})^T \boldsymbol{R}_o^{-1} (\boldsymbol{y} - \mathbf{1}\hat{\mu})}{n}$$

(2.15)

そこで、これらの値を $\mu$ ,  $\sigma$  として使うことで、式 (2.13) は $\theta$ ,  $\sigma$  の式になる、 $\theta$ . q は式(2.13) を目的関数とする数値的最大化問題を解くことにより求めることがで きる. さらに式 (2.13) の log をとることで最大化問題は次のように表される.

$$\max_{\boldsymbol{\theta}, \boldsymbol{q}} -n \log(\hat{\sigma_0}^2) - \log(\det \boldsymbol{R_0})$$

(2.16)

ここまでのパラメータの推定と関数値の推定の手順を図2.3にまとめる。

なお、パラメータの推定で最も計算コストがかかるのは $R_0$ の逆行列と行列式の 計算である.  $\mathbf{R}_{o}$ の次元はサンプル数nで決まるため多くのサンプルをとると計算時 間が増加する。また、最適化自体も推定するパラメータの数に依存するので、応答 曲面を描く空間の次元 k が増加すると推定の計算コストも増える.

#### 2.2.2 大域的最適化手法

応答曲面を使った最適化手法を説明する. 先ほども説明した通り. 応答曲面から 得られる推定値はばらつきが存在するため、応答曲面から推定値の最小点を探すだ けでは不十分である、つまり、精度の向上を行ない推定値の分散を減らすとともに、 最適値を見つけなければいけない.このために2つの戦略にそって最適化を行なう. 一つは大域的に最小値が存在する確率が高い位置を探索することである。最小値の 存在しそうな位置は、応答曲面が最小値であるか、その位置での応答曲面のばらつ

$<sup>^1</sup>$ ここで用いているモデルは雑音の項 $\epsilon$ が追加されているが、この項は値の推定に影響しないことが確 認できる. したがって, 文献 [50] の推定式をそのまま用いることができる.

きが大きく不確定要素の多いところである.次の戦略は大域的に見つけた最小値付近で局所的に応答曲面の精度をあげてより良い解を見つけることである.最適化アルゴリズムではこれらの戦略をバランス良くとることで効率的な最適化を目指す必要がある.

上記の目的を達するため最小値の改善の度合を表す指標を作り、これを最大にする点に新たにサンプル点に追加することで、「大域的」、「局所的」の 2つの戦略をバランス良く進める手法が文献 [47] で提案されている。まず、改善の指標の説明をおこなう。サンプルでの観測値の最小値を  $f_{\min}$  とする。点x における推定値は確率変数であり、これを Y とすると、この点における改善関数は  $I = \max(f_{\min} - Y, 0)$  で与えられる。つまり、Y が  $f_{\min}$  より小さければその差が関数値となり、そうでないなら 0 となる。Y は確率変数なのでこの関数の期待値がこの点で期待できる最小値の改善量となる。

$$E[I(x)] = E[\max(f_{\min} - Y, 0)]$$

(2.17)

式 (2.17) で定義される関数を、改善期待関数と呼ぶことにする。なお、 $Y \sim N(\hat{y}, s^2)$   $(\hat{y}$  は式 (2.8) で与えられる推定値)であるから、積分計算をすることで式 (2.17) は次のようになる。

$$E[I(\boldsymbol{x})] = (f_{\min} - \hat{y})\Phi\left(\frac{f_{\min} - \hat{y}}{s}\right) + s\phi\left(\frac{f_{\min} - \hat{y}}{s}\right)$$

(2.18)

ここで、 $\Phi$ と $\phi$ はそれぞれ正規分布の分布関数と密度関数である。最小値の改善を最も見込める点は最大化問題  $\max_{\boldsymbol{x}} E[I(\boldsymbol{x})]$  により求めることができる。すなわち、この問題の解がサンプル点を追加する点となる。

以上から、最適化のアルゴリズムは次のようになる.

- 1. 応答曲面を描くためにサンプル点を取り、シミュレーションを行なう. サンプル点のシミュレーション値の最小値を  $f_{min}$  とする.

- 2. サンプル点とシミュレーション結果を使い、応答曲面モデルを構築する.

- 3.2で生成した応答曲面の精度を検証する、十分でないなら停止する、

- 4. E[I(x)] の最大値  $I_{\max}$  とこれを与える点  $x_{\max}$  を求める。もし  $|I_{\max}/f_{\min}| < \epsilon_{\mathrm{tol}}$  ならば停止する( $\epsilon_{\mathrm{tol}}$  は定数)。最小値は  $f_{\min}$  となる。

- $5. x_{\min}$  をサンプル点に追加. シミュレーションを追加.  $f_{\min}$  を求め直す. 2へ.

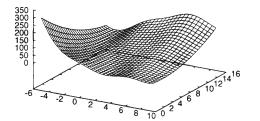

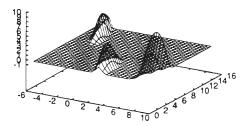

以上の手順で困難なのは手順4における最大値を求めるところである.ここで,最適化の評価に用いられるBranin 関数について,あるサンプルにおいて改善期待値関数を計算した結果を図2.4に示す.この図から分かるように,ある特定の領域だけ正の値を持ち,それ以外の部分はおよそ0になる.このような関数の最大値を通常の最適化手法で求めることはできない.そこで文献[47]では分枝限定法を用いた方法が提案されている.しかし,この手法を試したところ非常に計算コストがかかることが分かった.そこで,ここでは探索空間中にランダムに点を選び改善期待関数を計算し、その中で最大の値を初期値に選び非線形最大化を行なった.この手法によ

図 2.4: Branin 関数 (左) と改善期待値関数 (右)

ると、SUN Ultra 60上で数秒程度の時間で最大値が得られる。ただし、こうして得られた解が必ずしも最適値である保証はないので数回同じ過程を繰り返し、得られた最大値の中で最も大きい値を選択した。

#### 2.2.3 確率過程モデルの適用例

最適化の評価関数として有名な Branin 関数 [57] を用い、応答曲面生成とこれを用いた最適化の実験を行なった。Branin 関数は以下の式で表される。

$$F = a(y - bx^{2} + cx - d)^{2} + h(1 - f)\cos x + h$$

(2.19)

$a = 1, b = 5.14/(4\pi^2), c = 5/\pi, d = 6, h = 10, f = 1/8\pi, x \in [-5, 10], y \in [0, 15]$

曲面の形状を図2.4(左)に示す.図から分かるように、多項式モデルでは精度の良いあてはめを行なうことができない.

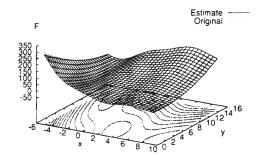

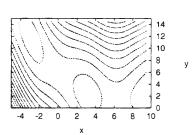

サンプル点はラテン超立方 [7] に従い 21 点とった。生成した応答曲面を図 2.5 に示す。図 2.5 (左)に元の曲面と推定した曲面を重ねて示している。両者の誤差はわずかであり,ほぼ一致しているように見える。また,両者の等高線を図 2.5 (右)に示している。この図からも,推定曲面の精度の良さを見ることができる。生成時間に要した時間は SUN Ultra 60 上で 77 秒,応答曲面の精度を表す  $R_{PRESS}^2$  は 0.9999 であり精度の良いあてはめを行なうことができた。( $R_{PRESS}$  の定義は付録 A.2 を参照。)

次に最適化実験を行なった。今回の手法では乱数を使った探索を用いているので、 試行ごとに異なる結果が得られる。実験は3回試行し、それらの結果を表2.1に示 す、いずれの試行も真値に近い値が得られている。

図 2.5: Branin 関数と応答曲面(左)とその等高線(右)

表 2.1: Branin 関数の最適化結果

|   | 確率過程   | 程モデルに  |        | 真値     |        |     |

|---|--------|--------|--------|--------|--------|-----|

| • | $x_1$  | $x_2$  | y      | $x_1$  | $x_2$  | y   |

|   | 3.1427 | 2.3906 | 0.0113 |        |        |     |

|   | 3.1299 | 2.4336 | 0.0201 | 3.1416 | 2.2750 | 0.0 |

|   | 3.1296 | 2.4342 | 0.0203 |        |        |     |

### 2.3 歩留まり最適化手法

ここまでで説明してきた最適化手法の歩留まり最適化問題への適用を考える. そのために、ここでは歩留まり最適化問題の目的関数について説明する.

今回の提案モデルは雑音を考慮しているが、最適化を行なうには目的関数となる 歩留まり指標は雑音をなるべく抑えた方が良い。例えば、モンテカルロ解析により 得られた歩留まりを目的関数に用いると、推定した歩留まりにばらつきが存在して おり、最適化には好ましくない。そこで、ここでは、ばらつきの影響を受けにくい、 品質管理の指標である  $C_{\rm p}$ – $C_{\rm pk}$  を元にしたもの [58] を目的関数として用いる。

目的関数の定義は以下の通りである。今、回路特性が $n_c$  個存在するとして、回路の特性をベクトル $\mathbf{c} = (c_1, c_2, \dots, c_{n_c})$ で表す。i 番目の特性に対して、歩留まりの指標を以下のように定義する。

$$\Psi_{i}^{L}(\boldsymbol{d}) = (1 - \lambda) \frac{S_{i}^{U} - S_{i}^{L}}{6\sigma_{c_{i}}} + \lambda \frac{\frac{S_{i}^{U} + S_{i}^{L}}{2} - \bar{c}_{i}}{3\sigma_{c_{i}}}$$

(2.20)

$$\Psi_{i}^{L}(\boldsymbol{d}) = (1 - \lambda) \frac{S_{i}^{U} - S_{i}^{L}}{6\sigma_{c_{i}}} + \lambda \frac{\bar{c}_{i} - \frac{S_{i}^{U} + S_{i}^{L}}{2}}{3\sigma_{c_{i}}}$$

(2.21)

$$\Psi_i(\boldsymbol{d}) = \min\{\Psi_i^{\mathrm{U}}(\boldsymbol{d}), \Psi_i^{\mathrm{L}}(\boldsymbol{d})\}$$

(2.22)

ここで d は設計変数, $S_i^{\rm L}$ , $S_i^{\rm L}$  は i 番目の仕様の上限と下限, $\lambda$  は  $0 \le \lambda \le 1$  なる定数である.式(2.20),(2.21)の第 1 項はばらつき具合に関するものであり,第 2 項は中心値に関する項である.ばらつき(分散)が小さいほど,平均値が仕様の中心に近いほどこれらの値は大きくなる.すなわち, $\Psi_i(d)$  の値が大きいほど望ましい回路特性といえる.

n<sub>c</sub> 個の仕様全体に対しては、歩留まり指標を次式で定義する.

$$\Psi_i(\boldsymbol{d}) = \max_{\boldsymbol{d}} \min_{i=1,2,\dots,n_c} \{ \Psi_i(\boldsymbol{d}) \}$$

(2.23)

次に式 (2.20) , (2.21) の計算方法を説明する. 計算のためには特性値の平均  $\bar{c}$  と分散  $\sigma_{c_i}$  が必要である. これらの計算をモンテカルロ解析を通じて行なうと雑音が大きくなる. そこで,各設計点 d において局所応答曲面を生成し,これを利用する. この局所応答曲面は先に述べた通り多項式によるもので十分表現できる. ここでは,1次の多項式を用いる. 平均値  $\bar{c}$  は応答曲面の定数項に等しい. 分散は次の公式(Transmission of Moments Formula)により求めることができる [6].

$$\sigma_{c_k} = \sum_{i=1}^{n_p} \sum_{j=1}^{n_p} \frac{\partial c_k}{\partial p_i} \frac{\partial c_k}{\partial p_j} \operatorname{Cov}(p_i, p_j)$$

(2.24)

ここで、Cov は共分散を取る関数とする。また、 $p_1, p_2, \ldots, p_{n_p}$  は、ばらつきの元であるプロセスの物理パラメータ(変動変数)とする。この公式は、回路特性の分散を変動変数の共分散で表現するものである。変動変数の共分散は測定より既知であ

図 2.6: 2 段増幅オペアンプ回路

り、回路特性の変動変数に対する感度  $\partial c_k/\partial p_i$  も局所応答曲面より求めることができるので、回路特性の分散を得ることができる。

以上のように定義される目的関数を用いた場合、計算コストで支配的となる要因をまとめておく、まず、最適化のはじめの段階での確率モデルによる応答曲面の生成では、サンプル点における目的関数の計算とモデルのパラメータ推定に計算コストがかかる。また、最適化の過程における追加サンプルでの目的関数の計算も計算コストの要因となる。ここで、各設計点での目的関数の計算に、1次多項式による局所応答曲面の生成が必要なため、回路シミュレーションを複数回実行する必要がある点に注意する。

## 2.4 実験

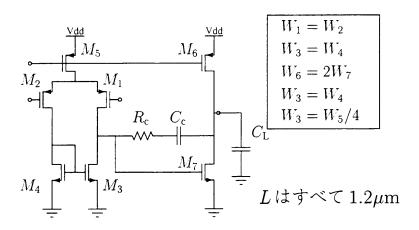

ここでは実験として提案手法をオペアンプに適用する.

使用した回路は 2 段増幅のオペアンプで,回路図を図 2.6 に示す.トランジスタ幅の変数名を,図 2.6 中の素子に割り振った番号に W をつけて定義する.すべてのトランジスタのゲート長は  $1.2\mu\mathrm{m}$  で固定する.この回路の設計変数は  $W_1$ ,  $W_5$ ,  $W_7$ ,  $C_\mathrm{c}$ ,  $R_\mathrm{c}$ である.他の寸法は図 2.6 中に示した制約条件で決定される.設計変数の定義域を表 2.2 に示す.これらの変数は,最適化においては -1 から 1 を定義域とする変数へと規格化を行なう.規格化式を表 2.2 にあわせて示す.また,回路の仕様はスリューレート,直流利得,単位利得周波数,位相余裕に対して表 2.3 のように定めた.次に適用するプロセスと変動条件について述べる.適用するプロセスは  $0.6\mu\mathrm{m}$  CMOS プロセスで,変動変数にトランジスタのパラメータの  $\Delta L$ ,  $\Delta W$ ,  $T_\mathrm{ox}$ ,  $V_\mathrm{th}$ ,  $R_\mathrm{sh}$  を選んでいる.それぞれ,実チャンネル長のマスク長からのずれ,実チャンネル幅のマスク幅からのずれ,酸化膜厚.しきい値電圧.ドレイン・ソースの寄生抵抗

表 2.2: 設計変数の範囲

|                                   |     |     | · · · · · · · · · · · · · · · · · · · |

|-----------------------------------|-----|-----|---------------------------------------|

| 設計変数                              | 下限  | 上限  | 規格化式                                  |

| $W_1 [\mu \mathrm{m}]$            | 20  | 220 | $(W_1 - 120)/100$                     |

| $W_5 \; [\mu \mathrm{m}]$         | 4   | 104 | $(W_5 - 54)/50$                       |

| $W_7 \; [\mu \mathrm{m}]$         | 50  | 250 | $(W_7 - 150)/100$                     |

| $C_{ m c}~[{ m pF}]$              | 1   | 11  | $(C_{\rm c} - 6)/5$                   |

| $R_{	extsf{c}}\left[\Omega ight]$ | 100 | 1k  | $(R_{\rm c} - 550)/450$               |

表 2.3: オペアンプの仕様

| <del></del>    | 下限   | 上限   |

|----------------|------|------|

| スリューレート [V/μs] | 5.0  | 10.0 |

| 直流利得 [dB]      | 70.0 | 80.0 |

| 単位利得周波数 [MHz]  | 10.0 | 12.0 |

| 位相余裕 [°]       | 65.0 | 70.0 |

#### である.

2.4. 実験

各設計点における目的関数の計算コストは、ほぼ 1 次の応答曲面モデルの生成に必要な回路シミュレーションで占められる。このシミュレーション回数は変動変数の数に依存する。今回の実験では変動変数が NMOS と PMOS 合わせて 10 個あり、実験計画として直交計画の一種である部分実施の要因計画 [59] を適用し、応答曲面の生成に 16 回のシミュレーションを要した。

最適化は、式 (2.23) で表される目的関数の確率過程モデルによる応答曲面の生成から始める。設計変数 5 個に対して、サンプル点を 50 個とった。パラメータの推定のために最適化手法として Nelder と Mead による滑降シンプレックス法 [60] を用いている。応答曲面の生成時間はシミュレーションにかかる時間に約 35 分、応答曲面生成にかかる時間が約 31 分であった。精度は  $R_{PRESS}^2$  は 0.999 であった。この時のパラメータ p、 $\theta$  の推定値を表 2.4 に示す。表から分かる通り  $R_c$  の  $\theta$  の値が小さいこ

表 2.4: 確率過程モデルパラメータの推定値

| 設計変数             | q    | $\theta$               |

|------------------|------|------------------------|

| $\overline{W_1}$ | 1.78 | $8.66 \times 10^{-02}$ |

| $W_5$            | 1.43 | $1.15 \times 10^{-01}$ |

| $W_7$            | 1.80 | $1.58 \times 10^{-02}$ |

| $C_{ m c}$       | 1.99 | 1.09                   |

| $R_{ m c}$       | 1.75 | $0.34 \times 10^{-06}$ |

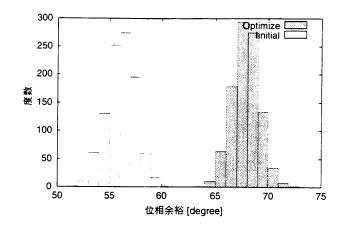

図 2.7: 位相余裕の最適化前と後のヒストグラム

とがわかる.この変数は生成した応答曲面上では特性に影響を与えないパラメータであるため、無視することにする.

次に、得られた確率過程モデルによる応答曲面をもとにして最適化アルゴリズムを適用した。最適化過程で31個のサンプルの追加を行ないアルゴリズムは停止した。この過程にかかる時間は約32分であった。初めの応答曲面の生成から最適化終了までのすべての過程でかかった時間は98分であった。得られた設計変数を使ってモンテカルロ解析を行なった。その結果、概略設計時の歩留まりが0%であったものが、93.8%になった。この時の位相余裕のヒストグラムを最適化前の概略設計時のものとあわせて図2.7に示す。

#### 2.5 まとめ

この章では小規模な回路ブロックの最適化を行なった。用いた手法は確率過程モデルによる最適化手法である。また、階層設計に結びつけるために局所応答曲面を目的関数の計算に用いている点も特徴に挙げられる。

オペアンプの実験で最適化に要した時間はおよそ 100 分程度で,実用的な計算コストで小規模回路の最適化が行なえた.特に第4章で提案する設計手法に従うと,回路仕様の変更と最適化の繰返しが想定される.このような場合,初期の応答曲面生成に必要な回路シミュレーション結果はそのまま新たな最適化に利用することができるので,この部分の計算コストは削減できる.すなわち,本論文で提案する階層的設計手法に適した最適化手法であると考える.

実用性ならびに階層設計への整合性の観点からは十分であると言えるが、最適化 手法にはまだ改善の余地がある。まず、確率過程モデルのパラメータの推定に、最 大化手法として滑降シンプレックス法を用いている。この方法は、収束性が悪くこ の問題に適したより収束性の高い手法を適用すれば計算コストの削減が期待できる。 次に、サンプル点の追加のための改善期待関数の最大化問題の、高速かつ正確な解 法が必要である。先にも述べたように、分枝限定法では計算コストがかかり過ぎて しまう。また、現在の乱数を用いた方法では、サンプル追加の点が確率的に決まっ てしまい一定の最適値に到達しない。したがって、この最大化手法の改良を改善期 待関数の形も含めて検討する必要がある。

最適化手法とは別に、歩留まりを表す指標も最適解に大きな影響を及ぼす。今回用いた $C_p$ - $C_{pk}$ をもとにした目的関数は、最適値付近でなだらかな形状をしており、最適化候補となる点が広い範囲に広がっている。これが、サンプル点の追加回数が多くなってしまった原因と考えられる。また、目的関数値と歩留まりが必ずしも一致しない場合があった。よりこの手法に適した目的関数の検討が必要である。

## 第3章

## 階層的統計解析

#### 3.1 はじめに

第2章では小規模回路の統計解析と、これを元にした歩留まり最適化手法について述べた。これに対して、この章と続く第4章では大規模回路の統計的解析と最適化に取り組む。まずこの章では、第1章で示した階層モデルを使った統計解析について述べる。この解析は第1章で述べたボトムアップ解析手法である。ここで、大規模化で問題になる統計解析の計算コストの削減を、中間モデルによる統計的パラメータと応答曲面モデル<sup>1</sup>を使い実現する。この手法により、システム特性をプロセスの物理パラメータと明示的につなぎ、物理特性によりシステム特性がどのように変化するかを知ることができる。逆に、プロセス側からはシステム歩留まりを得るためのプロセス特性への制約事項を知ることができる。

本章の構成を述べる. まず 3.2 節で本章で用いる手法の概略について説明する. 続く 3.3 節では階層間をつなぎ統計情報の伝達を担うモデルと伝達方法を説明する. 3.4 節では,提案手法を使った実験を行なう. 実験では PLL を題材に精度面と計算コスト面を評価する. また,モンテカルロ解析,ワーストケース解析,感度解析への応用も示す.

## 3.2 大規模回路の統計解析

第2章で述べた方法は、主に小規模な回路ブロックを対象とした解析であり、大規模回路にそのまま適用することはできない。なぜならば、大規模回路をSPICE系のシミュレータにより現実的な計算時間で解析することができないからである。さらに、統計解析は回路シミュレーションを多数実行する必要があり、さらに問題を困難なものにしている。そこで、この問題を解決する方法として、第1章で述べた階層的手法を取り上げる。

<sup>1</sup>これらのモデルの詳細は、それぞれ付録 A.1、A.2 を参照.

階層的統計解析手法は、ばらつきの根本となるプロセス階層の統計情報から、図 1.3 に示した階層構造の階層間をつなぐことで、システム階層の特性の統計情報を得る。ここで、各階層間の統計情報をつなげる手段は、計算コストが十分小さくなければいけない。この目的のために、中間モデルと応答曲面モデルを用いる。この方法を用いることで、プロセス階層の物理パラメータである  $\Delta L$  (実チャンネル長のマスク長からのずれ)や  $T_{\rm ox}$  (酸化膜厚)などを使って、システム階層の特性を陽的に記述することができ、プロセス階層の統計情報をシステム階層まで伝達することができる。

これまでに、階層構造を使った統計解析手法がいくつか提案されており [37-40]、階層構造を用いた統計解析の実現方法が論じられている。これらの方法はすべて MOSFET のデバイスのモデルパラメータのばらつきモデルを用いて、デバイス階層 のばらつきからシステム階層のばらつきを表現していた。しかし、これらは物理パラメータとシステム特性の関係が十分につかめない欠点がある。そこで、この研究では階層構造を更に下へとひろげ、プロセス階層の物理パラメータのばらつきを元にした階層的統計解析の実現を提案する。この方法により、物理パラメータのばらつきがシステム階層の特性にいかに影響を及ぼすかを知ることができる。

この章におけるもう一つの目的は、階層的な統計解析手法により、解析精度をどの程度期待できるかを実用的な観点から評価することにある。特に、階層構造における回路階層とシステム階層間の関係付けは言語記述を用いた動作シミュレーションを利用するため、言語記述に用いたモデルの精度を確認することが必要である。評価は、システム全体をSPICE系のシミュレータで解析した結果との比較により行なう。実用的観点から意味のある解析を目指すために、ここでは回路例としてPLL(Phase Locked Loop)を取り上げる。PLLをアナログ記述言語の一つである Verilog-AMSで記述し、このモデルの統計解析への適合性と実用性を、計算コストと精度の面から評価を行なう。

## 3.3 階層的統計解析手法

本章で取り扱う階層モデルは、第1章で説明したものである。これを図3.1に再掲する。各階層―プロセス、デバイス、回路、システム―のパラメータは、プロセスレベルの物理パラメータを端緒として変動している。階層的統計解析では最下層のプロセス階層から始めて、隣り合う階層間のパラメータの関係づけを行なう。統計情報はこのように関係づけられた階層間を一つづつ受渡しすることで最上位層まで伝達される。

ここで、階層間で受渡しする統計情報の内容に注意する必要がある。例えば、プロセス階層の物理パラメータから、デバイス階層のモデルパラメータへ統計情報を受渡しする際、特性が最も良くなる場合と、悪くなる場合の2通りパラメータ(ワースト/ベストケースパラメータ)を統計情報とすることがよく行なわれる。しかし、

図 3.1: 統計解析における階層構造

この方法で各階層ごとにワースト/ベストケースの解析を繰り返しても、システム階層の特性の正確なワースト/ベストケース値を求めることはできない。なぜなら、受渡しに使われる統計情報には、回路階層における回路ブロック間の相関などの統計情報が途中で抜け落ちており、システム階層まで運ばれる統計情報は現実のばらつきを表すものでなくなっているからである。また、この方法の別の問題として、システム特性がプロセス階層の物理パラメータの変動から受ける影響の大きさを知ることができないことも挙げられる。

以上の考察から、プロセス階層における物理的パラメータの統計的情報を、システム階層まで情報量を落すことなく伝達することが、正確な解析を行なうためには重要である。また、こうすることにより、システム階層の特性のばらつきを解析するだけでなく、システム特性が仕様を満たすためのプロセスの制約事項を明らかにすることが可能である。

本研究では、統計情報の受渡しの方法として中間モデルと応答曲面モデルを用いる。中間モデルにより、物理パラメータのばらつき(統計情報)を使ってデバイス階層のモデルパラメータを表現する。応答曲面モデルは、回路階層とシステム階層の特性をそれぞれの1つ下の階層の特性と結びつける目的で用いられる。応答曲面をつなげることで、デバイス階層からシステム階層へと統計情報を橋渡しすることが可能となる。図3.1にこれらのモデルがどのように使われているかを示している。

次に応答曲面をつなぎ合わせることで、いかにして統計解析を行なうかを示す.ここでの応答曲面モデルは多項式によるものを用い、回路特性を物理パラメータの関数で、システム特性を回路特性の関数でそれぞれ表す. 応答曲面モデルの多項式としては1次式もしくは2次式を使う.

35

今, システム中で注目する回路特性をベクトル  $\mathbf{c}=(c_1,c_2,\ldots,c_{n_c})^T$  で表す. この特性をプロセス階層の物理パラメータ  $\mathbf{p}=(p_1,p_2,\ldots,p_{n_p})^T$  の応答曲面モデル  $\mathrm{rsm}_{p\to c}$  で表す.

$$c_i = \operatorname{rsm}_{p \to c}(\mathbf{p})$$

=  $b_0 + \sum_{i=1}^{N} b_i p_i + (\text{higher order terms}).$  (3.1)

同様にシステム特性  $\mathbf{s} = (s_1, s_2, \dots, s_{n_s})^T$  を  $\mathbf{c}$  を使った応答曲面モデル  $\mathbf{rsm}_{c \to s}$  で表し、更に式 (3.1) を使うと次のようになる.

$$s = \mathbf{rsm}_{c \to s}(\mathbf{c}) = \mathbf{rsm}_{c \to s}(\mathbf{rsm}_{p \to c}(\mathbf{p}))$$

$$\equiv \mathbf{rsm}_{p \to s}(\mathbf{p}). \tag{3.2}$$

式 (3.2) の  $\mathbf{rsm}_{p\to s}$  は物理パラメータとシステム特性をつなぐ応答曲面である. 式 (3.2) を使うことで、物理パラメータの統計情報からシステム特性の統計情報を得ることができる.

ここで、システム特性をプロセス階層の物理パラメータで表現する利点を示す応用例として、感度解析を挙げる。感度解析により、物理パラメータがシステム特性へ与える影響の大きさを評価できる。ここでの注意は、互いに相関を持つパラメータに対する感度を比較しても得られる情報は少ないということである。なぜなら、これらの相関を単独に見た場合大きな感度を持っていても、別のパラメータの感度がこれを打ち消すことがあるからである。互いに相関を持たないパラメータに対する感度を計算するために、物理パラメータの主成分分析により得られる相関をもたないパラメータxを使って、式 (3.2) を書き直す(付録 A.1 式 (A.1) 参照)。

$$s = \operatorname{rsm}_{p \to s}(U\Lambda^{1/2}x) \equiv \operatorname{rsm}_{x \to s}(x)$$

(3.3)

ここで、 $\mathbf{rsm}_{x\to s}$ は無相関なパラメータ x とシステム特性 s をつなぐ関数である.式 (3.3) を用い無相関なパラメータに対するシステム特性の感度解析を行ない, $\partial s_k/\partial x_i$  を計算する.この結果を用いると物理パラメータのシステム特性に及ぼす影響を調べることができる.このために以下に示す展開を行なう.

$$\frac{\partial s_k}{\partial x_i} = \sum_j \frac{\partial s_k}{\partial p_j} \cdot \frac{\partial p_j}{\partial x_i} \tag{3.4}$$

どの物理パラメータがシステム特性に影響を及ぼすかを知るには以下の手順に従う.

- 1. 式 (3.4) 左辺の感度解析の結果から、感度の大きい $x_i$  に注目する.

- 2. 注目する  $x_i$  に対して式 (3.4) 右辺の展開を行なう.

- 3. 展開項の中で大きな値を取る物理パラメータが、システム特性に大きな影響を持つと判断できる.

## 3.4 実験

以上で述べた階層的統計解析手法の有効性を実験により検証する.まず,3.4.1節で実験で取り上げるPLL回路の機能記述モデルについて説明する.次に3.4.2節で機能記述モデルの解析精度の評価を行なう.最後に3.4.3節で階層的統計解析の実験を行なう.ここでは,実用性の検証のためこれらの解析の計算コストの評価を行なった.また,モデルの精度面の検証も行なうため,システム全体を素子記述しSPICEにより解析した結果との比較も行なっている.

なお、この実験では  $0.6\mu m$  CMOS プロセスを用いる。トランジスタのモデルパラメータとして、付録 A.1 で説明した抽出手法により生成した統計的モデルパラメータを用いる。ばらつきの元として考慮する物理パラメータは、実チャンネル長のマスク長からのずれ  $\Delta L$ 、実チャンネル幅のマスク幅からのずれ  $\Delta W$ 、酸化膜厚  $T_{\rm ox}$ 、しきい値電圧  $V_{\rm th}$ 、ドレイン・ソースの寄生抵抗  $R_{\rm sh}$  である。

#### 3.4.1 PLL の機能記述モデル

今回の実験では階層設計の例として PLL を取り上げる。また、ロックアップ時間 を解析の対象とした。ロックアップ時間は PLL の出力周波数が 10MHz にロックした状態からステップ状の入力信号の変化に合わせて 50MHz ヘロックするのにかかる時間とする。

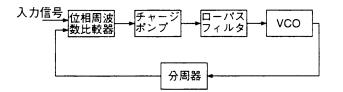

PLL は位相周波数比較器,チャージポンプ,ローパスフィルタ,電圧制御発振器 (Voltage Control Oscillator: 以下 VCO),分周器からなる.構成を図3.2に示す.各ブロックのモデルは Verilog-AMS を使って記述した.以下に各ブロックの機能記述モデルならびに回路特性の抽出方法を説明する.

チャージポンプ回路は,位相周波数比較器から出力される増加あるいは減少信号を入力として,増加信号が入力されているときは電流の吐き出しを,減少信号が入力されているときは吸い込みを行なう.これらの電流値を一定量 $I_{cp}$ としてモデル化する.また,出力端子の電圧がある限界値 $V_{lim}$ を越えると,回路を構成するトランジスタが飽和領域から外れるため,一定電流を供給できなくなる.そこで,チャージポンプの出力端子電圧—出力電流特性は,限界電圧までは一定電流値をとり,その電圧を越えると0へと直線的に減少する特性を仮定した.つまり区間線形によりこ

図 3.2: PLL の構成

れを表す、 $I_{cp}$ と $V_{lim}$ が機能記述の回路階層のパラメータとなる、SPICEの直流動作点解析により、これらの値は抽出できる。

VCO は入力電圧により発振周波数が変化する。この変化を直線で近似した。すなわち、このモデルでは直線の傾き(利得) $K_V$  が回路階層のパラメータとなる。利得 $K_V$  を抽出するためには、SPICE による過渡解析が数回必要である。解析結果から、電圧に対する発振周波数の変化を最小二乗法により直線で近似し、 $K_V$  を決定する。

位相比較器は、基準入力信号と PLL の出力信号を入力とし、これらの位相の関係によりチャージポンプ回路に増加、減少信号を出力する。また、分周器は入力信号の周波数を分周する。これらのブロックは論理回路により構成されており、機能は容易に言語記述することができる。さらに非理想的要素として、出力信号の遅延時間、立ち上り/立ち下がり時間をモデルに追加している。これらの値は過渡解析により抽出することができる。

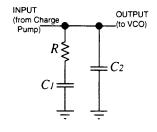

ローパスフィルタの構成は図 3.3 に示すとおり、抵抗、容量からなる。このような単純な構造をとるため、今回はローパスフィルタには機能記述を用いなかった.抵抗、容量を、図の通り R,  $C_1$ ,  $C_2$  とし、素子の接続記述を用いてシミュレーションする。3 次の極の影響を抑えるため、 $C_2$  は  $C_1$  の 10 分の 1 の値に設定する。このため設計に必要な変数は R と  $C_1$  である。

以上がPLLのモデル化である.ここで、どの回路特性が、システム特性であるロックアップ時間に大きな影響を及ぼすかを調べることにする.この結果を得ることで、影響の小さい回路特性は統計解析の際に無視することができ、計算コストの削減につながる.

制御理論より、PLLの過渡特性に次の2つのパラメータが重要な役割を果たす[61].

$$\omega_{\rm n} = \sqrt{\frac{I_{\rm cp}K_V}{2\pi NC_1}} \equiv \omega(\boldsymbol{c})$$

(3.5)

$$\zeta = \frac{R}{2} \sqrt{\frac{C_1 I_{\text{cp}} K_V}{2\pi N}} \tag{3.6}$$

これらは、それぞれ自然角周波数、ダンピング係数とよばれる。ロックアップ過程はこれらの値により決まる。式(3.5),(3.6) には回路特性パラメータ  $K_V$ ,  $I_{cp}$ , R,  $C_1$  が含まれている。そこで、これらのパラメータがロックアップ時間特性において

図 3.3: ローパスフィルタ

| ž |

|---|

| ž |

|       |                   |        | <del></del> |       |        |

|-------|-------------------|--------|-------------|-------|--------|

| 回路パラン | メータ               | 感度     | 回路パラ        | メータ   | 感度     |

| チャージ  | $I_{\mathrm{cp}}$ | -0.055 | 位相周波        | delay | -0.000 |

| ポンプ   | $V_{lim}$         | 0.000  | 数比較器        | rise  | 0.001  |

| VCO   | $K_V$             | -0.385 |             | fall  | -0.002 |

| ローパス  | R                 | -0.132 | 分周器         | delay | -0.001 |

| フィルタ  | $C_1$             | 0.111  |             | rise  | -0.000 |

|       | 1. 1.             |        |             | fall  | 0.000  |

主たる影響を及ぼすものと考えられる。このことを確認するために、ロックアップ時間の回路特性に対する感度解析を行なう。感度を特性間で比較するには、共通の尺度を用いる必要がある。そこで、次式で定義する正規化感度  $S_{ij}$  を用いることにする。

$$S_{ij} = \frac{\Delta s_i/s_i}{\Delta c_j/c_j} \tag{3.7}$$

37

式 (3.7) の感度解析の結果を表 3.1 に示す.表 3.1 より,式 (3.5),(3.6) に含まれるパラメータの感度が高く,その他のパラメータは感度が小さく無視できる.よって,後の実験では, $K_V$ , $I_{cp}$ ,R, $C_1$  のみを回路階層のパラメータとし,統計解析の対象とする.

#### 3.4.2 機能記述モデルの精度

提案する階層的な統計解析手法を検証する前に、アナログ機能記述を用いた階層的なシステム解析の精度を検証する必要がある。そこで、2通りの方法で実行したモンテカルロ解析の結果の比較によりアナログ機能記述モデルの精度を評価する。モンテカルロ解析の一つ目の方法は、Verilog-AMS と SPICE を用いた PLL の階層的解析であり、もう一つは PLL 全体の SPICE による解析である。階層的モンテカルロ解析の手順は以下の通りである。

- 1. 回路ブロック毎のモンテカルロ解析を SPICE を用いて行なう. ばらつきパラメータとして考慮する  $I_{cp}$ ,  $K_V$ , R,  $C_1$  をサンプルごとに組にして抽出する.

- 2.1. で抽出した回路特性パラメータの組を用いて、システム階層で Verilog-AMS によるモンテカルロ解析を行なう.

比較のため、トランジスタのモデルパラメータは、PLL 全体の SPICE によるモンテカルロ解析と階層的解析で同じ乱数列を用いることにする.

39

比較する解析方法の概念を図 3.4 に示す。図中の (1) が SPICE による素子記述の解析を、(2)-(3) が階層的な手法を表す。図より両者の誤差は、主に Verilog-AMS によるモデル化の精度に起因することが推測される。

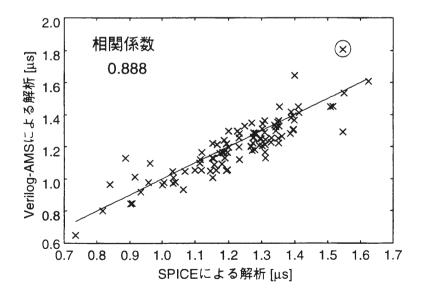

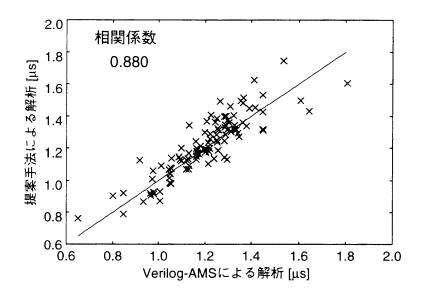

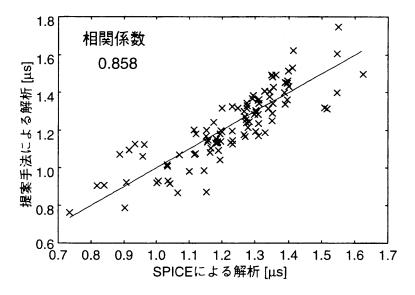

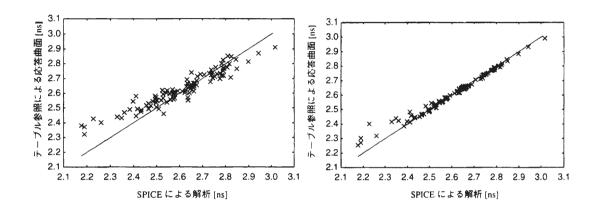

(1)の SPICE を用いた解析は1回あたり30分程度の解析時間を必要とするため、モンテカルロ解析はサンプル数を100回とした.実験結果の散布図を図3.5に示す.いくつかの点を除いては両者は良く一致している.相関係数は0.888であった.

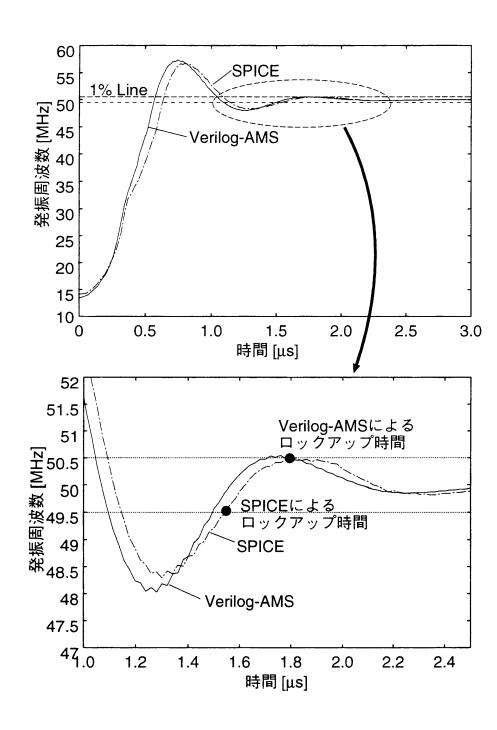

図3.5のいくつかに見られる顕著な誤差の原因を調べるため、例として図中で丸印をしたサンプルをとりあげる。図3.6に、このサンプルのロックイン過程の様子を、2通りの解析、すなわち、Verilog-AMSによる階層的な解析とSPICEによる解析について示した。図は発振周波数の時間的変化を表している。図3.6から明らかなように、Verilog-AMSによる機能記述による方法は、ロックイン過程を良く表している。誤差の原因は、ロックアップ時間の定義の仕方にある。ここで、ロックアップ時間は、目的のロック周波数に対して1%以内に収まる周波数と定義している。この例では、図3.6における拡大図を見ると、波形の2番目の山がVerilog-AMSによる場合は1%の線を越えているのに対して、SPICEではこの山がわずかにこの線を下回っている。このことが結果としてロックアップ時間の大きな誤差となっている。他のサンプルでも波形を調べたところ、この例のように両解析結果は良く一致していることが確認できた。

以上の議論から、Verilog-AMSを用いた階層的シミュレーションは、ロックイン 過程を精度良く表していることが分かった。また、3.4.1節でばらつきの元として選 んだ回路特性で、十分にばらつきを表現できることが分かる。

#### 3.4.3 階層的統計解析

階層的解析手法の精度を確認できたので、提案する応答曲面を用いた階層的統計解析手法をPLLに適用する. 応答曲面を使って、回路階層、システム階層のパラメータを式(3.1)、(3.2) のように下位階層のパラメータで表す. これにより、システム特性をプロセス階層の物理パラメータの多項式で表現することができる. 応答曲面の生成を以下のように行なった.

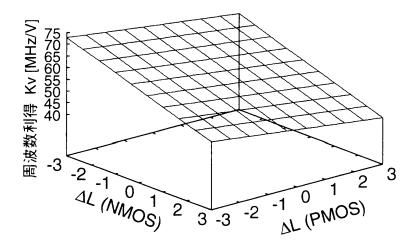

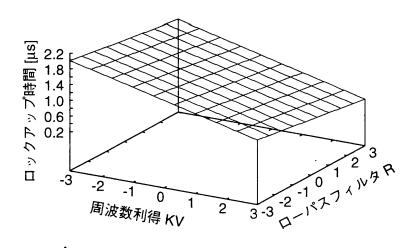

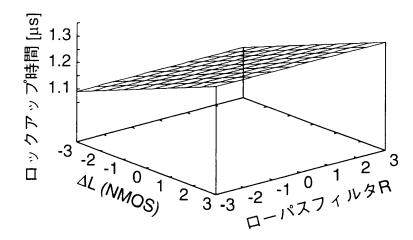

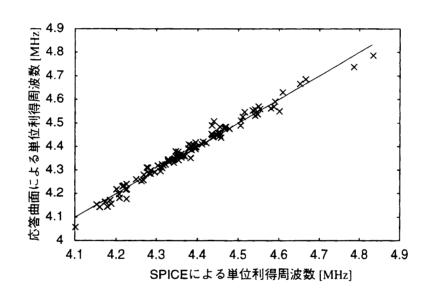

初めに、各回路ブロックの特性について、プロセス階層の物理パラメータに対する 応答曲面を生成する. これらの応答曲面は一次の多項式を用いた. 曲面の適合性は 重相関係数を用いて確認した. いずれの場合も 0.99 以上の値を示し精度良い近似が できていることが分かった. 生成した応答曲面の例として、VCO の周波数利得  $K_V$  のものを図 3.7 に示す.

次に、システム特性であるロックアップ時間の応答曲面を同様に生成する。先に述べた通り、システム特性の応答曲面は  $I_{cp}$ ,  $K_V$ , R,  $C_1$  の関数になる。応答曲面は 1次の多項式を用いた。応答曲面の重相関係数は 0.968 であり、十分な精度であると判断した。図 3.8 にロックアップ時間の応答曲面を示す。図は VCO の周波数利得  $K_V$  とローパスフィルタの R に対するロックアップ時間の応答曲面である。

図 3.4: 階層的統計解析手法の比較

図 3.5: SPICE と Verilog-AMS によるロックアップ時間解析の比較

図 3.6: ロックイン過程の波形—SPICE と Verilog-AMS による(図 3.5 の丸印をした波形に対応)

図 3.7:  $\Delta L$  (NMOS),  $\Delta L$  (PMOS) に対する VCO の周波数利得  $K_V$  の応答曲面 (物理パラメータはそれぞれの平均と分散で規格化を行なっている)

図 3.8: VCO の周波数利得  $K_V$  とローパスフィルタの R に対するロックアップ時間 の応答曲面  $(K_V$  と R はそれらの平均と分散で規格化を行なっている)

図 3.9: 物理パラメータに対するロックアップ時間の応答曲面(物理パラメータはそれぞれの平均と分散を用いて規格化している)

回路特性の応答曲面とシステム特性の応答曲面をつなぐことで、最終的にロックアップ時間をプロセス階層の物理パラメータで表現できる。図 3.9 に NMOS の  $\Delta L$  とローパスフィルタの R に対するロックアップ時間の応答曲面を示す。

階層的な統計解析の準備ができたので、次にこれを用いた応用例として、モンテカルロ解析、ワーストケース解析、そして感度解析を行なう.

応答曲面を用いた階層的モンテカルロ解析を行なう。ここでプロセスの物理パラメータは、3.4.2節のモンテカルロ解析でトランジスタのモデルパラメータに用いたものと同じ乱数列を使う。これは、このモンテカルロ解析(図 3.4 の (4)–(5))を 3.4.2 節の SPICE による解析(同図 (1)) 及び Verilog-AMS を使ったもの(同図 (2)–(3))と比較するためである。これらの比較をそれぞれ図 3.10 と図 3.11 に散布図で示す。

図 3.10 は Verilog-AMS と提案手法の比較であり、図 3.4 の (2)–(3) と (4)–(5) の比較に相等する.これは、主に提案手法における応答曲面の精度を評価していることになる.先の応答曲面の生成時には、これらの精度は十分であると判定した.しかし、図 3.10 において、両解析結果の差が大きなサンプルが存在する.この誤差の原因は、図 3.6 で示したようなロックイン過程のわずかな差によるロックアップ時間の変化である.このような誤差にも関わらず両者の整合は取れており、相関係数は 0.880 であった.

図 3.11 の PLL 全体の SPICE 解析と提案手法の比較は、この手法の精度を評価するものである。両者の相関係数は 0.858 であり、このことから、応答曲面をつなぎあわせて統計解析を行なう手法は、十分な精度で解析が可能であることが示された。

モンテカルロ解析に関して、最後に計算時間に関する議論を行なう。この実験で PLL 全体を SPICE により解析した場合(図 3.4 の (1)),一回の解析に約 35 分かかる。サンプル数 100 のモンテカルロ解析では 2 日以上の時間がかかり,実用的ではない。これに対して、提案手法(図 3.4 の (4)–(5))では,30 分程度でモンテカルロ

図 3.10: 提案手法と Verilog-AMS によるロックアップ時間の解析の比較

図 3.11: 提案手法と SPICE によるロックアップ時間の解析の比較

図 3.12: ロックアップ時間のモンテカルロ解析のヒストグラム

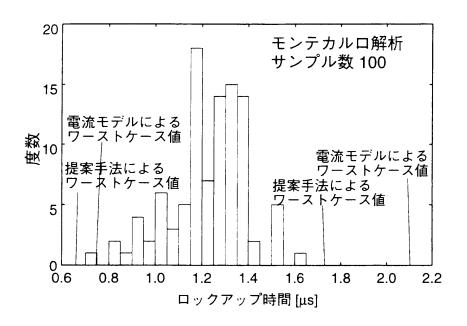

解析が実行可能である. 提案手法では、ほとんどが応答曲面の生成に必要な回路シ ミュレーションの時間によって占められており、それ以外の手順にかかる時間は無 視できる. 例えばシミュレーション結果の抽出は、今回の回路特性ではそのままシ ミュレーション結果から読み取ることができるので、ほとんど時間を費やさない、ま た、応答曲面の生成も最小二乗法によっており、ほとんどの場合 0.01 秒程度で生成 可能である. これらの結果から、提案手法は、SPICE 系のシミュレーションの 100 倍の速度で解析を行なうことができ、実用的な計算コストで統計解析を実現できる. 2つ目の応用例として、ワーストケース解析について述べる、ワーストケース値 を、平均から  $\pm 3\sigma$  ( $\sigma$ : 標準偏差) 離れた値と定義する、提案する手法を用い、サン プル数 1000 で行なったモンテカルロ解析から得られるワーストケース値を図 3.12 に「提案手法によるワーストケース値」として示す。図にはシステム全体に対する SPICEによるモンテカルロ解析(サンプル数 100)のヒストグラムもあわせて示す. SPICE によるモンテカルロ解析はサンプル数が少ないため、ワーストケース値の誤 差が大きいと考える、よって、ワーストケース値の比較は行なわないが、ヒストグ ラムと提案手法によるワーストケース値を比較すると、ワーストケース値がヒスト グラムの示す最悪値もしくは最良値付近を指していることが分かる.

次に、提案手法で求めたワーストケース値を従来手法によるワーストケース値と 比較する. 従来手法のワーストケースとして、電流値のワーストケースを取り上げ る. これはトランジスタ電流のばらつきが最大、最小になる場合のトランジスタパ ラメータをワーストケースパラメータとする.しばしば、このパラメータは回路特 性のワーストケースを求めるために用いられる。さらに、ローパスフィルタのR,  $C_1$ は、提案手法による解析の際に仮定したばらつき量をもとに  $3\sigma$ ( $\sigma$ : 標準偏差) 変

表 3.2: ロックアップ時間のワーストケース値の比較(単位 [ $\mu$ s])

3.4. 実験

| 推定方法  | ベストケース | ワーストケース |

|-------|--------|---------|

| 提案手法  | 0.66   | 1.73    |

| 電流モデル | 0.75   | 2.10    |

表 3.3: ロックアップ時間の感度解析(単位 [ns])

|                  | NMOS       |            |          |             |             |  |  |  |  |

|------------------|------------|------------|----------|-------------|-------------|--|--|--|--|

| -                | $\Delta L$ | $\Delta W$ | $T_{ox}$ | $V_{ m th}$ | $R_{ m sh}$ |  |  |  |  |

| $\overline{x_1}$ | -85.7      | -9.68      | -25.7    | 8.98        | -0.959      |  |  |  |  |

| $x_2$            | -2.38      | 31.5       | 8.01     | -7.01       | -0.953      |  |  |  |  |

| $x_3$            | -6.91      | -10.6      | 4.78     | -6.42       | 0.451       |  |  |  |  |

| PMOS             |            |            |              |             |             |  |  |

|------------------|------------|------------|--------------|-------------|-------------|--|--|

|                  | $\Delta L$ | $\Delta W$ | $T_{\rm ox}$ | $V_{ m th}$ | $R_{ m sh}$ |  |  |

| $\overline{x_1}$ | 8.12       | -0.895     | 5.14         | -12.2       | 0.643       |  |  |

| $x_2$            | 29.9       | -0.436     | 2.16         | 15.5        | 2.3         |  |  |

| $x_3$            | -25.2      | -0.997     | -0.562       | -7.71       | 1.69        |  |  |

動した場合の組合せをワーストケースとした。こうして求めた従来手法のワースト ケースを図3.12の「電流モデルによるワーストケース値」で示す。

従来手法と提案手法のワーストケースの比較の詳細を表3.2に示す。この表から分 かるように、従来の電流モデルによるワーストケース解析は現実に起こりうるワー ストケースからは大きくかけ離れたものとなっている.なぜならば.電流モデルの ワーストケースは各回路の真のワーストケースを表現しておらず、これを組み合わ せてもシステムのワーストケース値を得ることができないからである.また.仮に各 回路ごとに真のワーストケースを求めても、これらの組合せでシステム特性のワー ストケースを求めることは, 回路特性間の相関を考慮に入れていないため, 正確な 解析とはならない、このように、正確なワーストケース解析を行なうためには、物 理パラメータの統計情報を欠落することなく回路特性の統計情報に盛り込み、これ を考慮にいれてシステム階層で解析を行なう必要がある.提案する手法は、少ない 計算コストで以上のような解析を実現できる. この例からも, 階層的な統計解析手 法が有効であることが分かる.

提案手法の最後の応用例として感度解析を取り上げる、ここでは物理パラメータが ロックアップ時間に及ぼす影響を解析する. ロックアップ時間を式(3.3)により無相 関パラメータで表し、さらにこれらに対する感度解析を行なった。この感度  $\partial s/\partial x_i$ が大きいものから3つを取り出し、式(3.4)により展開した各項を表3.3に示す。

表 3.3 から、NMOS の  $\Delta L$  が最も大きな影響を及ぼすパラメータであることが分か る. また NMOS の  $\Delta W$ ,  $T_{\rm ex}$ , PMOS の  $\Delta L$  も大きな影響があることが分かる. こ のことは、次のように説明できる、すなわち、ロックアップ時間は VCO の可能発振 周波数に大きく依存している.このことは、結果としてトランジスタの電流特性の 影響に依存することとなり、これに影響を与えるパラメータの感度が大きくなる.

従来の感度解析は、各階層ごとに別個に行なわれてきた、しかし、この方法では 物理パラメータのシステム特性に与える影響を明らかにすることはできない. これ に対して提案する方法は、階層をわたって統計情報をやりとりするため、物理パラ メータを使ってシステム特性を表現することができる. これにより物理パラメータ のシステム特性への影響が階層を越えて知ることができる.このことは、プロセス 開発の立場で見た場合、プロセスパラメータがシステム特性に及ぼす影響を知るこ とができ、どのプロセスばらつきを抑えれば良いかの指針が得られる。

#### 3.5 まとめ

この章では、階層構造を使った統計解析の実験を行なった、設計システムを階層 的に取り扱い、階層間の統計情報の受渡しには応答曲面を用いることで、実用的な 時間で統計解析が適用可能であることを示した.

また、統計解析の例として、PLLのロックアップ時間を実験でとりあげた、PLL を機能記述によりモデル化し、これを使った解析の精度の検証と統計解析への適応 性を評価した、その結果、作成したモデルは統計解析に対しても十分な精度がある ことが分かった.

提案する解析方法の応用例として、モンテカルロ解析、ワーストケース解析、感 度解析を取り上げた、これらの実験では、階層間の統計情報をつなげることにより、 実際のばらつきを反映した解析を行なうことができた。さらにプロセスの物理パラ メータをもとにしたシステム特性の解析ができるため、システム特性が仕様を満た すために必要なプロセスパラメータの条件を知ることが可能である.

## 第4章

## 階層的歩留まり最適化手法

#### 4.1 はじめに

この章では、大規模なアナログ集積回路の統計的最適化手法を検討する、本題の 最適化に入る前に、ここで簡単にこれまでの章を振り返る。第2章では、小規模な ブロック回路を対象に歩留まりを考慮した回路定数最適化を行なった.しかし、こ の手法をそのまま大規模な回路に適用することは、計算コストの観点から不可能で ある、そこで、第3章で大規模回路に対する統計解析手法として、階層設計のボト ムアップ解析による手法を提案した、この章では、これをさらに発展させ階層的な 歩留まり最適化手法を提案する.

47

従来研究においても、階層的統計解析の手法は種々提案されている[37-40].しか し、これらの方法は、各階層間の統計的な情報を橋渡しすることでモンテカルロ解 析などの統計解析を実現しただけで、回路の最適化設計にまでは至っていない、つ まり、統計解析を行なった結果、歩留まりが不十分であることが分かっても、これ を改善することができない.この点から、大規模集積回路の統計的設計手法として はまだまだ不十分である. そこで、本章では第3章の提案手法を元に、これを最適 化まで拡張した手法を提案する.

ところでアナログ回路の階層設計における最適化手法として制約生成(constraint generation) に基づく手法が提案されており、回路設計やレイアウト生成への適用例 が報告されている[62-64]. これらの方法は、階層設計を利用したトップダウン設計 であり、制約生成の最適化問題により、上位階層から下位階層の特性が満たすべき 仕様を与える.しかし、回路設計において提案されている手法は、回路特性のばら つきを考慮に入れておらず、回路特性の統計情報をもとにした仕様生成技術が望ま れる、そこで、本章ではこの制約生成による手法に注目し、回路特性のばらつきを 考慮した手法へと拡張を試みた. 提案手法は、回路特性のばらつきを考慮し、シス テム特性がばらつきに対して適切な余裕を取れるよう回路仕様を生成する.ここで. 回路仕様として取るべき余裕を幾何学的に考え、回路特性空間内での統計的な距離

として表現した.この統計的な距離を表す項を最適化問題に採り入れることで,ばらつきを考慮に入れた仕様生成を実現する.提案手法は,トップダウン,ボトムアップの手法を繰返し行ない,トップダウン設計フローだけでは実現できないシステム全体の歩留まり最適化を行なうことができる.

本章の構成を述べる。まず 4.2 節で、第 3 章の統計解析手法を簡単に振り返るとともに、制約生成問題を階層的設計手法とともに説明し、その問題点を指摘する。4.3 節では、問題点に対する解決法として制約生成の歩留まり最適化問題への拡張を提案する。4.4 節で PLL (Phase Locked Loop) 回路を取り上げ、歩留まり最適化設計を行なった。最後に 4.5 節でまとめを行なう。

#### 4.2 階層的設計と制約生成

まず、対象とする設計の階層構造の説明からはじめる。本章においても、第1章で定義した階層構造を用いる。これはこれまでのものと同様ではあるが図 4.1 に示す。本章ではシステム階層と回路階層の統計情報のやり取りを主に考えるので、図 4.1 ではデバイス階層以下を省略して 3 つの階層に分けている。したがって、図 4.1 の最下層はトランジスタなどのデバイス特性を表すデバイス階層になっている。第1章で説明したように、デバイスのモデルパラメータはプロセス階層の物理パラメータと中間モデルを介して結びつけられている。今、物理パラメータが $n_p$  個存在するとして、これをベクトル $\mathbf{p}=(p_1,p_2,\ldots,p_{n_p})^T$  で表す。デバイス階層の上は機能ブロックごとの小規模な回路を表す回路階層であり、ここでは回路の特性がパラメータとなる。この階層の注目する $n_c$  個の回路特性をベクトル $\mathbf{c}=(c_1,c_2,\ldots,c_{n_c})^T$ で表す。最上位階層はシステム階層であり、ここでは回路特性をパラメータにした動作記述によりシステム特性が表される。同様に $n_s$  個のシステム特性をベクトル $\mathbf{s}=(s_1,s_2,\ldots,s_{n_s})^T$ で表す。第1章でも述べたように、図 4.1 において、下向きの矢印が仕様の流れを表しトップダウン設計に対応し、上向きの矢印が回路特性の情報の流れを表しボトムアップの設計に対応している。

図 4.1: 階層的システム解析

第3章の階層的統計解析では、計算コストの削減のために階層間におけるパラメータ同士の関係のモデル化に応答曲面を用いている。すなわち、デバイス階層から回路階層へのモデル化は応答曲面  $\operatorname{rsm}_{n\to c}$  を用い、回路特性  $c_i$  は

4.2. 階層的設計と制約生成

$$c_i = \operatorname{rsm}_{p \to c_i}(\boldsymbol{p})$$

と表される. 同様に、回路階層からシステム階層へは近似関数  $\mathrm{rsm}_{c o s_i}$  により回路特性  $s_i$  は

$$s_i = \operatorname{rsm}_{c \to s_i}(\boldsymbol{c})$$

となる.これらの応答曲面を使うことで、ボトムアップの方向に沿って統計解析が可能になる.しかし、もしシステム階層でばらつきに対して十分な歩留まりが得られない場合、これを改善することはできない.そこで歩留まり最適化の実現を考える.ここではボトムアップによる解析結果を受けて、歩留まりを改善するようトップダウンで新しい回路仕様を生成する方法を検討する.

トップダウン設計において最適化設計を行なうにはシステム階層から回路階層に最適な仕様を与える必要がある。ここで、最適な仕様とは、システム階層の仕様を満たす条件のもとで、各回路のコストを最小限におさえるものである。与えられた回路仕様に基づき、回路階層で最適化設計を行なう。

これまで、階層設計を用いたトップダウン最適化設計としては制約生成(constraint generation)による手法が提案されている [62–64]. 回路設計を対象とした手法では、回路階層での仕様の実現の容易さ、困難さをフレキシビリティ関数で表現する [62]. ここで、回路特性  $c_i$  に対してフレキシビリティ関数  $flex_{c_i}$  は次のような性質をもつ関数と定義される.

$$ext{flex}_{c_i}(c_i) = \begin{cases} ilde{\mathbf{a}} & \text{if it is in } \mathbf{c}_i \\ ilde{\mathbf{b}} & \text{if it is } \mathbf{c}_i \end{cases}$$

が実現困難な場合 (4.1)

システム全体のフレキシビリティ関数 flex を以下のように定義する.

$$flex(\mathbf{c}) = \sum_{i=1}^{n_c} w_i \cdot flex_{c_i}(c_i)$$

(4.2)

ここで $w_i$ は各回路のフレキシビリティ関数に付けられる重み係数である。制約生成の問題は以下のような最適化問題で表現される。

文献 [62] では、フレキシビリティ関数において回路ばらつきが考慮されていないため、歩留まりの最適化という点で不十分である。そこで、次の節において、フレキシビリティ関数にばらつきにもとづく項を導入することで、この手法をシステム歩留まりの最適化へ拡張する方法を提案する。

#### 4.3 提案手法

回路変数  $\mathbf{c}=(c_1,c_2,\ldots,c_{n_c})^T$  の空間を考える.ここで容認領域  $A_c$  を回路変数空間 内でシステム特性が仕様を満たす領域とする.いまシステム特性  $\mathbf{s}=(s_1,s_2,\ldots,s_{n_s})^T$  が  $\mathbf{c}$  の応答曲面関数  $\mathrm{rsm}_{\mathbf{c}\to\mathbf{s}_i}(\mathbf{c})$  で近似されているとすると

$$\mathcal{A}_c = \{ \boldsymbol{c} \mid s_i^{\mathrm{L}} \leq \mathrm{rsm}_{\boldsymbol{c} \to s_i}(\boldsymbol{c}) \leq s_i^{\mathrm{U}}, \ i = 1, 2, \dots, n_s \}$$

となる. ここで  $s_i^{\rm L}$ ,  $s_i^{\rm U}$  はシステム特性に求められる仕様で、特性の下限と上限とする (片方のみが存在する場合もある). よって、 $A_c$  の境界は

$$s_i^{\mathcal{X}} = \operatorname{rsm}_{c \to s_i}(c), \ i = 1, 2, \dots, n_s, \ \mathcal{X} = \operatorname{Lor} \mathcal{U}$$

(4.4)

で表される。

プロセスばらつきのため,回路特性は設計値に対してある分布を持つ.この確率 密度関数を第1章で定義したように  $pdf_c(\boldsymbol{d},\boldsymbol{c})$  とする.ここで, $\boldsymbol{d}$  は各回路のトランジスタサイズなど設計者により設計可能な変数であり,これを設計変数と呼ぶ.第1章で説明したように,確率密度関数  $pdf_c(\boldsymbol{d},\boldsymbol{c})$  は  $\boldsymbol{d}$  の関数になっており,回路特性 の出現確率が設計変数の値により変化する.回路の出現確率と  $\boldsymbol{A}_c$  の概念図を図 4.2 に示した.

システム特性の歩留まり Y は次の式で求められる.

$$Y = \int_{\mathcal{A}_c} \mathrm{pdf}_c(\boldsymbol{d}, \boldsymbol{c}) \mathrm{d}c \tag{4.5}$$

システム設計において、式 (4.5) の積分値が 1 に近い値を持つよう制約生成で回路仕様を決めることが望まれる。 つまり、予想される回路ばらつきに対して、システム階層で十分高い歩留まりが得られるよう、回路の仕様値を  $A_c$  の境界から十分余裕をもってとる必要がある。 そこで、この余裕を表す指標としてマハラノビスの距離 [65] を取り上げ、これをフレキシビリティ関数に組み込む方法を提案する。

図 4.2: 回路変数空間におけるシステム特性の容認領域 A。と回路の出現確率分布

まず、マハラノビスの距離を説明する. 確率変数 cの分布関数として正規分布を仮定すると、確率密度関数  $\mathrm{pdf}_c(\pmb{d},\pmb{c})$  は

$$\operatorname{pdf}_{\boldsymbol{c}}(\boldsymbol{d}, \boldsymbol{c}) = \frac{1}{(2\pi)^{n_{\boldsymbol{c}}/2}} \frac{1}{|\boldsymbol{R}|^{1/2}} e^{-\frac{1}{2}(\boldsymbol{c} - \bar{\boldsymbol{c}})^T \boldsymbol{R}^{-1}(\boldsymbol{c} - \bar{\boldsymbol{c}})}$$

(4.6)

となる. ここで R は回路変数 c の分散共分散行列,  $\bar{c}$  は c の平均である. 確率密度関数が式 (4.6) で表されているとき、等確率密度面は

$$(\boldsymbol{c} - \bar{\boldsymbol{c}})^T \boldsymbol{R}^{-1} (\boldsymbol{c} - \bar{\boldsymbol{c}}) = constant \tag{4.7}$$

となり、楕円体となる.

分布の中心から回路空間中の任意の点までの距離を考える。ここで、ユークリッド幾何学的なものではなく、確率密度関数の値をもとにした距離を考える。すなわち、空間内の点cと平均 $\bar{c}$ の距離 $d_R$ を次式で定義する。

$$d_R^2 = (\boldsymbol{c} - \bar{\boldsymbol{c}})^T \boldsymbol{R}^{-1} (\boldsymbol{c} - \bar{\boldsymbol{c}})$$

(4.8)

式 (4.8) による距離を,統計学ではマハラノビスの距離と呼ぶ.統計的な解釈では,マハラノビスの距離が近い点ほどその特性を取る回路の出現確率が高くなる.分布の中心から  $A_c$  の境界までのマハラノビスの距離は,最も出現確率の高い点までの距離になる(図 4.2 参照).したがって,マハラノビスの距離は,統計的に  $A_c$  の境界までの余裕を測るというここでの目的にかなっている.

回路仕様に対して最適化により生成される回路の特性分布は、仕様として与えられた値を平均値として正規分布をとると仮定する。つまり、生成する仕様からの距離をマハラノビスの距離で考えることにし、式 (4.8) の $\bar{c}$ を仕様点 $\bar{c}_{\rm spec}$  と書くことにする。

ここで、許容領域  $A_c$  の境界と回路仕様とのマハラノビスの距離を求める問題を定式化する。今、システム特性の容認領域  $A_c$  の境界は式 (4.4) で表される。仕様  $c_{\rm spec}$  と i 番目の境界とのマハラノビスの距離は以下の最適化問題の解となる。

$$\min_{\mathbf{c}} (\mathbf{c} - \mathbf{c}_{\text{spec}})^T \mathbf{R}^{-1} (\mathbf{c} - \mathbf{c}_{\text{spec}})$$

subject to  $s_i^{X} = \text{rsm}_{\mathbf{c} \to \mathbf{s}_i}(\mathbf{c})$  (4.9)

マハラノビスの距離の説明ができたので、ここでばらつきに対する余裕を考慮した仕様生成について説明する。まず、 $A_c$ の境界曲面、式(4.4)と仕様点のマハラノビスの距離のうち最小のもの  $d_R^{\min}$  を計算する。次に、この距離が遠いほど値が小さくなる関数の項をフレキシビリティ関数に追加する。つまり、追加する関数はマハラノビスの距離が最も近い仕様制限をなるべく遠くにするという要求を行なう。追加する関数は正規分布の関数を参考に以下のものを提案する。

$$V = e^{-\frac{1}{2}d_R^{\min^2}} \tag{4.10}$$

この項を追加することで、フレキシビリティ関数は次のようになる.

$$flex(\mathbf{c}) = \sum_{i=1}^{n_c} w_i \cdot flex_{c_i}(c_i) + w_V V$$

(4.11)

ここで $w_{V}$ は重み係数である.

新たにフレキシビリティ関数に追加した項Vの計算で一つ問題がある。それは、仕様生成の時点では、その仕様から生成される回路特性の分布を知ることはできず、回路特性の分散共分散行列Rが不明であるということである。そこで、仕様生成の段階で回路特性の分布を見積もる必要がある。ここではRとして、ある仕様をもとに生成した回路を統計解析して得られるものを使うことにする。当然、仕様生成前の回路と仕様生成後に回路定数最適化で得られる回路では回路の分布は変化する。このため提案する手法では、仕様生成と回路の統計情報の抽出を繰返し、この分布の差を小さくしていくことで最適な設計へと収束させることにする。この過程は、システム階層と回路階層の間を何回か行き来することになる。すなわち、トップダウンとボトムアップを交互に繰り返すことで所望の回路を得る。

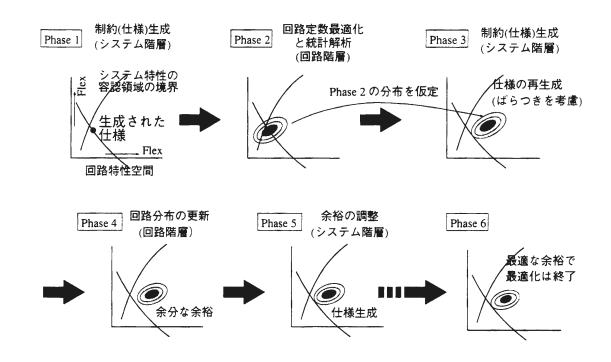

以上をふまえて、提案する最適化手法を提示する.

- 1. 式(4.2)を使い,式(4.3)の制約生成行なう.なお,これは4.2節で説明した従来手法の制約生成と同じである.これにより,各回路ブロックに対する仕様が与えられる.

- 2. 前のステップで得られた仕様をもとに、各回路ブロックにて回路定数最適化を 行なう. つまり、与えられた仕様を各回路ブロックが満たすように、各回路の 設計変数 d の最適化を行なう.

- 3. 得られた回路をもとに、各特性の統計情報を抽出する。回路特性cの平均 $\bar{c}$ と 各回路特性間の分散共分散行列Rを計算する。

- 4.3で得られた回路特性の統計情報をもとにシステム特性の統計解析を行なう.この3から4までの解析は第3章で述べたボトムアップによる統計解析である.

- 5. あらたに制約(仕様)生成を行なう. このとき目的関数は式(4.11)を使う. 3 で得られた分散共分散行列  $\mathbf{R}$  を,式(4.11)で必要なマハラノビスの距離の計算に使う.

- 6. 得られた回路仕様が前回のものに対して更新されていなければ停止. そうでないなら 2 へ. ここで, 2 の定数最適化は 5 で得られた仕様を満たすように行なわれる. これに加えて, 3 で計算した各特性の標準偏差の±3 倍を各回路の許容ばらつきとする. つまり, ここでの定数最適化は統計的歩留まり最適化である.

以上の最適化手順の概念を図 4.3 に示し、この図を使って手順の詳細な説明を行なう、図は、回路特性空間を示している。また、各回路特性は空間中の左下方向が 実現の容易さ度合が高いことを仮定している。つまり、この方向へ行くほどフレキ シビリティ関数の値が小さくなる。

手順1を行なうことで、ばらつきを考慮しない制約(仕様)生成を行なう。ばらつきのための余裕を取らないので、生成される制約(仕様)はシステム特性の容認領域

図 4.3: 最適化プロセスの概念図

$A_c$ の境界に落ち着く(図 4.3、Phase 1). 手順 2 で、それぞれの回路ブロックに与えられた制約(仕様)に対して、回路定数最適化を行なう.次に手順 3、4 において、回路ブロックの特性の分布とシステム特性の歩留まりが計算される. 回路定数最適化における仕様はばらつきを考慮に入れていないため、ここでの最適化結果の歩留まりは低いものとなる(図 4.3、Phase 2). さらに、回路特性の分布が次のステップでも手順 3 で求めたものと変わらないという仮定のもとで、手順 5 のばらつきを考慮に入れた制約(仕様)生成を行なう(図 4.3、Phase 3). 再び手順 2 に戻り、回路定数歩留まり最適化を行なう.更に、回路ブロックの分布を計算し(手順 3)、新しい回路ブロックの統計情報を得る.この手順は、手順 5 で予想した回路特性分布を更新することから回路分布の更新と呼ぶことにする.図 4.3 に示した例では、回路分布の更新により前回の仕様生成は余裕の取り過ぎであることが分かった(Phase 4). そこで、この余分な余裕を取り除くためにさらに制約(仕様)生成を行なう.この操作を余裕の調整と呼ぶことにする.何回か回路分布の更新と余裕の調整を繰り返すことにより、システムは十分な歩留まりと適度な余裕をもつ設計に落ち着くはずである(図 4.3、Phase 6).

本章の最後に、回路の歩留まり最適化について述べる。回路階層の歩留まり最適化手法については第2章で議論した。ここでの最適化の目的関数は、第2章同様、Aftabらによって定式化された $C_p$ - $C_{pk}$ という品質管理の指標をもとにしたもの[58]を用いている。この目的関数を用いると、最適化は回路特性の平均値を仕様の中心に置くと同時に、分散値も抑えることができる。

## 4.4 実験

ここで、提案手法の有効性を確認するため PLL (Phase Locked Loop) をとりあげ、ロックアップ時間の最適化を行なった。ロックアップ時間は,入力周波数の変化に対し PLL の出力周波数が 10 MHz から 50 MHz ヘロックするのにかかる時間とする。PLL は第3章の実験で用いたものと同じものを用いる。すなわち,位相周波数比較器,チャージポンプ,ローパスフィルタ,電圧制御発振器(Voltage Control Oscillator: 以下 VCO),分周器からなる。システムの機能記述モデルもやはり第3章で用いたものと同じものを用いた。機能記述には Verilog-AMS を用いた。

なお、この実験では  $0.6\mu m$  CMOSプロセスを用いる。トランジスタのモデルパラメータとして、付録 A.1 で説明した抽出手法により生成した統計的パラメータを用いる。ばらつきの元として考慮する物理パラメータは、実チャンネル長のマスク長からのずれ  $\Delta L$ 、実チャンネル幅のマスク幅からのずれ  $\Delta W$ 、酸化膜厚  $T_{\rm ox}$ 、しきい値電圧  $V_{\rm th}$ 、ドレイン・ソースの寄生抵抗  $R_{\rm sh}$  である。

まず、PLLに対して制約生成問題の定式化を行なう。第3章でも述べたようにPLLの過渡特性には以下のパラメータが重要な役割を果たす。

$$\omega_{\rm n} = \sqrt{\frac{I_{\rm cp} K_V}{2\pi N C_1}} \equiv \omega(\boldsymbol{c})$$

(4.12)

$$\zeta = \frac{R}{2} \sqrt{\frac{C_1 I_{\text{cp}} K_V}{2\pi N}} \tag{4.13}$$

これらは、それぞれ自然角周波数、ダンピング係数 [61] と呼ばれる。ここで、 $K_V$  は VCO の周波数利得、 $I_{cp}$  はチャージポンプの吐き出し、吸い込み電流、 $C_1$ 、R はローパスフィルタの容量値と抵抗値、N は分周器の分周比である。第3章の実験により、ロックアップ過程は自然角周波数、ダンピング係数により決まり、回路特性 c として式 (4.12)、(4.13) 中の  $K_V$ 、 $I_{cp}$ 、 $C_1$ 、R を選べば良いことが分かっている。また、ダンピング係数は系の安定性から設計値として 0.8 をとることにする。ここでは、ダンピング係数の値を固定して、 $\omega_n$  の応答曲面を描くことから定式化をはじめる。

$$t_{\text{lock}} = rsm_{s}(\omega_{n}) \tag{4.14}$$

ロックアップ時間  $t_{lock}$  を自然角周波数  $\omega_n$  の一次式であてはめた結果,重相関係数が 0.946 となり,十分な精度で表すことができた.よって,式(4.3)の制約条件はロックアップ時間の仕様を  $t_{locksp}$  とすると,以下のようになる.

$$t_{\text{locksp}} \ge t_{\text{lock}} = \text{rsm}_{\text{s}}(\omega_{\text{n}}) = \text{rsm}_{\text{s}}(\omega(\boldsymbol{c}))$$

(4.15)

実験ではロックアップタイムの仕様を  $t_{locksp}=10.0\mu s$  とする. さらに、先ほどのダンピング係数に対する設定があるので、もうひとつの制約条件が加わる.

$$\zeta = \frac{R}{2} \sqrt{\frac{C_1 I_{\rm cp} K_V}{2\pi N}} = 0.8 \tag{4.16}$$

表 4.1: 各回路の制約上限

| 回路特性        | 上限                     |

|-------------|------------------------|

| $I_{ m ch}$ | $150\mu\mathrm{A}$     |

| $K_V$       | 70MHz/V                |

| $C_1$       | $700 \mathrm{pF}$      |

| R           | $1.1 \mathrm{k}\Omega$ |

図 4.4: 最適化による歩留まり向上とばらつきに対する余裕

式(4.3)の制約条件が定式化できたので、次は目的関数を考える。各回路のフレキシビリティ関数は以下のものを用いた。

$$flex_{c_i} = e^{\mathbf{a}^{\mathrm{U}}(c_i - c_i^{\mathrm{U}})} \tag{4.17}$$

式(4.17)は,各回路実現の容易さの上限  $c_i^{\rm U}$  を設け,これらの値を越えると増加傾向が強くなる関数である。 $a^{\rm U}$  を大きくすることにより,すりばちの形状がより急峻になる.各回路の  $c_i^{\rm U}$  を表 4.1 にまとめる.

以上の目的関数と制約条件を元に提案手法を適用した. 仕様生成と回路最適化の繰返しは4回目の制約生成で設計定数の変化がなく停止した.

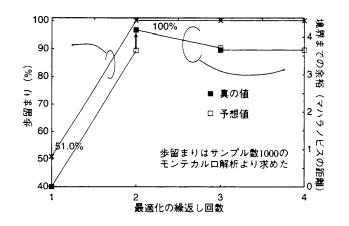

提案アルゴリズムにより歩留まりの向上がどのように行なわれたかを図 4.4 に示す、また、生成制約(仕様)からシステム特性の容認領域の境界までのマハラノビスの距離もあわせて示す。先に述べたように、回路定数歩留まり最適化後の回路分布の更新により正確な距離を知ることができる。そこで、各繰返しにおいて更新前の予想値と、更新後の実際の距離を、それぞれ図中の「予想値」と「真の値」で示した.「予想値」と「真の値」はそれぞれ図 4.3 の Phase 3 と Phase 4で測る余裕に相当している。また、図 4.4 での余裕の予想値と真の値の差が、回路分布の更新量に相当する。この図を、歩留まりの改善と余裕の調整の 2 つの面から考察する。

まず、歩留まりの改善から述べる、提案アルゴリズムでは、1回目の制約生成は回路のばらつきを考慮しないものからはじめる、すなわち、フレキシビリティ関数を

式(4.2)とした従来手法の制約生成である。そのため、1回目の制約(仕様)生成、回路定数最適化では51.0%と十分な歩留まりが得られていない。続く2回目以降は制約(仕様)生成において手順5を行なうため、ばらつきのための余裕を見込んだ仕様生成を行なう。このため、2回目以降は100%の歩留まりに到達している。

次に4.3節で述べた、余裕の調整について見ていく、図4.4からも明らかなように、 歩留まりが100%に到達した後でも余裕の調整は続いている。つまり、回路分布の更 新と余裕の調整の繰返し過程が続く。このため、歩留まりが100%に到達していても 最適化過程は終了しない。図4.4で2回目の繰返しを見ると、大きな回路分布の更新 が起こっている。このことは、続く制約(仕様)生成において、更新した分布を用 いてより少ないコストによる回路の生成の可能性を示唆している。すなわち、回路 分布の更新により明らかになった過剰な余裕を、余裕の調整により、より少ないコ ストのシステムの実現に結びつける。実際、3回目の繰返しで制約(仕様)生成を実 行し、より少ないコストの仕様が実現したことを確認できた。

なお、歩留まりの改善が急激に100%にまで上昇しその後変化が見られないのは、この手法では良く見られる経過である。このことは、最適化の過程において、回路分布の更新で特性分布に大きな変化が現れないことを意味する。歩留まりの変化は見られないが、何も行なわれていないのではなく、各繰返しにおいて仕様の生成と回路階層での回路定数歩留まり最適化を行ない、より少ないコストへと最適化を進めている。

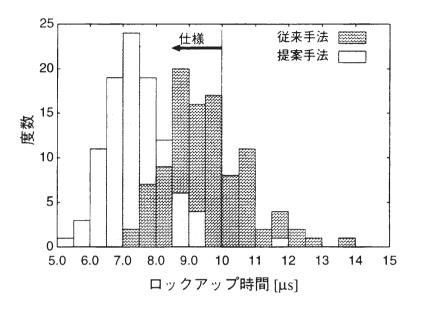

最適化の1回目と4回目の Verilog-AMS で計算したロックアップ時間の分布のヒストグラムを、それぞれ従来手法の制約生成 $^1$ と提案手法として図 $^4$ .5に示す。また、分布の平均と標準偏差の比較を表 $^4$ .2 に示す。これらから、従来手法では平均の値 $^9$ .53 $\mu$ s はロックアップ時間の仕様 $^1$ 0 $\mu$ s 以内に入っているが、ばらつきを考慮した場合歩留まりが不十分であることが分かる。これに対して提案手法ではばらつきを考慮した最適化が行なわれていることが分かる。

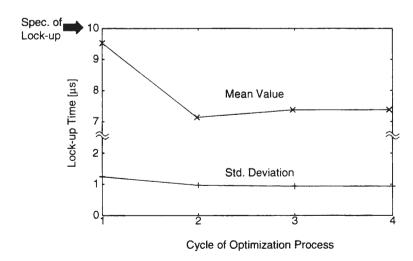

最後に、最適化過程における平均と標準偏差の変化の様子を図4.6に示す. 最終的に得られた特性の平均は仕様値からおよそ標準偏差の3倍離れていることがわかる. このことからも、ばらつきに対し適切な余裕をとった設計であることが確認できる. 平均値は2回目の繰返し時に最速となる. しかし、この特性は過剰な性能であり、3回目以降、この過剰な性能が余裕の調整により減少していく過程が図から見ることができる. また、標準偏差の値も減少していることがわかる. これは、2回目の繰返し以降、回路定数歩留まり最適化により標準偏差(ばらつき)の小さい回路へ最適化しているためである.

図 4.5: ロックアップ時間のヒストグラム―提案手法と従来手法の比較

表 4.2: 従来手法と提案手法のロックアップ時間の平均と標準偏差(Verilog-A によるモンテカルロ)

|      | 平均 [μs] | 標準偏差 [μs] |

|------|---------|-----------|

| 従来手法 | 9.53    | 1.24      |

| 提案手法 | 7.38    | 0.930     |

図 4.6: 最適化過程におけるロックアップ時間の平均、標準偏差の変化

<sup>11</sup> 回目の制約(仕様)生成は従来手法の制約生成であることに由来している。

#### 4.5 まとめ

本章では、大規模なアナログ回路を対象に階層設計手法を利用した歩留まり最適 化手法を提案した。トップダウン設計において制約生成を適用し、システムの構成 回路に対して仕様を与える。提案手法では、制約生成において各回路に対するコス トの他に、歩留まりに対する余裕を考慮できるため、システム特性の歩留まりの向 上が実現できる。

## 第5章

## ベクトル合成モデルによる統計的遅延解析

#### **5.1** はじめに

これまでの章でアナログ回路の統計的な解析を取り扱ってきた.この章からは、これまでの手法を踏まえてディジタル回路を取り扱うことにする.

近年のプロセスばらつきの問題はディジタル回路においても重要な問題となっている. 例えば, 重要な特性であるゲートの遅延時間も, プロセスばらつきに起因しばらついており, これを考慮しなければ目標とする動作周波数で動作しなくなり, 結果として歩留まり低下をもたらす. そこで, ここでは, ディジタル回路において特に重要な特性である遅延時間の解析を取り扱う.

まず、従来手法による解析について述べその問題点を明らかにする。従来、ばらつきを考慮した解析方法としてモンテカルロ解析[6]がある。これは、変動の要因となる物理特性の統計的分布をもとにシミュレーションモデルパラメータを変化させ、シミュレーションを行なう。実際の物理特性の分布特性(分散、相関)を正確に反映したシミュレーションが行なえる反面シミュレーションコストが重要な問題になる。つまり、モンテカルロ解析の精度はシミュレーション回数に依存し、十分な精度の解析を行なうには少なくとも100~1000回のシミュレーションが必要である。従って、回路シミュレーションを使ってこの手法を適用することは、実用上不可能である。

このような問題からより少ないシミュレーションコストによる方法が検討されてきた[6,11,45,66]. 簡便であるという理由から一般的によく用いられる方法に、ワーストケース解析(コーナ解析)がある. この方法はトランジスタの電流特性をもとに遅延時間の「速い」、「遅い」の二通りの場合を決定し、回路シミュレータのモデルパラメータ(ワーストケースパラメータ)として用意しておくものである. それぞれのパラメータにおけるシミュレーション結果を最悪のケースとしてばらつきの量を推定する. 以下、この手法は電流特性を元にしたモデルを用いることから、電流特性のワーストケース解析と呼ぶことにする.

実際の製造の現場においてはこの方法が良く用いられるにもかかわらず、ワース

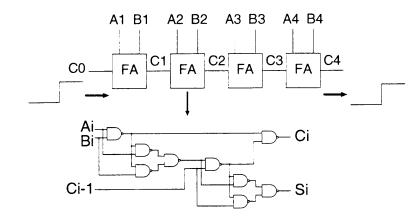

図 5.1: 4bit 加算回路

図 5.2: 4bit 加算回路の遅延時間の分布とワーストケース値

トケース解析は、モンテカルロ解析で得られるばらつき量と比較して精度が悪い.ここでこの手法の解析例を通してこの方法の問題点を確認し、本章において取り組むべき課題を明確にする.

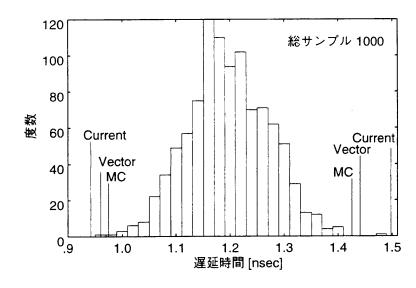

例として図 5.1 に示した 4bit 加算回路の桁上げ信号の遅延時間を取り上げ、ワーストケース解析およびサンプル数 1000 のモンテカルロ解析を適用した例を図 5.2 に示す。図 5.2 にはモンテカルロ解析を適用し平均から標準偏差の 3 倍の位置を「MC」、電流特性のワーストケース解析の結果を「Current」としている。モンテカルロ解析から求められるワーストケース値と電流特性によるそれとの間に差があることがわかる。モンテカルロ解析の結果はサンプル数からも精度的に十分と考えられるので、電流特性のワーストケース解析に精度の問題があることになる。

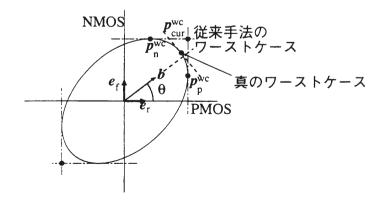

この問題の原因はワーストケースパラメータが経路の遅延のワーストケースを十

分に表していない点にある。このことは単独のセルの遅延のワーストケースが経路のワーストケースにはならないことを意味している。つまり信号経路中に立ち上がり、立ち下がりが混在する場合のワーストケースを、従来手法のPMOSとNMOSの電流特性のワーストケースの単純な組合せでは表現できないのである。このことから、経路のワーストケースを正確に求める方法が必要である。

以上より本章の目的は、この従来手法の精度の問題点を克服し、少ないシミュレーションコストで正確に遅延時間の統計解析を行なうことにある。具体的には、セルの遅延特性とトランジスタの電流特性の関連から、ばらつきの原因となる物理パラメータと遅延量を結びつける簡潔な遅延特性モデル(ベクトル合成モデル)を提案し、このモデルを使って遅延時間の統計的分布を求める。

本章の構成を述べる. 5.2節ではワーストケースを決定する1次係数ベクトルという概念を導入する. 5.3節では1段構成のセルの遅延時間がトランジスタの電流特性に影響を受けることから1次係数ベクトルに共通な性質を仮定として導く. 5.4節では経路の遅延を1次係数ベクトルの合成で表現するベクトル合成モデルを提案する. 5.5節では以上で述べた理論に対する検証ならびに従来手法の電流特性によるワーストケース解析の誤差を定量的に評価する.

## 5.2 ワーストケース解析と1次係数ベクトル

ワーストケースを見い出す手法については種々の方法が提案されている.ここでは,文献[11]により提案されている,プロセスばらつきの統計的分布にもとづき現実に起こりうる可能性を考慮したワーストケース抽出手法を用いることにする.

まずプロセスの変動のもととなる物理量—例えば実チャンネル長のマスク長からのずれ  $\Delta L$ , 酸化膜厚  $T_{ox}$  など—を変動変数と定義し、これを n 次元変動変数空間中のベクトル  $\mathbf{p}=(p_1,p_2,\ldots,p_n)^T$  で表す。また、変動変数の分布関数(確率密度関数)を既知のものとし  $\mathrm{pdf}(\mathbf{p})$  とする。回路の入力から出力までの遅延時間  $t_{d}$  を、変動変数の関数と仮定して、応答曲面により近似することを考える。応答曲面関数を  $\mathrm{rsm}$  とすると、

$$t_{\rm d} = \operatorname{rsm}(\mathbf{p}). \tag{5.1}$$

式 (5.1) の応答曲面をもとに,回路特性の平均値  $\mu_{t_d}$ ,標準偏差  $\sigma_{t_d}$  を求める.これらはモンテカルロ解析を行なうことで得ることができる.ここで, $pdf(\mathbf{p})$  をもとに,式 (5.1) を使って遅延値を得ることができるので,モンテカルロ解析はシミュレーションコストを費やさずに計算できる.

ワーストケース値twc は以下のように書ける.

$$t_{\rm d}^{\rm wc} = \mu_{t_{\rm d}} + wk\sigma_{t_{\rm d}} \tag{5.2}$$

ここで、w は遅延量が最も大きい(遅い)場合 +1、最も少ない(速い)場合 -1 をとる。また、k はワーストケースの平均値  $\mu_{ta}$  からの距離を標準偏差  $\sigma_{ta}$  を基準に表

す、例えば、正規分布を仮定した場合 k=3 で約 99.7% の出現確率を表す点をワー ストケースとして選ぶことになる.

ワーストケースは、式(5.2)のワーストケース値をとる条件のもとで、最も確率 密度値が高い場合と定義できる.したがって、ワーストケースを求める問題は以下 のように定式化できる.

$$\max_{\boldsymbol{p}} pdf(\boldsymbol{p})$$

subject to  $t_{d}^{wc} = rsm(\boldsymbol{p})$  (5.3)

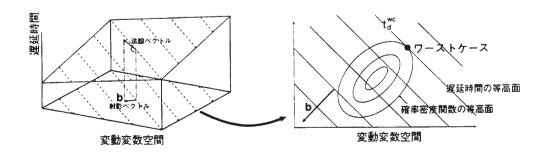

この式(5.3)のワーストケースを求める最適化問題は幾何学的には次のように考 えることができる. すなわち、 $t_{x}^{yc} = rsm(\mathbf{p})$  なる応答曲面の等高面が確率密度関数 の等確率密度面と接するとき、その接点がワーストケースである.

ここで、さらに議論をすすめるために、遅延時間の応答曲面モデルを簡単化して 1次式の場合を考える、通常、変動変数空間で考慮する領域は狭く、1次の応答曲面 で十分な場合が多い、応答曲面は次式のように書ける、

$$t_{\mathbf{d}} = \operatorname{rsm}(\boldsymbol{p})$$

$$= b_0 + b_1 p_1 + b_2 p_2 + \dots + b_n p_n$$

$$= b_0 + \boldsymbol{b}^T \boldsymbol{p}$$

(5.4)

ここで $b_0$ ,  $\boldsymbol{b}=(b_1,b_2,\cdots,b_n)^T$ は1次の応答曲面モデルの回帰係数である.このベ クトル b の幾何学的な意味は、応答曲面の法線ベクトルを変動変数空間へ下ろした 射影ベクトルである。また、このベクトルに対して垂直な変動空間中の平面が、応 答曲面の等高面である。すなわち、ベクトルbは変動変数空間において遅延時間の 変動方向を示している.以上を図5.3に示す.

1次の遅延応答曲面モデルの場合  $t_{

m d}^{

m wc}={

m rsm}(m{p})$  なる等高面は平面となり,確率密 度関数との接点(ワーストケース)は、確率密度関数の形状とこの平面の法線ベク トルトの方向により決まる、つまり、セル、組合せ回路のワーストケースの変動変 数空間中の位置を議論するには、このベクトルの方向を論ずればよい.

以上の議論から、ワーストケースの変動変数空間上の位置を決定づけるものとし て、ベクトルもは重要な役割を果たす、そこで、このベクトルを1次係数ベクトル

図 5.3: 応答曲面、1次係数ベクトル、ワーストケース

5.3. セルの遅延特性のワーストケースと応答曲面

図 5.4: 1段 CMOS 論理セル

と呼ぶことにする.

## 5.3 セルの遅延特性のワーストケースと応答曲面

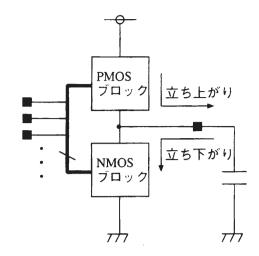

この章では CMOS の1段構成のセルの遅延のワーストケースについて考察する. ここでの1段構成の定義は、図5.4のようにNMOSとPMOSのブロックが出力ノー ドで結合した構成とする.

組合せ論理回路のセルの遅延時間は、出力に接続された負荷容量の充放電に要す る時間と考えることが出来る。図5.4からわかるように、立ち上がり時は容量に対 して充電が必要であり、通常の CMOS LSI の動作では、PMOS のドレイン電流によ り電荷が供給される、逆に立ち下がり時は、容量の放電が行なわれ、NMOSのドレ イン電流がこれに関与する、このことから、遅延特性は立ち上がりと立ち下がりで、 それぞれ PMOS と NMOS のトランジスタの電流特性と密接な関係がある. すなわ ち、1段構成のセルの遅延時間のワーストケースは、PMOSとNMOSのトランジス タの電流特性のワーストケースで近似できると考えられる.

1段構成のセルの種類、入力波形の過渡時間、負荷の容量などの条件が変化する と、遅延特性も変化する、しかし、これらの条件が変化しても、遅延特性のワース トケースがトランジスタの電流で決定されることには変わりがない。よって、種々 の条件でも、セルの遅延時間には共通のワーストケースが存在すると考えられる.

別の見方をすると、共通のワーストケースを持つということは、5.2節で導入した 1次係数ベクトルの向きが共通であるということである.そして、種々の条件により 遅延時間が変化するという点は1次係数ベクトルの向きではなく大きさが変化する ということである。以上をまとめて次の仮説とする。

#### 仮説

1段構成のセルには、そのセルの種類、入力波形の立ち上がり、立 ち下がり時間、負荷容量にかかわらず、共通の1次係数ベクトルの 向きを持つ.

立ち上がりと、立ち下がりで PMOS、NMOS のワーストケースに近似されるため、 2通りの共通の1次係数ベクトルの向きが存在する.ここで,立ち上がり方向の単位 ベクトルを $e_r$ . 立ち下がり方向の単位ベクトルを $e_f$ と表す.

これらのベクトルを用いると、式 (5.4) は、立ち上がり  $t_{dr}$ 、立ち下がり  $t_{df}$  でそ れぞれ

$$t_{\rm dr} = b_{\rm 0r} + b_{\rm r} \cdot \boldsymbol{e}_{\rm r}^T \boldsymbol{p}, \ t_{\rm df} = b_{\rm 0f} + b_{\rm f} \cdot \boldsymbol{e}_{\rm f}^T \boldsymbol{p}$$

(5.5)

$\geq b_{\{r,f\}} = |b|.$

なお、立上り遅延時間は PMOS の電流特性により支配されていることから、その 変動方向を示すベクトル  $e_r$  は PMOS の変動要因の成分が支配的となる. 同様にベク トルegはNMOSの変動要因の成分が支配的である.したがって、今考えている変動 変数空間では  $e_r$  と  $e_f$  は、ほぼ直交していると考えられる $^1$ . すなわち、

$$\boldsymbol{e}_{r}^{T}\boldsymbol{e}_{f}=0$$

である この性質は5.4 節で述べる応答曲面の合成に必要な実験計画に利用すること ができる.

## 5.4 応答曲面の合成

5.3節は簡単な1段構成のセルのワーストケースから、1次係数ベクトルの性質を 考察した.より複雑なセル.組合せ回路になると、信号経路上に立ち上がり、立ち 下がりが複数交じり合うことになる.このような場合のワーストケースは、今まで の単純なトランジスタの電流によるワーストケースでは解析できなくなる.

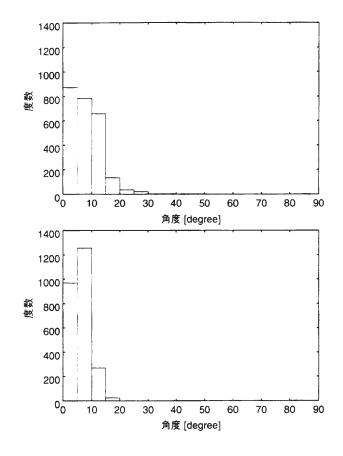

ワーストケースがどのようになるかを調べるために、経路の遅延時間の応答曲面 を考える。これは、1段ごとに応答曲面を求めておき、それらを足し合わせることで 求めることが出来る、遅延時間の対象となる経路上に、信号が立ち上がる1段構成 のセルが $m_r$ 個、立ち下がりが $m_r$ 個あるとする、個々のセルの応答曲面を式(5.5)の係数  $b_0, b_r, b_f$  に添字  $\{1, \ldots, m_r\}$ ,  $\{1, \ldots, m_f\}$  をつけて表す。経路の遅延は,以下 のように表される.