APPLIED PHYSICS LETTERS VOLUME 81, NUMBER 25 16 DECEMBER 2002

## Interface properties in metal-oxide-semiconductor structures on n-type 4H-SiC(03 $\bar{3}$ 8)

Hiroshi Yano, <sup>a)</sup> Taichi Hirao, Tsunenobu Kimoto, and Hiroyuki Matsunami Department of Electronic Science and Engineering, Kyoto University, Yoshidahonmachi, Sakyo, Kyoto 606-8501, Japan

Hiromu Shiomi

SiXON Ltd., 27-1 Saiin-Hidericho, Ukyo, Kyoto 615-0065, Japan

(Received 29 April 2002; accepted 24 October 2002)

The interface properties of  $SiO_2/4H$ - $SiC(03\overline{3}8)$  were characterized using n-type metal-oxide-semiconductor structures fabricated by wet oxidation. The interface states near the conduction band edge are discussed based on the capacitance and conductance measurements at a low temperature and room temperature. 4H- $SiC(03\overline{3}8)$  was found to have different energy distribution of the interface state density from the (0001) face. The shallow interface state density on  $(03\overline{3}8)$  is lower than on (0001) by a factor of 4 to 8. © 2002 American Institute of Physics.

[DOI: 10.1063/1.1529313]

Interface properties are the most important issues to determine the performance of metal-oxide-semiconductor (MOS) devices. As is the case with silicon (Si), silicon carbide (SiC) can be thermally oxidized to form silicon dioxide (SiO<sub>2</sub>). In addition to that, SiC has excellent physical properties, such as wide band gap and high breakdown field suitable for high-power and high-temperature devices. Combined with the above features, SiC MOS transistors are expected to have high switching speed and low energy loss at room temperature and even under high-temperature operation. However, poor interface properties of SiC MOS structures, especially in 4H-SiC, processed by standard thermal oxidation hinder the realization of high-performance SiC MOS transistors.

It is well known that the interface properties of MOS structures in Si strongly depend on the surface orientations, that is, Si(100) has the smallest interface state density and Si(111) has the largest one, and the situation of Si(110) sits between the above two faces.1 This is originated from the interface states of  $P_b$ -type dangling bonds. As for SiC, we have experimentally demonstrated that the interface properties of MOS structures also strongly depend on the surface orientations as follows: higher performance of MOS transistors and lower density of shallow interface states were obtained on 4H-SiC(11 $\bar{2}$ 0) compared to those on (0001).<sup>2-5</sup> The (0001) and (11 $\bar{2}$ 0) faces of hexagonal crystal structure correspond to the (111) and (110) faces of cubic structure, respectively. The origin of interface states in SiC MOS structures has not been clarified yet. For example, carbon clusters and near-interface oxide traps are suggested as origins for interface states.<sup>6</sup> The formation of these defects may be different on different surfaces, because Si and C atom arrangements on the surface affect the oxidation kinetics as the oxidation rate depends on the surface orientations.<sup>7</sup>

There may exist surface orientations other than the

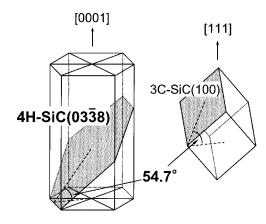

above two faces in 4H-SiC that can improve MOS transistor performance and MOS interface properties further. Although the origin of interface states is different, we have selected a new surface orientation, 4H-SiC(03 $\overline{3}8$ ), according to the Si analogy. The 4H-SiC(03 $\overline{3}8$ ) is semi-equivalent to 3C(cubic)-SiC(100), tilted by 54.7° toward  $\langle 01\overline{1}0 \rangle$  from (0001), as illustrated in Fig. 1. In this letter, the interface properties of MOS structures on 4H-SiC(03 $\overline{3}8$ ) were characterized, based on capacitance and conductance measurements, focusing on the interface states near the conduction band edge.

The starting materials were n-type 4H-SiC substrates with surface orientations of  $(03\overline{3}8)$  and (0001). 4H-SiC $(03\overline{3}8)$  substrates were prepared by slicing ingots grown on  $(000\overline{1})$  by a modified Lely method at SiXON Ltd. with an angle of  $54.7^{\circ}$  toward the  $\langle 01\overline{1}0 \rangle$  direction. N-type epitaxial layers were grown by standard atmospheric-pressure cold-wall chemical vapor deposition (CVD) at  $1520^{\circ}$ C using SiH<sub>4</sub> and C<sub>3</sub>H<sub>8</sub> as source gases and H<sub>2</sub> as a carrier gas. The net donor concentrations of epilayers were  $3.2 \times 10^{17}$  and  $8.7 \times 10^{16}$  cm<sup>-3</sup> for the  $(03\overline{3}8)$  and (0001) faces, respectively. The specular surface was successfully obtained by CVD growth on  $(03\overline{3}8)$  as well as on (0001). The

FIG. 1. Schematic illustrations of surface orientations for 4H-SiC( $03\overline{3}8$ ) and 3C-SiC(100).

a)Present address: Graduate School of Materials Science, Nara Institute of Science and Technology, 8916-5 Takayama, Ikoma, Nara 630-0101, Japan; electronic mail: h-yano@ms.aist-nara.ac.jp

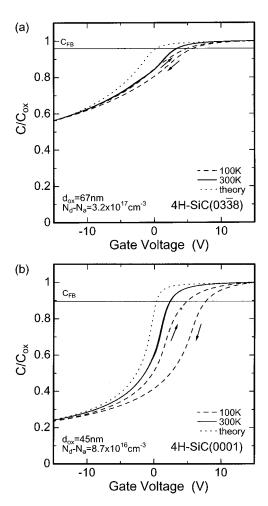

FIG. 2. High-frequency C-V characteristics of n-type 4H-SiC MOS capacitors on (a)  $(03\overline{3}8)$  and (b) (0001) faces. Solid and broken curves were taken at 300 and 100 K, respectively. Dotted curves indicate theoretical calculations. Injection-type hysteresis is observed.

samples were cleaned by an RCA method, and then loaded immediately into the oxidation furnace. Wet oxidation was performed at 1150 °C to grow a thermal oxide. The oxidation time/thickness were 25 min/67 nm for  $(03\overline{3}8)$  and 120 min/45 nm for (0001), which revealed that the oxidation rate for  $(03\overline{3}8)$  was 6–7 times faster than for (0001). After thermal oxidation, in situ post-oxidation annealing was carried out at 1150 °C for 30 min in Ar. Al was deposited on the surface as a gate electrode with a diameter of 300  $\mu$ m and also on the back side for an ohmic contact. Finally, postmetallization annealing was done in a forming gas (10% H<sub>2</sub>) in N<sub>2</sub>) at 400 °C for 30 min.

To characterize the interface properties, high-frequency (1 MHz) C-V characteristics were measured at room temperature (300 K) and at a low temperature (100 K) with a bias sweep rate of 0.1 V/s. The interface state density was calculated from the peak value of the parallel conductance measured in the frequency range of 1 kHz to 1 MHz at room temperature. 9,10 Both the capacitance and conductance measurements were done using an HP4284A precision LCR meter in an electrically shielded dark box.

Figures 2(a) and 2(b) show high-frequency C-V characteristics of 4H-SiC MOS capacitors on  $(03\overline{3}8)$  and (0001), respectively, measured at 300 K and 100 K. Note that the different slopes of the C-V curves are due to the difference of the net donor concentration and the oxide thickness for the two samples. At 300 K (solid curves in Fig. 2), a small hysteresis (<0.1 V) was observed for both samples. The flatband voltage shift is 3.1 V for the  $(03\overline{3}8)$  face and 2.0 V for the (0001) face. Although the flatband voltage shift on (0338) looks larger than on (0001), the effective oxide charge density calculated from the multiplication of the flatband voltage shift and the oxide capacitance (51.2 nF/cm<sup>2</sup> for  $(03\overline{3}8)$  and  $76.2 \text{ nF/cm}^2$  for (0001)) results in the same number of charges  $(1.0 \times 10^{12} \text{ cm}^{-2})$ , negative charges for both faces. These negative charges originated from both fixed charges and electrons trapped at interface states.

At a low temperature of 100 K (broken curves in Fig. 2), both the flatband voltage shift and hysteresis increased due to the existence of shallow interface states.<sup>5,11,12</sup> Relatively shallow interface states affect the flatband voltage shift, because electrons trapped at the interface states stay, and behave like fixed negative charges. As for quite shallow states, they become the origin of the injection-type hysteresis due to slow emission of electrons from the interface states during the voltage sweep. Neither shallow state has much effect on the C-V curves at room temperature. The flatband voltage shift at 100 K is 4.4 V for  $(03\overline{3}8)$  and 7.0 V for (0001), leading to the effective negative charge density  $(Q_{\text{eff}})$  of  $1.4 \times 10^{12}$  and  $3.3 \times 10^{12}$  cm<sup>-2</sup>, respectively. The increased ratio of the effective negative charge density from 300 to 100 K [ $Q_{\text{eff}}(100 \text{ K})/Q_{\text{eff}}(300 \text{ K})$ ] is 1.4 for (03 $\bar{3}$ 8) and 3.3 for (0001). This indicates that the interface state density on  $(03\overline{3}8)$  at relatively shallow energies is smaller than on (0001).

Compared with the change of the flatband voltage shift, the larger difference in the increase of hysteresis is observed for different surface orientations. Although the hysteresis under flatband condition at 300 K is very small for both faces, it increases to 0.9 V for  $(03\overline{3}8)$  and 2.9 V for (0001). The increase of hysteresis corresponds to the emitted electron density  $(Q_{\text{hvs}})$  of  $3.1 \times 10^{11} \text{ cm}^{-2}$  for  $(03\overline{3}8)$  and 1.4  $\times 10^{12}$  cm<sup>-2</sup> for (0001). In comparison with the value at room temperature  $[Q_{\text{hys}}(300 \text{ K}) \sim 3 \times 10^{10} \text{ cm}^{-2}]$ , the increased ratio  $[Q_{hys}(100 \text{ K})/Q_{hys}(300 \text{ K})]$  is 9.6 for  $(03\overline{3}8)$ and 41 for (0001). This means that the interface state density on (0001) increases toward the conduction band edge drastically, but that on  $(03\overline{3}8)$  does not. From the increase of the flatband voltage shift and hysteresis at the measurement temperatures from 300 to 100 K,  $SiO_2/4H-SiC(03\overline{3}8)$  is found to have smaller interface state density than (0001) near the conduction band edge.

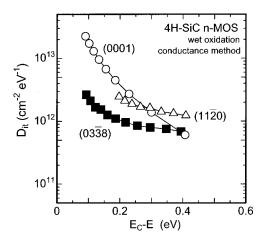

The distribution of interface state density  $(D_{it})$  as a function of energy from the conduction band edge  $(E_C)$  is shown in Fig. 3 for both  $(03\overline{3}8)$  and (0001) faces. At deep energies of  $E_C$ -E>0.4 eV,  $D_{it}$  on (03 $\bar{3}$ 8) tends to be larger than on (0001). However, the slope of the distribution of  $D_{\rm it}$  on  $(03\overline{3}8)$  is not as steep as that on (0001). Therefore, the  $(03\overline{3}8)$  sample has lower  $D_{it}$  than the (0001) sample at shallow energies of  $E_C$ –E<0.3 eV, which verifies the previous argument based on the temperature dependence of the C-Vcurves shown in Fig. 2. Between the energy range of  $E_{\rm C}$  $-E = 0.1 - 0.2 \text{ eV}, D_{\text{it}} \text{ on } (03\overline{3}8) \text{ is smaller than on } (0001)$ by a factor of 4 to 8. The data on  $(11\overline{2}0)^{13}$  are also indicated in Fig. 3 for comparison. The  $(03\overline{3}8)$  sample gives a half

Downloaded 24 Dec 2006 to 130.54.130.229. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 3. Distribution of interface state density ( $D_{\rm it}$ ) evaluated from conductance method.

value of  $D_{\rm it}$  on (11 $\overline{20}$ ) in the whole energy range monitored in this experiment. The different  $D_{\rm it}$  profiles in Fig. 3 for various surface orientations suggest that origins of interface states (for example, carbon clusters, near-interface oxide traps, dangling bonds, and so on) and their numbers are different for these faces. More detailed investigation is needed to clarify the origin of interface states of SiC MOS structures.

Obtaining small  $D_{it}$  values near the conduction band edge is important for SiC MOS structures, because the performance of SiC MOS transistor is mainly limited by the interface states at shallow energies.<sup>14</sup> As a matter of fact, we have fabricated 4H-SiC MOS transistors on  $(03\overline{3}8)$ ,  $(11\overline{2}0)$ , and (0001) faces using the same oxidation process (wet oxidation at 1150 °C) as described in this letter, and obtained higher effective channel mobility on  $(03\overline{3}8)(\sim 11 \text{ cm}^2/\text{Vs})$ than on  $(11\overline{2}0)(\sim 6 \text{ cm}^2/\text{Vs})$  and  $(0001)(\sim 4 \text{ cm}^2/\text{Vs})$ . 15 The channel mobilities obtained here on  $(03\overline{3}8)$  and  $(11\overline{2}0)$ are not so high compared to our previously reported value  $(\sim 30 \text{ cm}^2/\text{Vs})$  on  $(11\bar{2}0)$ ,  $^{2-4}$  probably due to immature fabrication processes. We believe that much higher channel mobility could be obtained on  $(03\overline{3}8)$  by improving the fabrication process of MOS transistors as well as optimizing the oxidation conditions.

In summary, the interface properties of n-type MOS structures with wet oxides on 4H-SiC(03 $\overline{3}8$ ) were characterized. High-frequency C-V characteristics measured at a low temperature indicated a large flatband voltage shift and hysteresis on (0001), while those on (03 $\overline{3}8$ ) were small. This implies that MOS structures on (03 $\overline{3}8$ ) have smaller interface states at shallow energies than on (0001), which was verified by the measurement of interface state density using the conductance method at room temperature. The interface state density on (03 $\overline{3}8$ ) at shallow energies was 4 to 8 times smaller than on (0001), leading to higher channel mobility on 4H-SiC(03 $\overline{3}8$ ). Therefore, the (03 $\overline{3}8$ ) face of 4H-SiC is a promising surface orientation for realizing high-performance MOS devices on 4H-SiC.

This work was supported by a Grant-in-Aid for Specially Promoted Research, No. 09102009, from the Ministry of Education, Culture, Sports, Science and Technology of Japan. The authors express their gratitude to Kyoto University Venture Business Laboratory (KU-VBL) for the partial support to this work.

<sup>&</sup>lt;sup>1</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (Wiley, New York, 1981) p. 385.

<sup>&</sup>lt;sup>2</sup>H. Yano, T. Hirao, T. Kimoto, H. Matsunami, K. Asano, and Y. Sugawara, IEEE Electron Device Lett. **20**, 611 (1999).

<sup>&</sup>lt;sup>3</sup> H. Yano, T. Hirao, T. Kimoto, H. Matsunami, K. Asano, and Y. Sugawara, Mater. Sci. Forum 338–342, 1105 (2000).

<sup>&</sup>lt;sup>4</sup>H. Yano, T. Hirao, T. Kimoto, and H. Matsunami, Jpn. J. Appl. Phys., Part 1 39, 2008 (2000).

<sup>&</sup>lt;sup>5</sup> H. Yano, T. Kimoto, and H. Matsunami, Mater. Sci. Forum 353–356, 627 (2001).

<sup>&</sup>lt;sup>6</sup>V. V. Afanas'ev, M. Bassler, G. Pensl, and M. Schulz, Phys. Status Solidi A 162, 321 (1997).

<sup>&</sup>lt;sup>7</sup>K. Ueno, Phys. Status Solidi A **162**, 299 (1997).

<sup>&</sup>lt;sup>8</sup> K. Nakayama, Y. Miyanagi, H. Shiomi, S. Nishino, T. Kimoto, and H. Matsunami, Mater. Sci. Forum 389–393, 123 (2002).

E. H. Nicollian and A. Goetzberger, Bell Syst. Tech. J. 46, 1055 (1967).

J. R. Brews, Solid-State Electron. 26, 711 (1983).

<sup>&</sup>lt;sup>11</sup> V. V. Afanas'ev, A. Stesmans, M. Bassler, G. Pensl, and M. J. Schulz, Appl. Phys. Lett. **76**, 336 (2000).

<sup>&</sup>lt;sup>12</sup> M. Bassler, V. Afanas'ev, G. Pensl, and M. Schulz, Mater. Sci. Forum 338–342, 1065 (2000).

<sup>&</sup>lt;sup>13</sup> H. Yano, T. Kimoto, and H. Matsunami, Appl. Phys. Lett. 81, 301 (2002).

<sup>&</sup>lt;sup>14</sup>R. Schörner, P. Friedrichs, D. Peters, and D. Stephani, IEEE Electron Device Lett. 20, 241 (1999).

<sup>&</sup>lt;sup>15</sup> T. Hirao, H. Yano, T. Kimoto, H. Matsunami, and H. Shiomi, Mater. Sci. Forum **389–393**, 1065 (2002).