# LOW THERMAL EXPANSION OF ELECTRODEPOSITED COPPER IN THROUGH SILICON VIAS

DINH VAN QUY

# LOW THERMAL EXPANSION OF ELECTRODEPOSITED COPPER IN THROUGH SILICON VIAS

(シリコン貫通電極での銅めっきと低熱膨張特性)

Graduate School of Energy Science,

Kyoto University

DINH VAN QUY

2020

# Table of contents

| СНАРТ  | ΓER   | 1: INTRODUCTION                                    | 1      |

|--------|-------|----------------------------------------------------|--------|

| 1.1.   | Bao   | ckground of Research                               | 1      |

| 1.1    | .1.   | Three-Dimensional Integrated Circuits (3DICs)      | 1      |

| 1.1    | .2.   | Through Silicon Via (TSV)                          | 4      |

| 1.1    | .3.   | TSV Challenges                                     | 15     |

| 1.2.   | Rev   | view of Existing Research                          | 20     |

| 1.2    | .1.   | High Speed TSV Filling                             | 20     |

| 1.2    | 2.    | TEC Mismatch Challenges: Copper Pumping and KOZ    | 21     |

| 1.3.   | Ab    | stract of Research                                 | 25     |

| 1.4.   | Ret   | ferences                                           | 28     |

| СНАРТ  | ΓER 2 | 2: BOTTOM-UP TSV FILLING USING SULFONATED DIALLYL  |        |

| DIMET  | ΉYΙ   | L AMMONIUM BROMIDE COPOLYMER AS A LEVELER          | 35     |

| 2.1. I | ntroc | luction                                            | 35     |

| 2.2. E | Exper | rimental                                           | 35     |

| 2.3. F | Resul | ts and Discussion                                  | 37     |

| 2.4. 0 | Concl | lusions                                            | 41     |

| 2.5. F | Refer | ences                                              | 42     |

| СНАРТ  | ΓER ( | 3: LOW THERMAL EXPANSION ELECTRODEPOSITED COPPER A | ND ITS |

| CONT   | RAC   | TION MECHANISM BY ANNEALING                        | 43     |

| 3.1. I | ntroc | luction                                            | 43     |

| 3.2 E  | xperi | imental                                            | 44     |

| 3 3 E  | Resul | ts and Discussion                                  | 46     |

| 3.4. Conclusions                                          |           |

|-----------------------------------------------------------|-----------|

| 3.5. References                                           | 53        |

| CHAPTER 4: THERMAL STRES REDUCTION OF COPPER THROUGH SI   | LICON VIA |

| (TSV) WITH ANNEALING.                                     | 54        |

| 4.1. Introduction                                         | 54        |

| 4.2. Experimental                                         | 55        |

| 4.3. Results and Discussion                               | 56        |

| 4.4. Conclusions                                          | 65        |

| 4.5. References                                           | 66        |

| CHAPTER 5: ELECTROCHEMICAL BEHAVIOR OF 2M5S AND ITS INFLU | JENCE ON  |

| REDUCTION OF COPPER PUMPING AND KEEP-OUT ZONE             | 67        |

| 5.1. Introduction                                         | 67        |

| 5.2. Experimental                                         | 68        |

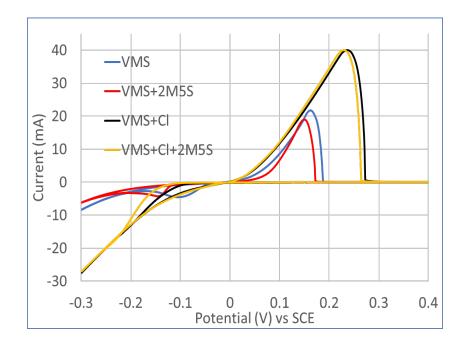

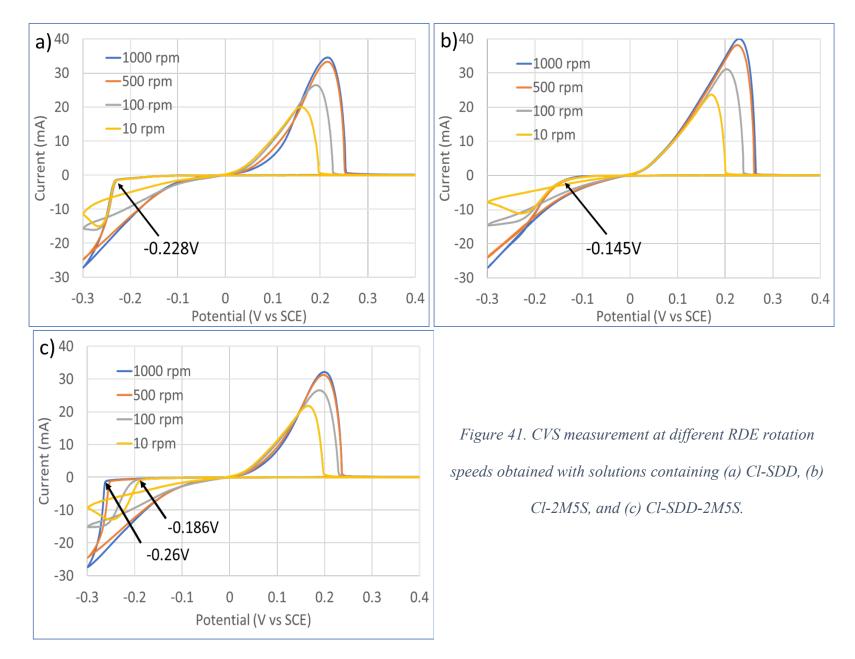

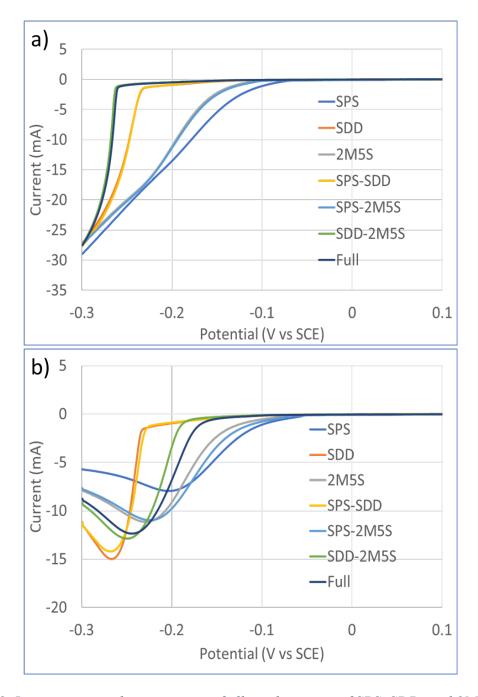

| 5.3. Results and Discussion                               | 70        |

| 5.4. Conclusions                                          |           |

| 5.5. References                                           |           |

| CHAPTER 6: SUMMARY                                        |           |

| Acknowledgements                                          |           |

| List of Publications                                      |           |

| List of Presentations                                     |           |

# **CHAPTER 1: INTRODUCTION**

#### 1.1. Background of Research

# 1.1.1. Three-Dimensional Integrated Circuits (3DICs)

The progress of semiconductor devices is predicted by Gordon Moore's statement in 1965, known as Moore's law. According to Moore's law, the number of transistors per Integrated Circuit (ICs) doubles about every two years<sup>1</sup>. Significant efforts have been made to keep up with Moore's Law, and more and more transistors have been mounted on the same chip in the last 50 years. However, as transistor scaling reaches physical limits and the associated costs rise dramatically, continually increasing the number of integrated transistors requires new innovations in ICs. Three-Dimensional Integrated Circuits (3DICs) have emerged as a promising technology that has attracted much attention in recent years. Since transistor to the lower transistor is Through Silicon Via (TSV) in 3DIC.

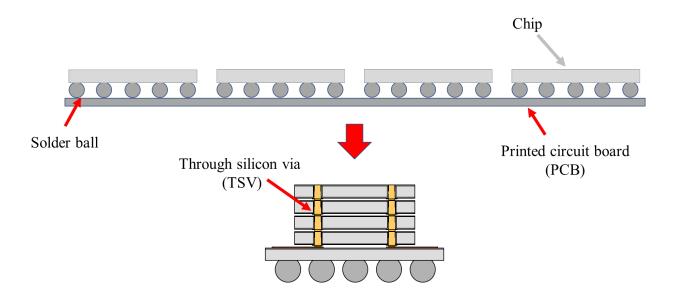

Figure 1. Schematic diagram showing the concept of 2DIC packaging and 3DIC packaging [2].

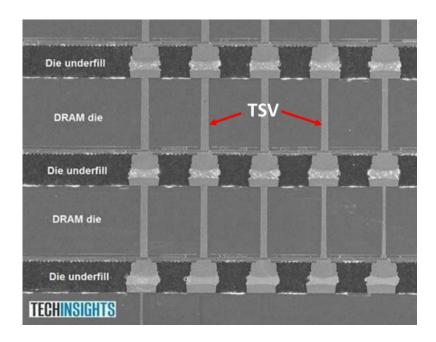

Figure 1 illustrates the schematic of traditional 2DIC packaging and 3DIC packaging<sup>2</sup>. The upper graph in Figure 1 is the concept of traditional 2D packaging, where four chips are mounted horizontally on a printed circuit board (PCB) by solder bumps. Assuming a chip size of 1 cm, the signal transmission length from the first chip to the fourth chip is 4 cm. On the other hand, the lower graph in Figure 1 illustrates the concept of 3D packaging where four chips are stacked vertically using TSV interconnects. Since four chips are stacked vertically, the packing size is reduced by a factor of four. In addition, since the thickness of silicon chip is only several tens micrometers, stacked chips with TSVs provide the shortest interconnection between different chips. Therefore, 3DIC packaging is the most promising technology that allow to achieve lower power consumption, smaller form factor, higher performance, and more functional devices<sup>3,4</sup>. For example, High Bandwidth Memory (HBM) is a TSV technology-based device. Samsung and SK Hynix are the leader in this market. Figure 2 shows a cross section image of the HBM device produced SK Hynix with 4 DRAM chips (dies) are interconnected through TSVs<sup>5</sup>.

Figure 2. SEM image of HBM with TSV technology (Source: Package Analysis of the SK-Hynix HBM, TechInsights).

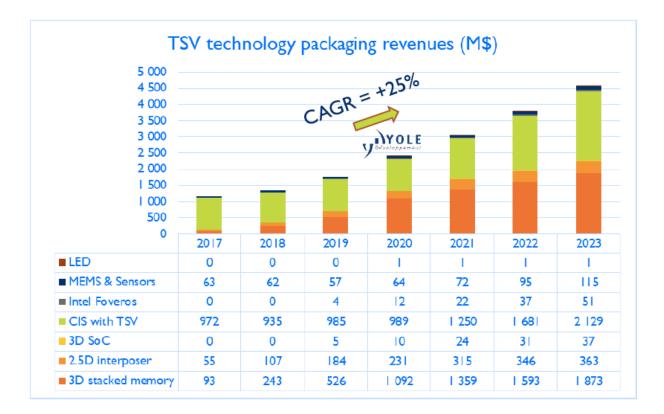

*Figure 3. Global TSV technology packaging market (Source: 2.5D / 3D TSV & wafer-level stacking technology & market updates 2019 report by Yole Development.).*

The global TSV technology packaging market given by Yole Development is shown in Figure 3. TSV technology has a bright future with a Compound Annual Growth Rate (CAGR) of 25%. In addition, TSV packaging revenue is estimated to increase to about \$ 4.5 billion in 2023, as shown in Figure 3. TSVs is now the preferred interconnect choice for high performance 3D stacked memory and CMOS Image Sensor (CIS). They are also an enabling technology for heterogeneous integration of logic circuits with silicon interposers, Micro Electro Mechanical Systems (MEMS), and sensors. New players who historically were not TSV adopters, such as Intel, are entering TSV market. For example, Intel has entered the TSV market in 2019 with the introduction of Intel Foveros, an advanced 3D face-to-face die stacking packaging process. In the near future, TSVs will also enable Light Emitting Diode (LED) and photonics. CIS accounted for more than 80% of the TSV market in 2017, although this will fall to about 46% by 2023. This is mainly due to the growth of the other TSV applications, led by

3D stacked memories, silicon interposers, MEMS and sensors. The TSV markets for Intel Foveros and 3D System on Chip (SoC) are expected to reach around \$51 million and \$37 million by 2023, respectively.

# 1.1.2. Through Silicon Via (TSV)

## 1.1.2.1.Via First, Via Middle, and Via Last Process

Through-silicon via (TSV) is the core of 3DIC technology. The TSV concept was invented by William Shockley in 1956<sup>6</sup>, and was further developed by in 1964 by IBM researchers M. Smith and E. Stern<sup>7</sup>. At the beginning, TSV was not originally intended for 3DIC. The first 3DIC stacked chips fabricated with a TSV process were invented in 1980s in Japan<sup>8</sup>. Depending on the order of TSV formation step to the transistor formation step (or FEOL: Front End of Line) and wiring step (or BEOL: Back End of Line), TSV fabrication is categorized as via first, via middle, and via last process.

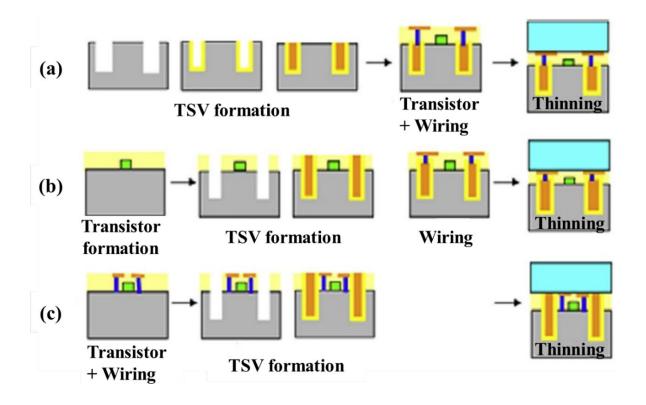

Figure 4 shows the schematic flow of via first, via middle, and via last processes<sup>9</sup>. In the via first process, TSVs are fabricated before the transistor formation and wiring step. Meanwhile, TSVs are made between the transistor formation and wiring step in the via middle process. Finally, in the via last process, TSVs are manufactured after the formation of transistor formation and wiring step. Among these processes, via middle is the most common used in the industry for achieving the highest. The major drawback of the via middle process is that TSV is exposed to very high temperature (400-600°C) during insulator formation step. This high exposure temperature causes some serious reliability problems, leading to the failure of electronic devices. In addition, the TSV formation (especially, TSV etching, Cu electrodeposition, and Cu CMP) in via middle process is expensive. These problems are discussed in more detail in section "1.1.3. TSV challenges" of this thesis.

Figure 4. Schematic flow of (a) via first, (b) via middle, and (c) via last processes [9].

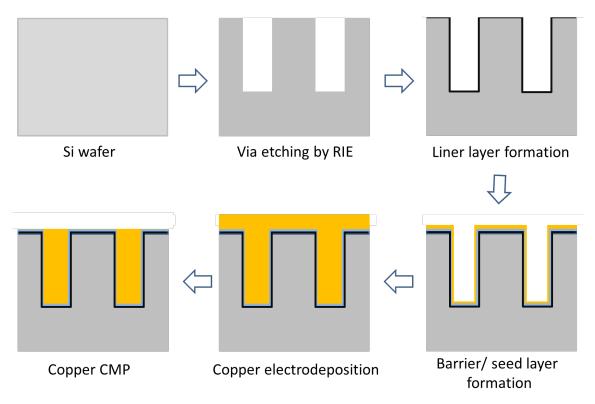

Figure 5. Schematic flow of TSV formation process.

# 1.1.2.2. TSV Formation Process

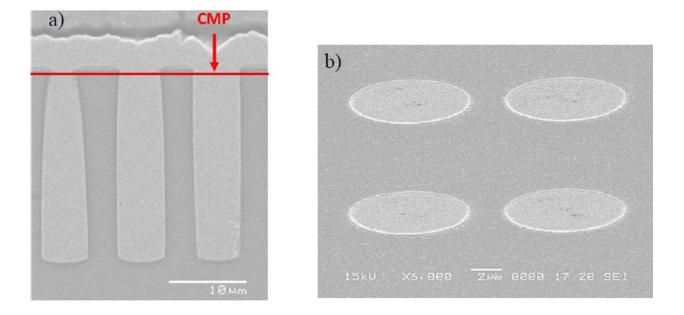

Typical TSV formation process is shown in Figure 5. The first step is via etching by Reactive Ion Etching (RIE). Next, an insulator layer, a barrier layer, and a seed layer are formed. After that, TSV is filled by copper electrodeposition. Finally, TSV is polished to remove copper overburden by Chemical Mechanical Polishing (CMP).

# 1.1.2.2.1. TSV Etching

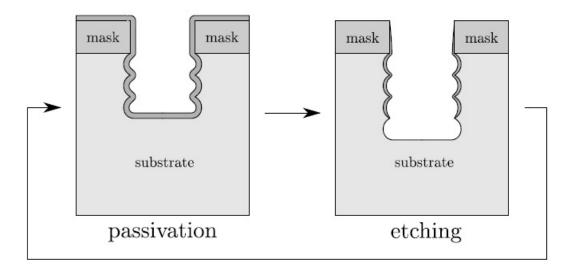

TSV etching is primarily done by using RIE to create high aspect ratio vias. The most commonly used process for TSV RIE is the Bosch process. The Bosch process basically executes two steps alternately, one etching step followed by a passivation step, as shown in Figure  $6^{10}$ . Sulfur hexafluoride (SF<sub>6</sub>) is commonly used as an etchant for silicon etching in the etching step. Octafluorocyclobutane (C<sub>4</sub>F<sub>8</sub>) gas, on the other hand, is used in the passivation step and produces a good passivation film to prevent lateral silicon etching during the next etching step<sup>10,11</sup>. During the Bosch process, a residual passivation film remains at the bottom of the TSV as an etching byproduct<sup>12,13</sup>. The residual passivation film prevents subsequent metal deposition. Therefore, additional de-passivation step by using O<sub>2</sub> and Ar plasma is used to remove the residual passivation film at the bottom of the TSV<sup>13</sup>.

TSV etching using the Bosch process has challenges, such as controlling the roughness of the sidewalls and the uniformity of via depth<sup>14</sup>. These challenges can be minimized by optimizing the processing parameters in both the etching and passivation steps, since the etching rate, uniformity, and selectivity are highly dependent on the processing parameters in both the etching and passivation steps.

Figure 6. Schematic of Bosch process [10].

## 1.1.2.2.2. Dielectric Insulator Layer

To sufficient insulate the filled copper from the surrounding silicon substrate, a dielectric insulator is essential for the TSV. Typical requirements for a TSV dielectric layer include good step coverage and thickness uniformity, low stress, no leakage current, and high breakdown voltage<sup>14,15</sup>. The most commonly used material for TSV insulator is  $SiO_2^{16-19}$ . The methods for depositing the SiO<sub>2</sub> insulator depends on the TSV integration process (via first, via middle, and via last process). There are basically two options for insulator deposition, namely: Plasma-Enhanced Chemical Vapor Deposition (PECVD) of SiO<sub>2</sub>, Atmospheric Pressure Chemical Vapor Deposition (APCVD) of SiO<sub>2</sub>. The PECVD process uses liquid tetraethyl orthosilicate (TEOS) Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub> as a source of silicon. The growth rates SiO<sub>2</sub> films by PECVD are high and the process temperature is lower than 400°C<sup>19</sup>. The APCVD process uses tetraethyl orthosilicate (TEOS) Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub> and O<sub>3</sub> as the precursors. By using O<sub>3</sub> instead of O<sub>2</sub>, the deposition temperature can be reduced in the range of 400°C-600°C<sup>17,18</sup>. However, since SiO<sub>2</sub> formed by APCVD has a high residual stress, the thickness of APCVD SiO<sub>2</sub> should be less than 0.5  $\mu$ m<sup>20</sup>.

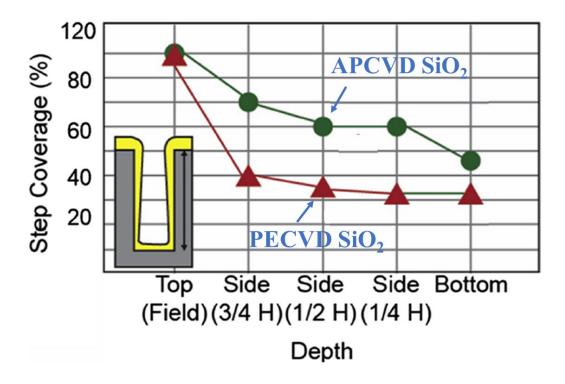

Figure 7. Comparison of step coverage of SiO<sub>2</sub> formed by APCVD and PECVD from top to bottom of TSV [21].

Figure 7 compares step coverage of SiO<sub>2</sub> between APCVD and PECVD from the top of the TSV, along the sidewalls, to the bottom<sup>21</sup>. The x-axis is the comparison position along the TSV, and the y-axis is the step coverage. In Figure 7, the step coverage decreases continuously for both PECVD and APCVD as the distance goes from top to bottom of the TSV. However, it can be seen that the uniformity of SiO<sub>2</sub> formed by PECVD at all positions except the top of the via is less than 50%. In contrast, APCVD SiO<sub>2</sub> has better step coverage than PECVD SiO<sub>2</sub>, and therefore APCVD is commonly used to form the SiO<sub>2</sub> insulator<sup>16,19,21</sup>.

# 1.1.2.2.3. Barrier and Seed layer

After deposition of the dielectric insulator, a barrier layer is formed, followed by a copper seed layer. The barrier layer not only acts as an adhesion layer between the dielectric layer and the filled copper, but also prevents copper diffusion during the annealing process. The commonly used materials as barrier layer are Ti, Ta, TiN, and TaN<sup>22–24</sup>. Depending on the

size of the TSV, Physical Vapor Deposition (PVD) and Chemical Vapor Deposition (CVD) are used to deposit the barrier layer. Ta and Ti barrier layers can be deposited using the PVD method. The advantage of the PVD method is that the temperature during deposition is low. However, for high aspect ratio TSVs (> 10: 1), PVD is inappropriate because of poor step coverage<sup>25</sup>. TiN or TaN barrier layers are typically deposited using the CVD method. Compared with the PVD method, the CVD method formed a more uniform barrier layer, but required a higher deposition temperature.

In the next step, copper seed is deposited on the barrier layer by PVD before filling the TSV with the copper electrodeposition process.

# 1.1.2.2.4. Copper Electrodeposition

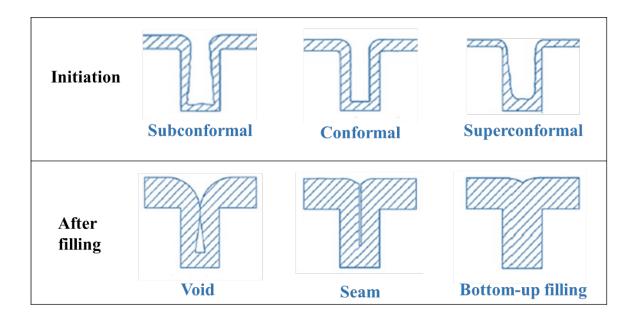

After the barrier and seed layer deposition, the TSV is filled by electrodeposition. Copper is widely used as a filling material for TSV because of its low resistivity. There are three possibility of TSV filling profiles, as shown in Figure 8<sup>26</sup>. In the subconformal profile, the copper electrodeposition rate at the TSV opening is higher than at the via bottom. This difference in electrodeposition rate causes a narrowing of the TSV opening, leading to void formation when electrodeposition process is complete. In the conformal profile, copper is electrodeposited at the same rate on TSV opening, TSV sidewall, and TSV bottom. Subconformal electrodeposition results in the appearance of seams at the final stage of TSV filling. Subconformal and conformal profile are caused by the depletion limit of cupric ions inside the TSV<sup>27</sup>. Void and seam cause reliability problems. Therefore, the optimal filling profile is superconformal (or bottom-up filling) where the copper electrodeposition rate at the bottom of the TSV is greater than that at the TSV opening.

# Figure 8. Common copper filling profiles in TSV [26].

Copper sulfate and sulfuric acid are the basic components of the electrolytes that are widely used in the industry for copper electrodeposition. Copper sulfate acts as the source of copper ions, and sulfuric acid increases the conductivity of the electrolyte. In addition, chloride ion, a set of organic additives (inhibitor, accelerator, and leveler), and Periodic Pulse Reverse (PPR) current are used to accelerate electrodeposition rate at the via bottom and inhibit the electrodeposition rate at the via outside.

# Additives chemistry

The HCl serves as a source of Cl<sup>-</sup> ions, plays an important role in electrodeposition of copper, including promoting accelerator and supporting inhibitor by forming the complexes with accelerator and inhibitor<sup>28,29</sup>.

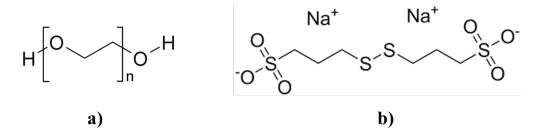

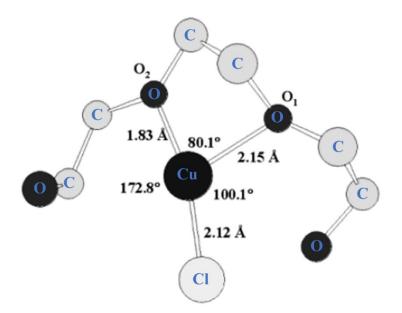

A first type of organic additive used for copper electrodeposition is the inhibitor (suppressor). Inhibitors are usually long-chain polymers (molecular weight 1000-20000). Inhibitor is mainly adsorbed on the via outside, on the via sidewall near the via opening, and inhibits copper electrodeposition at these positions. The most commonly used inhibitor is polyethylene glycol (PEG), which has the chemical structure shown in Figure 9. Inhibitors inhibit electrodeposition by adsorbing on the copper surface. However, PEG alone does not readily adsorb to the copper surface. In the presence of Cl<sup>-</sup> ions, the adsorption strength of PEG on the copper surface is greatly increased, resulting in a significant inhibition of copper electrodeposition. The formation of Cu-Cl-PEG complex has been widely used to explain the strong adsorption of PEG on copper surfaces in the presence of Cl<sup>-</sup> ions<sup>30–33</sup>. Based on a surface-enhanced Raman spectroscopy study, Z. V. Feng et al. proposed a structural model for the Cu-Cl-PEG complex, as shown in Figure 10<sup>33</sup>. In this model, a cuprous center is complexed by two ether oxygen ligands from PEG and one Cl<sup>-</sup> ligand.

Figure 9. Chemical structures of (a) PEG, and (b) SPS.

# Figure 10. Structural model of a Cu-Cl-PEG complex [33].

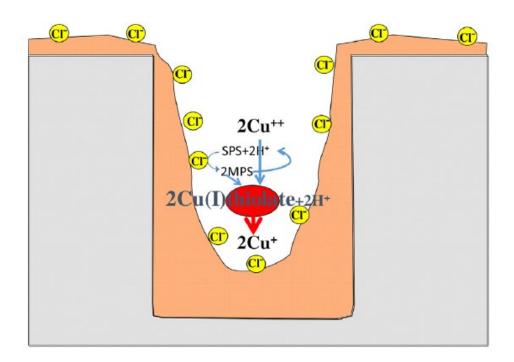

A second type of organic additive is the accelerator (brightener). Accelerators are small molecules, usually sulfur-containing compounds. The accelerator blocks the adsorption of the inhibitor and slowly replaces it. It also penetrates inside the via and increases the electrodeposition rate at the via bottom. A well-known accelerator used in the industry is Bis(3-sulfopropyl) disulfide (SPS), as shown in Figure 9. Similar to PEG, SPS requires the support of Cl<sup>-</sup> ion to accelerate copper electrodeposition. Several researches have been conducted on the acceleration mechanism of SPS<sup>34–36</sup>. The two famous mechanisms are curvature enhanced accelerator coverage proposed by T. P. Moffat et al.<sup>34</sup>, and cuprous ion related mechanism proposed by K. Kondo et al.<sup>36</sup>, as shown in Figure 11. First, SPS is reduced to MPS by the adsorbed chloride. Next, MPS reacts with cupric ions to form Cu(I)thiolate complex intermediate. After that, the Cu (I) thiolate complex floats to the via bottom due to the vortex. Cu(I)thiolate complex is then oxidized to SPS, releasing cuprous ion. The released cuprous ion is quickly electrodeposited as copper, causing acceleration at the bottom of the via.

Figure 11. Model of SPS acceleration mechanism [36].

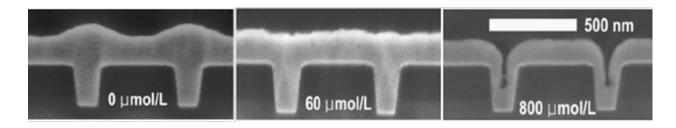

A third type of organic additive is the leveler. There are thousands of types of levelers, usually quaternary nitrogen compounds. Levelers disable the accelerator, and exhibit an inhibition effect during copper electrodeposition. Levelers are also used to reduce the thickness of the overburden to improve overall flatness. Figure 12 shows the changes in the surface of copper electrodeposited at different concentrations of the leveler<sup>37</sup>. Copper bumps are clearly

observed in the absence of the leveler, but disappear at the leveler of 60  $\mu$ mol/L. For 800  $\mu$ mol/L of leveler, the TSV is not completely filled and voids may form. This is probably due to excessive leveler diffusion into the TSV, reducing copper electrodeposition rate at the TSV bottom. Moreover, in the Chapter 3-5 of this thesis, I have found out that another function of the leveler is to reduce the thermal expansion of electrodeposited copper.

Figure 12. Leveler concentration dependence of electrodeposited copper surface. [37].

# Periodic pulse reverse (PPR) current

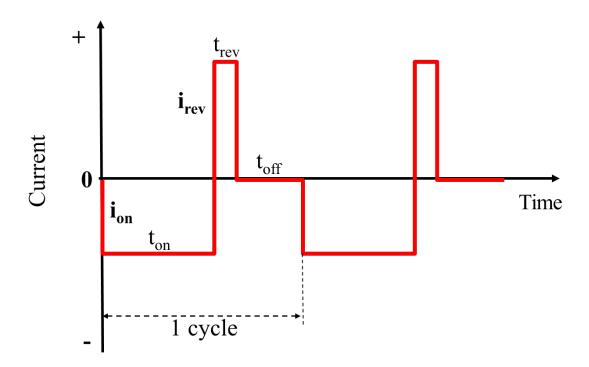

Periodic pulse reverse (PPR) current has been widely in copper electrodeposition for TSV filling. Figure 13 illustrates a typical PPR current waveform. In Figure 13, i<sub>on</sub> and i<sub>rev</sub> stand for the cathodic current (or electrodeposition current) and anodic current (or stripping current), respectively, and t<sub>on</sub>, t<sub>rev</sub> and t<sub>off</sub> stand for the electrodeposition time, stripping time and pause time, respectively.

The cuprous (Cu<sup>+</sup>) ion plays very important role in the bottom-up TSV filling. K. Kondo et al. verified the relation between the Cu<sup>+</sup> ions and the acceleration effect of the accelerator at the via bottom<sup>38</sup>. Based on an electrochemical method, J. R. White found that the Cu<sup>+</sup> ions in copper dissolution were 1000 times higher than that during electrodeposition<sup>39</sup>. This means that as the reverse current of the PPR current increases, the Cu<sup>+</sup> ion concentration inside the via increases, and the bottom-up TSV filling is achieved<sup>40</sup>. All five parameters of the PPR current can be easily controlled, so the PPR current reduces voids and improves TSV filling performance.

Figure 13. A typical periodic pulse reverse (PPR) current waveform.

# 1.1.2.2.5. Copper Chemical Mechanical Polishing (CMP)

After copper electrodeposition step, the copper overburden must be removed by a planarization process called chemical mechanical polishing (CMP). In CMP, the wafer is placed face down on a rotating pad where the slurry is dispensed. Normally, copper CMP consists of a minimum of two steps. The first step is the removal of copper overburden stopping at the barrier layer. The second step is to remove the barrier layer that stops at the dielectric insulator layer.

# 1.1.3. TSV Challenges

# 1.1.3.1. High Speed TSV Filling

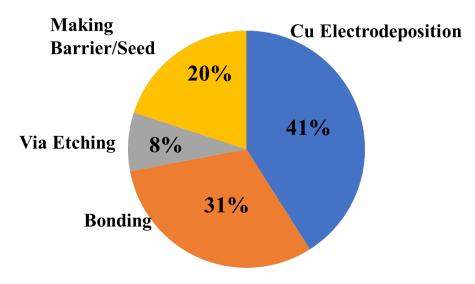

Figure 14 is a pie chart of the breakdown of TSV production costs<sup>41</sup>. In Figure 14, copper electrodeposition, bonding, barrier/seed layer formation, and via etching costs account for 41%, 31%, 20% and 8% of total TSV production cost, respectively. In other words, copper electrodeposition is the most expensive step of TSV production process. Therefore, TSV cost savings are largely managed by copper electrodeposition cost reduction. There are several ways to reduce the cost of copper electrodeposition, including using latest electrodeposition tools and reducing the time required for electrodeposition. However, the latest electrodeposition tools are expensive. Furthermore, large clean room areas need to accommodate a large amount of electrodeposition tools. Therefore, electrodeposition time must be reduced to reduce TSV production costs. Increasing current density is a promising solution to reduce electrodeposition time. However, if the current density is too high, constriction occurs at the TSV opening and voids will be formed. Acid residues remaining in the voids can cause reliability problems. Therefore, high speed TSV filling without voids is important and it will be examined in this research.

Figure 14. TSV production cost [41].

# 1.1.3.2. Thermal Expansion Coefficient (TEC) Mismatch Problems

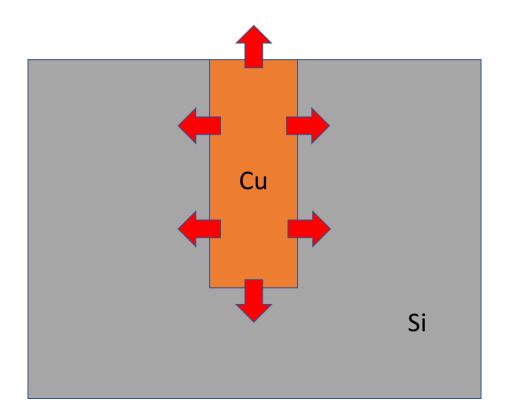

Copper is widely used as a filling material for TSV because of its low resistivity. Despite the advantages of using copper as the filling material, copper TSV has its drawback due to thermal expansion coefficient (TEC) mismatch between copper and surrounding silicon. Copper has a high thermal expansion coefficient (TEC) of  $17x10^{-6}$ /°C, while the TEC of silicon is only  $2x10^{-6}$ /°C. During the SiO<sub>2</sub> formation of the wiring step in via middle process, copper TSV is exposed to a high temperature between 400°C and 600°C. As shown in Figure 15, due to the large thermal expansion coefficient (TEC) mismatch between the silicon substrate and copper, copper expands much more than silicon, causing high thermal stresses in all directions during the manufacturing process. These thermal stresses can lead to failure of the microelectronic device.

*Figure 15. TEC mismatch induced thermal stress in TSV structure.*

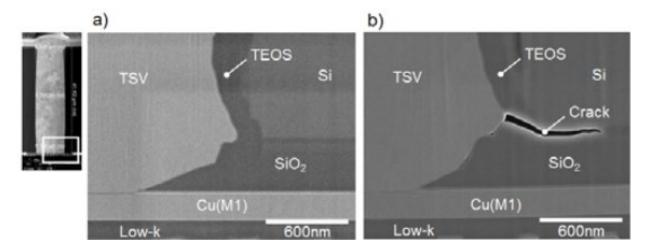

However, at the bottom corner of the TSV, the thermal stress due to the mismatch of TEC between copper and silicon cannot be released. The Thermal stress causes cracks in the

silicon at the bottom corner of the TSV<sup>42,43</sup>. Figure 16 shows the cross-sectional SEM images of TSV after annealing at 200°C, and 400°C cyclic annealing. In Figure 16a, no cracks are observed in the bottom corner of TSV after post annealing at 200°C. However, when the annealing temperature rises to 400°C, long cracks are seen in the silicon, as shown in Figure 16b. Crack in silicon can cause leakage currents into the silicon bulk, leading to serious TSV reliability problems.

Figure 16. Cross sectional SEM image of TSV (a) after annealing at 200 °C, and (b) after 400 °C cyclic annealing [43].

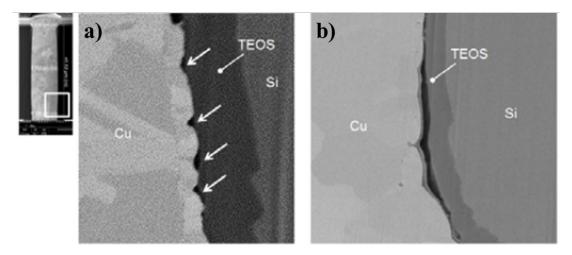

In addition, thermal stress also causes voids and delamination<sup>43–45</sup> at the copper-silicon interface. Figure 17 shows a cross-sectional SEM images of the interface between copper and the dielectric layer after annealing at 200°C, and 400°C cyclic annealing. After annealing at 200°C, there are small voids along the interface between the copper and the dielectric layer, as shown in Figure 17a. Furthermore, as the annealing temperature rises to 400°C, voids become larger, causing delamination at the interface between the copper and the dielectric layer. Voids and delamination are attributed to the poor adhesion and poor coverage of the dielectric insulator layer.

*Figure 17. Cross sectional SEM image of interface between copper and dielectric layer (a) after annealing at 200 °C, and (b) after 400 °C cyclic annealing [43].*

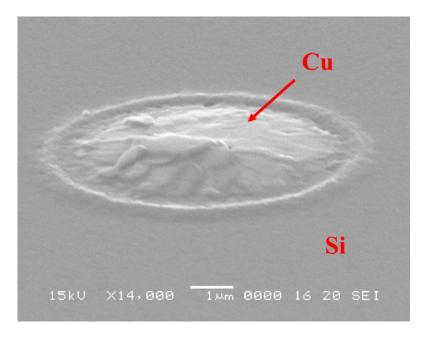

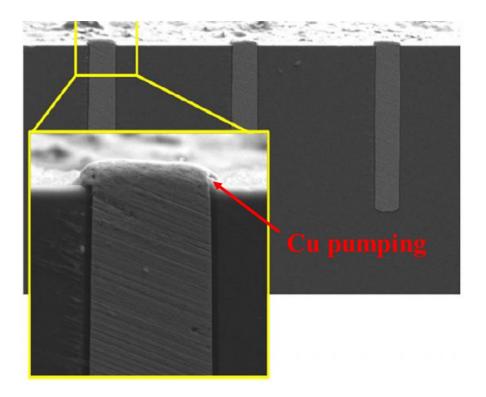

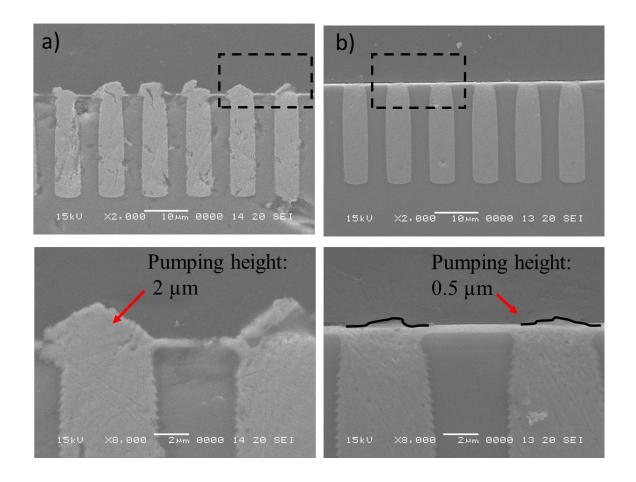

The upward thermal stress in Figure 15 is partially relieved by copper pumping<sup>46-48</sup>. Figure 18 is a top-view SEM image of copper pumping by annealing and Figure 19 is the cross section of copper TSV after annealing. In both Figure 18 and 19, copper pumping is evident with the copper height is higher than the silicon surface when annealing. However, copper pumping destroys the wiring above the TSV. Therefore, copper pumping also raises reliability problems.

Figure 18. Top-view SEM image of copper pumping in TSV.

Figure 19. Cross-sectional SEM image showing copper pumping after annealing [48].

Figure 20. Keep out zone (KOZ) area around the TSV.

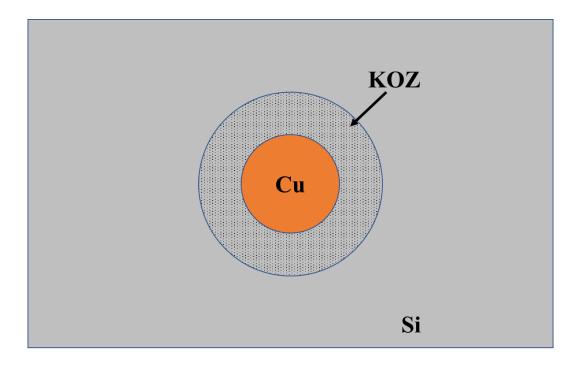

Due to the TEC mismatch between copper and silicon, the silicon surrounding the TSV of copper is also subject to significant thermal stress. The induced thermal stress changes the

electrical resistivity and mobility of silicon around the  $TSV^{49}$ . The changes in mobility may result in timing violations in the circuit. Therefore, a keep out zone (KOZ) area<sup>50–52</sup> has to be properly defined. Technically, KOZ is defined as the area around a TSV where the transistors cannot be formed to prevent the effects leading to device failure. KOZ is usually considered to be an area around the TSV where mobility changes exceed 5%<sup>52</sup>.

Among the aforementioned problems, copper pumping and KOZ are the main problems. Therefore, this thesis focuses on these problems.

# 1.2. Review of Existing Research

Two parts of researches are reviewed in this section. The first part is related to high speed TSV filling without voids to reduce the total TSV fabrication cost. The second main part is related to the researches based on the TEC mismatched problem such as copper pumping and thermal stress in copper TSV.

## 1.2.1. High Speed TSV Filling

Copper electrodeposition accounts for 41% of the total production cost of TSV and is the most expensive step in the TSV production process<sup>41</sup>. Thus, reduction of the copper electrodeposition cost is necessary. There are several ways to reduce the cost of copper electrodeposition, including using latest electrodeposition tools and reducing the time required for electrodeposition. However, the latest electrodeposition tools are expensive. Furthermore, large clean room areas need to accommodate a large amount of electrodeposition tools. Therefore, electrodeposition time must be shortened to reduce TSV production costs. Numerous studies have been investigated the factors that affect copper electrodeposition to reduce the filling time<sup>53-72</sup>.

PPR current is one of the factors that can be used and optimized for high speed TSV filling<sup>53–57</sup>. For example, J.-J. Sun et al. first successful filled the  $10 \times 70 \ \mu m$  TSV in 12 hours<sup>55</sup>.

K. Kondo et al. 's results showed that a  $10 \times 70 \,\mu\text{m}$  TSV was completely filled in 60 minutes by using optimized PPR current to remove voids at the TSV center<sup>56</sup>. In addition, S. C. Hong et al. achieved 80 minutes of filling time for  $30 \times 60 \,\mu\text{m}$  TSVs using a three-step PPR current<sup>57</sup>.

Changing the TSV shape from conventional columnar to conical shape greatly reduced TSV filling time<sup>58–60</sup>. According to a K. Kondo et al. research<sup>58</sup>, the filling time decreased from 60 minutes at  $-10 \text{ mA/cm}^2$  for 30×50 µm columnar TSVs to 20 minutes at  $-28 \text{ mA/cm}^2$ . Also, H. Hoang and K. Kondo achieved completely filling of 3×27 µm and 2×16 µm conical TSVs in only 3 minutes<sup>59</sup> and 30 seconds<sup>60</sup>, respectively.

Additives are the key for obtaining bottom-up TSV filling. Various accelerators, inhibitors and levelers have been investigated in previous studies for high speed TSV filling<sup>61–</sup><sup>72</sup>. For example, T. Hayashi et al. introduced V-shaped bottom-up filling of  $10 \times 70 \,\mu\text{m}$  TSV in 35 minutes using diallylamine additive as leveler<sup>70</sup>. T. P. Moffat et al. reported donut-shape bottom-up filling of  $8 \times 56 \,\mu\text{m}$  columnar TSVs in 17 minutes using only Tetronic 701<sup>71</sup>. M. J. Kim et al synthesized new TEG-based levelers and achieved perfect 9x40  $\mu\text{m}$  TSV filling within 750 seconds<sup>72</sup>. There are thousands of additives, each with different effects on TSV filling. Therefore, there is still room for reducing TSV filling times with new novel additives.

# 1.2.2. TEC Mismatch Challenges: Copper Pumping and KOZ

During the SiO<sub>2</sub> formation in via middle process, copper TSV is exposed to a high temperature between 400°C and 600°C. Due to the large thermal expansion coefficient (TEC) mismatch between the silicon substrate and copper, copper expands much more than silicon, causing high thermal stresses. Thermal stress has caused some serious reliability problems. Copper pumping and KOZ are the main reliability problems. Therefore, current researches on copper pumping and KOZ are reviewed here.

In this part, the research review is divided into three following fields: (1) Review of researches related to the effects of annealing condition and numerical studies. (2) Review of researches related to other TSV filling materials that are not pure electrodeposited copper. (3) Review of researches related to TSV geometry and TSV structure.

# (1) Review of studies related to the effects of annealing condition and numerical studies.

The first field is a review of studies related to the effects of annealing condition, and numerical studies of thermal stress and copper pumping. After copper TSV fabrication, copper TSV is exposed to a high temperature between 400°C and 600°C during the SiO<sub>2</sub> formation in via middle process. Exposure to high temperatures changes the properties of electrodeposited copper. Several studies have used scanning electron microscope (SEM), nanoindentation, and electron backscatter diffraction (EBSD) to investigate the effects of annealing on changes in copper properties<sup>73–77</sup>. For instance, P. Saettler et al.<sup>73</sup> investigated the microstructure of electrodeposited copper in TSVs at different annealing temperatures. It can be seen that no significant grain growth is observed up to 250°C. At temperatures above 250°C, copper grain growth is appearance, and the size of the copper grains increases with the annealing temperature. T. Jiang et al. and J. D. Messemacker et al. have studied the correlation between copper microstructure and copper pumping<sup>75,78</sup>. In addition, the effect of annealing conditions on copper hardness and elastic modulus was also studied by C. Okoro et al.<sup>76</sup>. Nanoindentation measurements showed that high temperature annealing reduces hardness and elastic modulus of electrodeposited copper.

There are many works that studied about copper pumping when annealing. Laser microscope, interferometer, atomic force microscopy (AFM) have been applied to study copper pumping. All of the above measurements showed that the copper pumping height increased with increasing annealing temperature<sup>46,77,79–81</sup>. Furthermore, I. D. Wolf et al. <sup>81</sup> reported that

multiple long time annealing and CMP can reduce the copper pumping. However, the CMP is a very expensive process.

Numerical models also are created to simulate copper pumping and thermal stress in silicon<sup>46,47,82–84</sup>. N. Nabiollahi et al. numerically simulated copper pumping during annealing by using finite element analysis<sup>83</sup>. B. Liu et al. simulation results showed that a von Mises stress peak appeared at the interface between silicon and copper TSV; and the von Mises stress gradually decreased as the distance from the TSV increased<sup>46</sup>. These numerical studies help understand the reliability problems of copper TSVs under various annealing conditions.

# (2) Review of researches related to other TSV filling materials that are not pure electrodeposited copper.

The second field is review of researches related to TSV filling materials. It is necessary to find a fundamental solution to inhibit the copper pumping and thermal stress problem. One direct solution to reduce Cu pumping in TSVs is to minimize TEC mismatch between copper and silicon substrate. TEC mismatch can be minimized by replacing Cu by a metal having a lower TEC value than copper or alloying copper with a metal having a lower TEC value<sup>85–88</sup>. For example, Kikuchi et al. succeeded in depositing TSV uniformly with W metal which has TEC value of  $4.5 \times 10^{-6/\circ}C^{85}$ . M. H. Roh et al. tried to inhibit the copper pumping by using Cu-W alloys. The results showed that the TEC of Cu-7.6 %wt W was only  $10.8 \times 10^{-6/\circ}C$ . The pumping height also decreased from 1.369 µm for Cu to 0.465 µm for Cu-7.6%wt W<sup>86</sup>. H. S. Jung et al. investigated the effect of Cu-Ni alloy on TSV pumping at various annealing temperatures. The 92% wt Cu-8% wt Ni alloy TSV showed low pumping height and low von Mises stress at temperatures below 350°C. At temperatures above 350°C, the pumping increased and the von Mises stress of the Cu-Ni via increased due to increased Cu creep

deformation<sup>87</sup>. However, the resistivity of these metal and alloys is higher than that of copper, and furthermore, etching is difficult.

Recently, silicon carbide (SiC) particles and carbon nanotubes (CNTs) have also been tested for TSV filling<sup>89–93</sup>. S.H. Kee et al.<sup>89</sup> attempted to reduce copper pumping of 30x60 µm TSVs by adding of SiC particles into the electrolyte. It was confirmed that the pumping height decreased from 1.12 µm for Cu TSV to 0.164 µm for Cu/SiC TSV. However, the aspect ratio of TSV is very low, and the resistivity of Cu/SiC composite is higher than that of copper. S. Sun et al.<sup>92</sup> filled the TSV with a novel CNT/Cu composite. CNT/Cu composite is a promising material because it has low resistivity and low TEC value. However, growing CNTs in TSV requires special techniques, and it is difficult to control the uniform distribution of CNTs.

# (3) Review of researches related to TSV geometry and TSV structure.

The third field is review of researches related to TSV geometry and TSV structure. The thermal stress of copper TSV has been studied with different structural designs, such as the impacts of the diameter, the pitch, and the geometry of TSVs<sup>94–96</sup>. According to K. H. Lu et al.<sup>94</sup> and J. Pang et al.<sup>95</sup> researches, the larger the TSV diameter, the greater the stress acting on the surrounding silicon. Therefore, downsizing TSV diameter is a useful way to reduce the thermal stress. Also, J. Pang suggested that the TSV pitch should be larger than 3.5 times TSV diameter to prevent the interaction between two adjacent TSVs<sup>95</sup>. J. Zhou et al.<sup>96</sup> studied the role of different TSV geometry designs on the thermal stress. The results suggested that the stiffness of TSV sidewall has an important effect on the thermal stress of the copper TSV.

The liner layer functions as a buffer or cushion for thermal stress, as it mechanically bonds copper to silicon. Therefore, thicker liner or liner which has lower Young's modulus can relieve thermal stresses, reduce copper pumping and KOZ. Several researches have been conducted to investigate the effect of liner thickness and polymer liner on the reduction of copper pumping and KOZ<sup>97-102</sup>. J. D. Messemaeker et al.<sup>97</sup> investigated the effect of the liner thickness and the liner elastic modulus on copper pumping and thermal stress. The results showed that the thickness of the liner O<sub>3</sub>-TEOS SiO<sub>2</sub> had an opposite effect on copper pumping and thermal stress in 5x50 µm TSV. As the thickness of the O<sub>3</sub>-TEOS SiO<sub>2</sub> liner increases from 50 to 630 nm, the residual pumping height decreases from  $(102 \pm 7)$  nm to  $(11 \pm 1)$  nm and the thermal stress increases from 220 to 610 MPa. In addition, J. D. Messemaeker et al.'s results also showed that the low-k dielectric liner effectively reduced residual copper pumping and thermal stress, compared to O<sub>3</sub>-TEOS SiO<sub>2</sub> liner. However, an improvement in deposition conformality of low-k dielectric liner was necessary. T. T, Bui et al.<sup>98,99</sup> studies revealed the potential for using Parylene-HT as the liner layer in TSV. However, no copper pumping and thermal stress were addressed in Parylene-HT liner TSV. Another polymer used for TSV liner is benzocyclobutene (BCB)<sup>100-102</sup>. Q. Chen et al.<sup>102</sup> tried to solve thermal stress problem by developing TSV using benzocyclobutene (BCB) as liner layers. The result shows that BCB layers were able to reduce the stress in the silicon surrounding, but it increased the copper pumping. Recently, polyimide used as TSV liner has become more popular due to its low Young's modulus value (3-4 GPa) along with the TEC value of 20 ppm/°C which is close to the TEC of copper<sup>103–108</sup>. Murugesan et al.<sup>105</sup> study showed that the polyimide liner not only reduced the copper pumping height to more than half of the SiO<sub>2</sub> liner layer, but also affected the uniform copper pumping height that facilitated the rest of the integration process. In addition, the authors confirmed that the polyimide liner reduces thermal stress by a factor of five compared to the thermal stress in SiO<sub>2</sub> liner TSV.

# 1.3. Abstract of Research

Through Silicon Via (TSV) enabled by copper electrodeposition is the key technology of 3DIC packaging, which allow high packaging density, high speed signal transmission, and reduce power consumption. TSV technology has a bright future, with TSV packaging revenues estimated to increase to about \$ 4.5 billion in 2023 (Source: 2.5D / 3D TSV & wafer-level stacking technology & market updates 2019 report by Yole Development). However, TSV technology still has barriers including cost and reliability problems to overcome for higher volume production. These challenges are addressed in Chapter 1 and the solutions to these challenges have been investigated in Chapter 2-5 of this research. Chapter 6 summarizes the main contributions of this thesis.

Copper electrodeposition accounts for 41% of the total production cost of TSV and is the most expensive step in the TSV production process<sup>41</sup>. Thus, reduction of the copper electrodeposition cost is necessary. There are several ways to reduce copper electrodeposition costs, such as using a clean room area, improving electrodeposition tools, and reducing electrodeposition time. However, using the clean room area and the latest electrodeposition tools is expensive. Increasing current density, which means shorten the electrodeposition time, is a promising solution to reduce electrodeposition time. However, if the current density is too high, constriction occurs at the TSV opening and voids will be formed. Over the last decade, there are many studies looking at defect-free fast TSV filling solutions, such as using pulsed reverse currents, designing different TSV structures, investigating new additives, and optimizing additives concentration<sup>53-72</sup>. However, there are thousands of additives, each with different effects on TSV filling. Therefore, there is still room for reducing TSV filling times with new novel additives. In the Chapter 2 of this thesis, I have been investigated the chemical behaviors of Sulfonated Diallyl Dimethyl Ammonium Bromide Copolymer (SDDABC) in copper electrodeposition. Furthermore, SDDABC concentration optimization and TSV filling experiments at the optimal SDDABC concentration have been also performed.

Copper is commonly used for TSV filling because copper has the low resistivity value. However, copper TSVs pose reliability problems due to thermal expansion coefficient (TEC) mismatch between copper and surrounding silicon. The main mechanical reliability problems include copper pumping, voiding, cracking, and delamination<sup>42-48</sup>. The residual stresses from the thermal annealing degrades the TSV mobilities through the piezoelectric effect, threatening TSV electrical performance. The residual stresses define a Keep Out Zone (KOZ) around the TSV where no active devices are located to prevent electronic devices failure<sup>51,52</sup>. The large TEC mismatch of about 15 x 10<sup>-6</sup>/°C results in the accumulation of thermal stresses that cause copper pumping and KOZ, which have been investigated in a number of studies. For example, the microstructure of copper in TSV when annealing has been characterized by using SEM, nanoindentation and EBSD methods<sup>73-77</sup>. In addition, simulations also were performed to understand the effect of copper pumping and KOZ<sup>46,47,82-84</sup>. From this understanding, proper annealing conditions and multiple CMPs were performed to reduce copper pumping and KOZ. However, this method is not very effective and costly. Another way to minimize TEC mismatch between copper and silicon is to replace copper by alloying and compositing copper with other materials having a lower TEC values<sup>85-93</sup>. However, the resistivity of copper alloys and copper composites is higher than pure electrodeposited copper, and special methods may be required for electrodeposition. To reduce copper pumping and KOZ, TSV structural designs such as TSV diameter, pitch, geometry, and TSV liner materials were also investigated<sup>94-108</sup>. However, improvements in the adhesion and uniformity of the polymer liners were needed.

Reduction of copper pumping and KOZ by reducing the TEC of pure electrodeposited copper is of primary interest in this research. No one to date think or attempt to reduce the TEC of pure electrodeposited copper, thus this research is very original. Reducing the TEC of electrodeposited copper is a simply method to save costs while maintaining the resistivity of the electrodeposited copper. In Chapter 3, I have found out low TEC copper electrodeposited in a solution containing 2-Mercapto-5-benzimidazolesulfonic acid sodium salt dihydrate (2M5S) additive by measuring the thermal expansion of a copper pipe with the thermal expansion meter. In addition, the contraction mechanism of low TEC copper has been proposed

based on the detailed observations of electrodeposited copper when annealing. Thereafter, low TEC copper has been applied to fill the APCVD SiO<sub>2</sub> TSV in Chapter 4, and copper pumping at different annealing temperatures is measured using the in-situ heating SEM stage. Furthermore, the resistivity of low TEC copper before and after annealing is also measured and compared with conventional electrodeposited copper. Finally, the electrochemical behaviors of 2M5S and its interaction with other additives in the electrolyte have been investigated in Chapter 5. In addition, copper pumping and KOZ have been measured for conventional copper and low TEC copper in PECVD SiO<sub>2</sub> TSV. Finally, Chapter 6 summarizes the main contributions of this thesis.

## 1.4. References

1. G. E. Moore, Cramming More Components Onto Integrated Circuits, *Proceedings of the IEEE*, vol. 86, pp. 82-85, 1998.

2. K. Kondo et al., Copper Electrodeposition for Nanofabrication of Electronics Devices, Nanostructure Science and Technology, Springer, p. 178 (2014).

3. K. N. Tu, Microelectron. Reliab., 51, 517–523 (2011).

4. J. U. Knickerbocker et al., IBM J. Res. Dev., 52, 553-569 (2008).

5.https://archive.eetasia.com/www.eetasia.com/ART\_8800714409\_499486\_NT\_874cb9d4.H TM.

6. J.H. Lau, Who Invented the Through Silicon Via (TSV) and When? 3D InCites, 2010.

7. Kada, Morihiro, "Research and Development History of Three-Dimensional Integration Technology". *Three-Dimensional Integration of Semiconductors: Processing, Materials, and Applications*, Springer, pp. 6–7 (2015).

8. J. H. Lau, *Reliability of RoHS-Compliant 2D and 3D IC Interconnects*, McGraw Hill Professional, p. 1 (2010).

- 9. J. Eloy, Market Trends for 3D Stacking, EMC 3D, 2007.

- 10. R. Abdolvand and F. Ayazi, Sensors Actuators A Phys., 144, 109-116 (2008).

- 11. C. J. D. Craigie et al., J. Vac. Sci. Technol. B Microelectron. Nanom. Struct., 20, 2229 (2002).

- 12. C. B. Labelle, V. M. Donnelly, G. R. Bogart, R. L. Opila, and A. Kornblit, *J. Vac. Sci. Technol. A Vacuum, Surfaces, Film.*, **22**, 2500–2507 (2004).

- 13. Z. Wang, F. Jiang, D. Q. Yu, and W. Q. Zhang, ECS Trans., 60, 407-412 (2014).

- 14. J. P. Gambino, S. A. Adderly, and J. U. Knickerbocker, *Microelectron. Eng.*, **135**, 73–106 (2015).

- 15. Z. Wang, Microelectron. Eng., 210, 35-64 (2019).

- 16. C. Chang, T. Abe, and M. Esashi, Microsyst. Technol., 10, 97-102 (2004).

- 17. E. J. Kim, J. Electrochem. Soc., 141, 3462 (1994).

- 18. I. A. Shareef, J. Vac. Sci. Technol. B Microelectron. Nanom. Struct., 13, 1888 (1995).

- R.Wieland, SiO2, Handb. 3D Integr. Technol. Appl. 3D Integr. circuits, p. 107–1687

120, (2008).

- 20. K. Suu, in 2016 Pan Pacific Microelectronics Symposium (Pan Pacific), IEEE, p. 1–6, (2016).

- 21. K. Moon, A Robust Through-Silicon-Via (TSV) Middle Scheme for 3D Interconnects Technology, in: Advanced Metallization Conf. (2010).

- 22. A. Redolfi et al., in 2011 IEEE 61st Electronic Components and Technology Conference (ECTC),, p. 1384–1388, IEEE (2011).

- 23. A. Klumpp, P. Ramm, and R. Wieland, in 2010 Design, Automation & Test in Europe Conference & Exhibition (DATE 2010), p. 1678–1683, IEEE (2010).

- 24. N. Khan et al., IEEE Trans. Components Packag. Technol., 33, 3-9 (2010).

- 25. Y. Civale et al., in 2012 4th Electronic System-Integration Technology Conference,, p. 1-

4, IEEE (2012).

26. Jung-Chih Hu, W.-C.G., Ting-Chang Chang, Ming-Shiann Feng, Chun-Lin Cheng, You-Shin Lin, Ying-Hao Li, Lih-Juann Chen. 2005: Germany.

27. T. P. Moffat et al., J. Electrochem. Soc., 147, 4524 (2000).

28. W.-P. Dow and H.-S. Huang, J. Electrochem. Soc., 152, C67 (2005).

- 29. Y. Jin, K. Kondo, Y. Suzuki, T. Matsumoto, and D. P. Barkey, *Electrochem. Solid-State Lett.*, **8**, C6 (2005).

- 30. D. Stoychev, Trans. IMF, 76, 73-80 (1998).

- 31. W.-P. Dow, M.-Y. Yen, W.-B. Lin, and S.-W. Ho, J. Electrochem. Soc., 152, C769 (2005).

- 32. J. J. Kelly, J. Electrochem. Soc., 145, 3477 (1998).

- 33. Z. V. Feng, X. Li, and A. A. Gewirth, J. Phys. Chem. B, 107, 9415-9423 (2003).

- 34. T. P. Moffat, D. Wheeler, S.-K. Kim, and D. Josell, J. Electrochem. Soc., 153, C127 (2006).

- 35. A. C. West, S. Mayer, and J. Reid, Electrochem. Solid-State Lett., 4, C50 (2001).

- 36. T. Hayashi et al., J. Electrochem. Soc., 162, D199-D203 (2015).

- 37. S.-K. Kim, D. Josell, and T. P. Moffat, J. Electrochem. Soc., 153, C826 (2006).

- 38. K. Kondo, T. Nakamura, and N. Okamoto, J. Appl. Electrochem., 39, 1789–1795 (2009).

39. J. R. White, J. Appl. Electrochem., 17, 977-982 (1987).

40. T. Hayashi et al., J. Electrochem. Soc., 160, D256-D259 (2013).

41. C. Setiagung, Advanced copper electrodeposition corresponding to TSV process. Paper presented at the three dimentional packaging- TSV electrodeposition tool, University of Tokyo, 31 Aug 2009 (2009).

42. J. M. Chan, X. Cheng, K. C. Lee, W. Kanert, and C. S. Tan, in 2017 IEEE 67th Electronic Components and Technology Conference (ECTC),, p. 73–79, IEEE (2017).

43. H. Kitada, T. Akamatsu, Y. Mizushima, T. Ishitsuka, and S. Sakuyama, in 2015 IEEE 65th Electronic Components and Technology Conference (ECTC),, vol. 2015-July, p. 1840–1845, IEEE (2015).

44. J. Marro, C. Okoro, Y. Obeng, and K. Richardson, *Microelectron. Reliab.*, **54**, 2586–2593 (2014).

45. S. Chen et al., Microelectron. Reliab., 91, 52-66 (2018).

- 46. B. Liu, A. Satoh, K. Tamahashi, Y. Sasajima, and J. Onuki, *Trans. Japan Inst. Electron. Packag.*, **11**, E17-014-1-E17-014–8 (2018).

- 47. F. X. Che et al., IEEE Trans. Components, Packag. Manuf. Technol., 3, 732–739 (2013).

48. S.-K. Ryu et al., Appl. Phys. Lett., 100, 041901 (2012).

- 49. C. Selvanayagam, X. Zhang, R. Rajoo, and D. Pinjala, *IEEE Trans. Components, Packag. Manuf. Technol.*, **1**, 1328–1335 (2011).

- 50. W. Guo et al., in 2013 IEEE International Electron Devices Meeting,, p. 12.8.1-12.8.4, IEEE (2013).

- 51. M. Said, M. El-Sayed, F. Mehdipour, and N. Miyakawa, in *Technical Papers of 2014 International Symposium on VLSI Design, Automation and Test.*, p. 1–4, IEEE (2014).

- 52. S.-K. Ryu et al., IEEE Trans. Device Mater. Reliab., 12, 255–262 (2012).

- 53. S. Jin, S. Seo, S. Park, and B. Yoo, *Microelectron. Eng.*, 156, 15–18 (2016).

- 54. Q. S. Zhu, A. Toda, Y. Zhang, T. Itoh, and R. Maeda, *J. Electrochem. Soc.*, **161**, D263–D268 (2014).

- 55. J.-J. Sun et al., J. Electrochem. Soc., 150, G355 (2003).

- 56. K. Kondo et al., J. Electrochem. Soc., 152, H173 (2005).

- 57. S. C. Hong, W. G. Lee, W. J. Kim, J. H. Kim, and J. P. Jung, *Microelectron. Reliab.*, **51**, 2228–2235 (2011).

- 58. K. Kondo et al., J. Electrochem. Soc., 161, D791–D793 (2014).

- 59. V. H. Hoang and K. Kondo, *Electrochim. Acta*, 212, 270–276 (2016).

- 60. V. H. Hoang and K. Kondo, J. Electrochem. Soc., 164, D795–D797 (2017).

- 61. N. T. M. Hai, J. Furrer, E. Barletta, N. Luedi, and P. Broekmann, *J. Electrochem. Soc.*, **161**, D381–D387 (2014).

- 62. N. T. M. Hai et al., J. Electrochem. Soc., 160, D3158–D3164 (2013).

- 63. T. Lu, F. Wang, and Y. He, J. Electrochem. Soc., 163, D663–D671 (2016).

- 64. C. Chang, X. Lu, Z. Lei, Z. Wang, and C. Zhao, *Electrochim. Acta*, 208, 33–38 (2016).

- 65. M. Tang et al., RSC Adv., 7, 40342–40353 (2017).

- 66. W.-P. Dow et al., *Electrochim. Acta*, **54**, 5894–5901 (2009).

- 67. W. Dow, C. Li, M. Lin, G. Su, and C.-C. Huang, J. Electrochem. Soc., 156, D314 (2009).

- 68. D. Josell and T. P. Moffat, J. Electrochem. Soc., 161, D287–D292 (2014).

- 69. O. Lühn, C. Van Hoof, W. Ruythooren, and J.-P. Celis, *Electrochim. Acta*, **54**, 2504–2508 (2009).

- 70. T. Hayashi, K. Kondo, T. Saito, M. Takeuchi, and N. Okamoto, *J. Electrochem. Soc.*, **158**, D715 (2011).

- 71. T. P. Moffat and D. Josell, J. Electrochem. Soc., 159, D208–D216 (2012).

- 72. M. J. Kim et al., J. Electrochem. Soc., 163, D185-D187 (2016).

- 73. P. Saettler, M. Boettcher, and K.-J. Wolter, in 2012 IEEE 62nd Electronic Components and Technology Conference,, p. 619–624, IEEE (2012) http://ieeexplore.ieee.org/document/6248895/.

- 74. M. Song et al., Mater. Sci. Eng. A, 755, 66-74 (2019).

- 75. T. Jiang, C. Wu, J. Im, R. Huang, and P. S. Ho, in *IEEE International Interconnect Technology Conference*, p. 377–380, IEEE (2014).

- 76. C. Okoro et al., J. Micromechanics Microengineering, 20, 045032 (2010).

- 77. S. Chen et al., Microelectron. Reliab., 63, 183-193 (2016).

- 78. J. De Messemaeker et al., in 2014 IEEE 64th Electronic Components and Technology Conference (ECTC),, p. 613–619, IEEE (2014).

- 79. M. Sung et al., J. Electrochem. Soc., 166, D514–D520 (2019).

- 80. C. Paper et al., in 2013 Electronic Components & Technology Conference,, p. 586–591 (2013).

- 81. I. De Wolf et al., *Microelectron. Reliab.*, **51**, 1856–1859 (2011).

- 82. T. Jiang et al., *Microelectron. Reliab.*, **53**, 53–62 (2013).

- 83. N. Nabiollahi et al., in 2013 14th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE),,

p. 1–4, IEEE (2013).

- 84. X. Liu et al., IEEE Trans. Components, Packag. Manuf. Technol., 6, 993-999 (2016).

- 85. H. Kikuchi et al., Jpn. J. Appl. Phys., 47, 2801–2806 (2008).

- 86. M.-H. Roh, A. Sharma, J.-H. Lee, and J.-P. Jung, *Metall. Mater. Trans. A*, **46**, 2051–2062 (2015).

- 87. H. S. Jung, Y. Jang, S. Choa, and J. P. Jung, Mater. Trans., 56, 2034–2041 (2015).

- 88. Y. T. Lin et al., ECS Electrochem. Lett., 4, D25–D27 (2015).

- 89. S.-H. Kee, W.-J. Kim, and J.-P. Jung, Microelectron. Eng., 214, 5–14 (2019).

- 90. H. Wu et al., J. Electrochem. Soc., 166, D237–D243 (2019).

- 91. R. Xie et al., Nanotechnology, 24, 125603 (2013).

- 92. S. Sun et al., Nanotechnology, 27, 335705 (2016).

- 93. T. Wang, K. Jeppson, L. Ye, and J. Liu, Small, 7, 2313–2317 (2011).

- 94. K. H. Lu et al., in 2009 59th Electronic Components and Technology Conference,, p. 630–634, IEEE (2009).

- 95. J. Pang and J. Wang, in 2012 13th International Conference on Electronic Packaging Technology & High Density Packaging, p. 725–730, IEEE (2012).

- 96. Jing Zhou et al., in 2011 IEEE 13th Electronics Packaging Technology Conference,, p. 686–690, IEEE (2011).

97. J. De Messemaeker et al., in *2015 IEEE International Reliability Physics Symposium*,, vol. 2015-May, p. 4C.5.1-4C.5.10, IEEE (2015).

98. T. T. Bui et al., IEEE Trans. Components, Packag. Manuf. Technol., 6, 510-517 (2016).

99. T. T. Bui et al., in 2016 IEEE 66th Electronic Components and Technology Conference (ECTC),, vol. 2016-Augus, p. 2182–2187, IEEE (2016).

100. S. Lee et al., in 2018 International Conference on Electronics Packaging and iMAPS All Asia Conference (ICEP-IAAC),, p. 346–349, IEEE (2018).

101. Q. Ma, K. Wu, and Z. Wang, *IEEE Trans. Components, Packag. Manuf. Technol.*, **6**, 1847–1854 (2016).

102. Q. Chen, W. Yu, C. Huang, Z. Tan, and Z. Wang, *Microelectron. Reliab.*, **53**, 725–732 (2013).

103. T. Fukushima, M. Murugesan, J. Bea, K. W. Lee, and M. Koyanagi, in *Extended Abstracts* of the 2013 International Conference on Solid State Devices and Materials,, vol. 308, p. 866–867, The Japan Society of Applied Physics (2013).

104. S. Wang, Y. Yan, Z. Cheng, Z. Chen, and Y. Ding, *Microsyst. Technol.*, **23**, 3757–3764 (2017).

105. M. Murugesan et al., in 2014 IEEE International Electron Devices Meeting,, vol. 2015-Febru, p. 14.7.1-14.7.4, IEEE (2014).

106. C. Xue et al., IEEE Trans. Device Mater. Reliab., 18, 266–272 (2018).

107. Y. Yan et al., in 2016 IEEE International 3D Systems Integration Conference (3DIC),, p. 1–5, IEEE (2016).

108. Y. Yan, M. Xiong, B. Liu, Y. Ding, and Z. Chen, *Sci. China Technol. Sci.*, **59**, 1581–1590 (2016).

## CHAPTER 2: BOTTOM-UP TSV FILLING USING SULFONATED DIALLYL DIMETHYL AMMONIUM BROMIDE COPOLYMER AS A LEVELER

#### 2.1. Introduction

Through Silicon Via (TSV) enabled by copper electrodeposition is the key technology of 3-demintional integrated circuit (3DIC) packaging, which allow high packaging density, high speed signal transmission, and reduce power consumption. However, the TSV processing cost is still expensive. Copper electrodeposition accounts for 41% of the total production cost of TSV<sup>1</sup>, so it is necessary to reduce copper electrodeposition cost. There are several ways to reduce the cost of copper electrodeposition, including using latest electrodeposition tools and reducing the time required for electrodeposition. However, the latest electrodeposition tools are expensive. Furthermore, large clean room areas need to accommodate a large amount of electrodeposition tools. Increasing current density, which means shorten the electrodeposition time, is a promising solution to reduce electrodeposition time. However, if the current density is too high, constriction occurs at the TSV opening and voids will be formed. Therefore, high speed TSV filling without void defects is required.

In this Chapter, a new leveler, sulfonated diallyl dimethyl ammonium bromide copolymer (SDDMABC), has been introduced for copper electrodeposition. SDDMABC leveler exhibits a strong inhibition effect and its super bottom-up TSV filling will be reported.

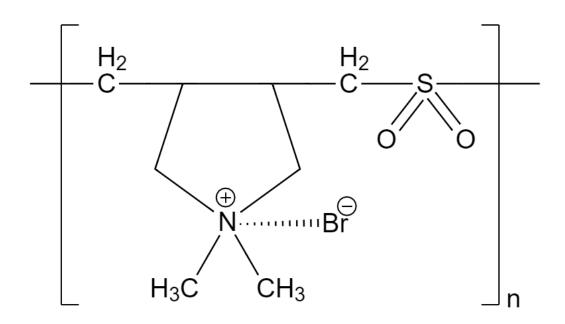

#### 2.2. Experimental

The composition of a basic bath was 200 g/L  $CuSO_4 \cdot 5H_2O$  and 25 g/L  $H_2SO_4$ , 50 ppm of Cl<sup>-</sup>, 2 ppm of SPS, and 25 ppm of PEG. SDDABC leveler which has only one positive charge head group and bromide as a counter ion is purchased from Nittobo Medical Co., Ltd. The chemical structure of SDDABC is shown in Figure 21. The solutions used for all

electrochemical measurements and TSV filling experiments were prepared by adding different concentrations of SDDABC to the basic bath.

Figure 21. Structure of sulfonated diallyl dimethyl ammonium bromide copolymer (SDDABC).

Cyclic voltammetry stripping (CVS) measurements were performed at room temperature using a electrochemical measurement system (Hokuto Denko, HZ7000) equipped with a rotator (Hokuto Denko, HZAP1203n) in three electrodes glass cell containing 60 mL of electrolyte. A platinum rotating disk electrode (RDE) with a diameter of 5 mm were used as working electrode. The counter and reference electrodes were platinum wire and saturated calomel electrode (SCE electrode), respectively. In cyclic voltammetry stripping (CVS) measurement, potential was swept from 0.6V to -0.4V and then returned back to 0.6V. The potential sweep rate for CVS experiments was 10 mV/s.

Electrodeposition samples for filling experiments were silicon chip fragments with many TSVs. TSV with a diameter of 20  $\mu$ m and a depth of 45  $\mu$ m was used without knowing the detail structure of the TSV. A phosphorus containing copper bar was used as an anode. TSV filling experiments were carried out in a beaker containing 150 mL of electrolyte solution. The electrolyte was purged with oxygen for 30 minutes prior to electrodeposition. Silicon chip fragments were placed on a rotating cathode which rotated at 1000rpm during electrodeposition. A pulse reverse current was applied to copper electrodeposition. The pulse conditions were t<sub>off</sub>: t<sub>on</sub>: t<sub>reverse</sub> = 100: 200: 10 ms and i<sub>on</sub>: i<sub>reverse</sub> = 1:3. The silicon chip fragments were polished using emery papers. Then, the TSV cross section was observed by SEM (JEOL, JSM-5500S).

#### 2.3. Results and Discussion

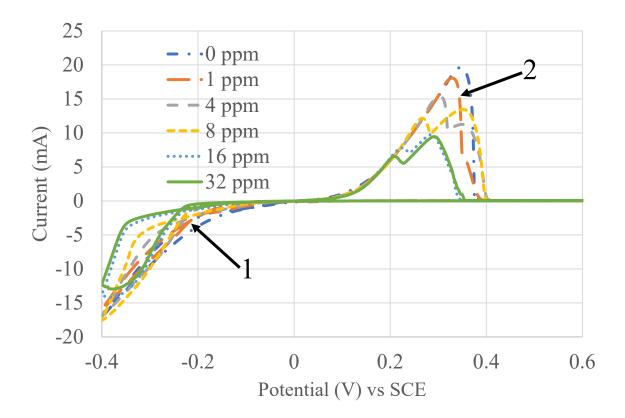

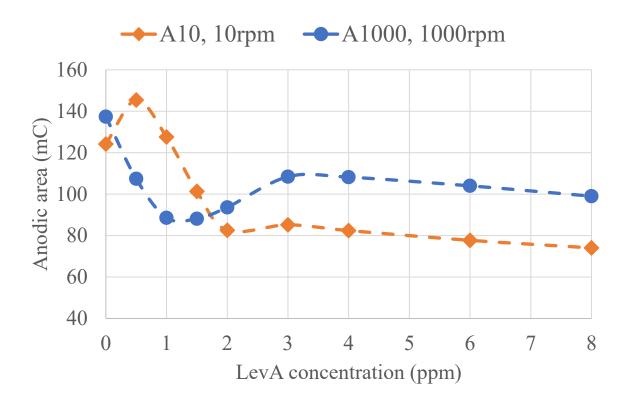

Figure 22 shows cyclic voltammograms recorded at 1000 rpm from solutions containing 50 ppm Cl<sup>-</sup>, 2 ppm SPS, 25 ppm PEG and different concentrations of SDDABC leveler. In the presence of 1 ppm of SDDABC, the reduction potential of cupric ion underwent a negative shift (arrow 1), along with the decrease in the anodic stripping peak (arrow 2). This means that addition of 1 ppm of SDDABC inhibits the copper electrodeposition. As expected with the increase of SDDABC concentration to 32 ppm, this inhibition effect of SDDABC is more clearly because SDDABC shifted the reduction potential to more negative values and dramatically decreased the anodic stripping area. Moreover, increasing the concentration of SDDABC leveler from 16 ppm to 32 ppm did not significantly change the cathodic potential and anodic stripping area, indicating that saturation inhibition is almost reached at 16 ppm of SDDABC. This inhibition is due to the adsorption of SDDABC leveler molecule on the cathode surfaces<sup>2,3</sup>.

Figure 22. Cyclic voltammograms in the presence of different concentrations of SDDABC.

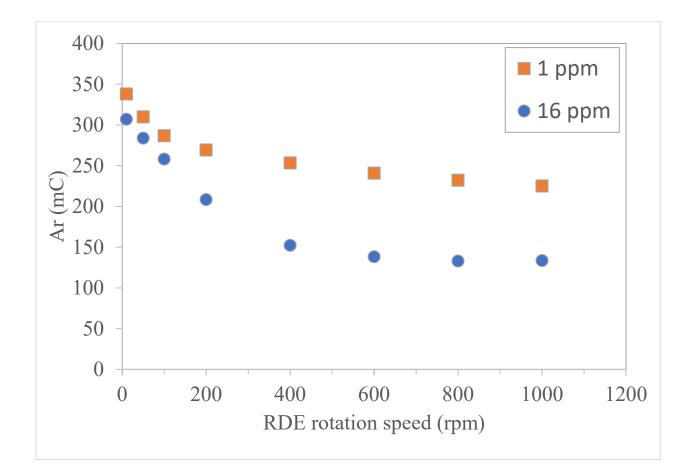

Because TSV is deep and narrow, the convection outside TSV is high flow velocity, while that inside the TSV is slow flow velocity during filling process. Therefore, I assume that 1000 rpm of rotating disk electrode (RDE) represents the convection condition at the via outside, 10 rpm of RDE represents the convection at the via bottom. To understand the inhibition effect of SDDABC leveler for copper electrodeposition during TSV filling process, the changes of RDE rotation speed in the presence of SDDABC were studied. Figure 23 shows the influence of rotation speed on anodic stripping area (Ar) obtained from CVS measurement with 1 ppm (**•** symbol) and 16 ppm (**•** symbol) of SDDABC. For both 1 ppm and 16 ppm of SDDABC, the Ar values decrease faster at low rotation speeds than that at high rotation speeds. This rotation dependent behavior indicates that the copper deposition is inhibited strong at the via outside and sidewall near via opening, while the acceleration effect at the via bottom is

strong. Moreover, the Ar values at high rotation speeds (above 400 rpm) of 16 ppm SDDABC were about 150 mC, while the values of 1 ppm of SDDABC were 250 mC. That means 16 ppm of SDDABC inhibits the copper electrodeposition at via sidewall and outside much stronger than 1 ppm of SDDABC. In other words, 16 ppm of SDDABC must have better TSV filling performance than 1ppm of SDDABC.

Figure 23. Influence of RDE rotation speed on anodic stripping charge of copper electrodeposition at 1 and 16 ppm of SDDABC.

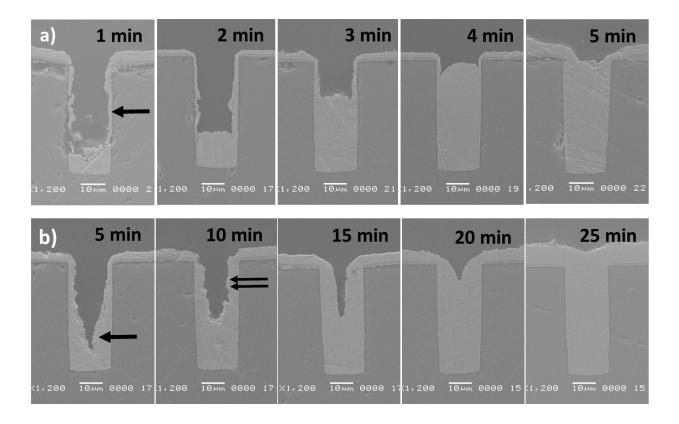

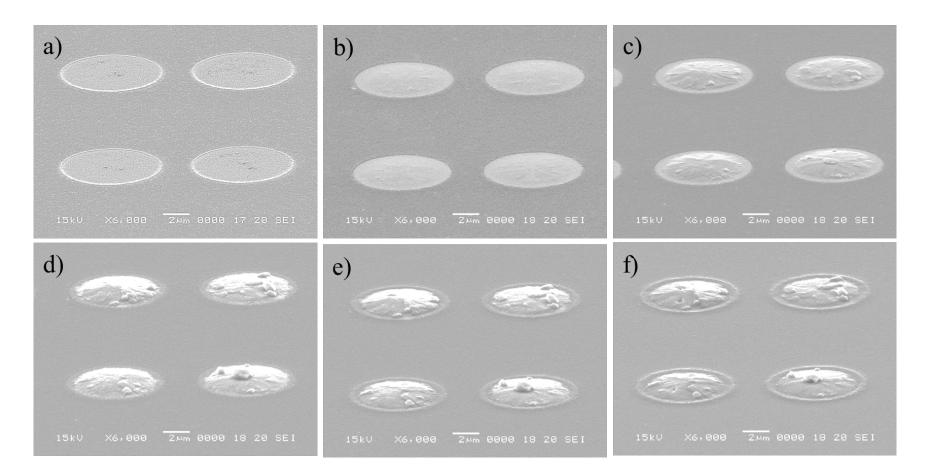

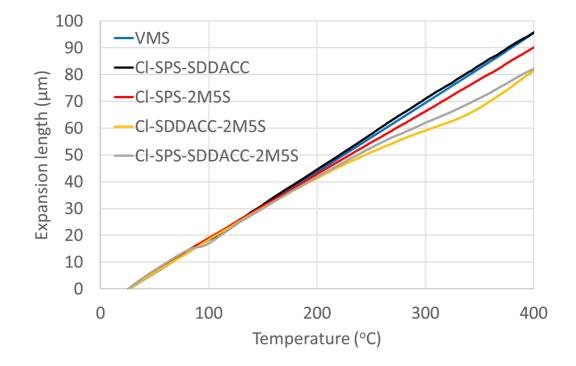

Figure 24 shows the cross sections of TSV filled with 1 ppm and 16 ppm of SDDABC at different electrodeposition times. The current density is 25 mA/cm<sup>2</sup>. Figure 24a shows the

filling profiles over times with 16 ppm of SDDABC and the electrodeposition time is 1 min, 2 min, 3 min, 4 min, and 5 min, respectively. In this case, deposition rate at the via sidewall is very small (arrow in Figure 24a at 1 min) and super bottom-up TSV filling is observed. This is only possible when inhibition layer formed by 16 ppm of leveler cover the via sidewall and strongly inhibit the copper electrodeposition on the via sidewal<sup>4-6</sup>. In addition, it takes only 5 min to completely fill the TSV in the presence of 16 ppm SDDABC. Figure 24b is the cross sections of TSV filled with 1 ppm of SDDABC and the electrodeposition time is 5 min, 10 min, 15 min, 20 min, and 25 min, respectively. The V- shape bottom-up filling with thick deposited copper at the via bottom and sidewall near the via bottom (arrow in Figure 24b at 5 min) and relatively thick deposited copper at the sidewall near the via outside (double arrows in Figure 24b at 10 min) forms with 1 ppm of SDDABC. This V- shape has been reported in several studies<sup>2,7</sup>. The V-shape filling attributes to the gradually decrease inhibition effect along the via depth direction and strong acceleration effect of accelerator at the via bottom. With increasing time, the filling ratio reached 100% with 25 min.

Figure 24. Cross sections of TSV filled with a) 16 ppm and b) 1 ppm of SDDABC at different filling times.

#### 2.4. Conclusions

In this chapter, sulfonated diallyl dimethyl ammonium bromide copolymer (SDDABC) was used as a leveler. The leveler behavior was characterized by CVS method with different concentrations at different RDE rotation speeds. SDDABC forms a strong inhibition layer on copper surface when 16 ppm concentration is added. Super bottom-up TSV filling with nearly no deposited on TSV sidewall was achieved with 16 ppm of SDDABC. This super bottom-up filling is 5 times faster than that with V-shape.

#### 2.5. References

C. Setiagung, Advanced copper electrodeposition corresponding to TSV process. Paper presented at the three dimentional packaging - TSV electrodeposition tool, University of Tokyo, 31 Aug 2009 (2009).

2. O. Lühn, C. Van Hoof, W. Ruythooren, and J.-P. Celis, *Electrochim. Acta*, **54**, 2504–2508 (2009).

3. B. Chen, J. Xu, L. Wang, L. Song, and S. Wu, ACS Appl. Mater. Interfaces, 9, 7793–7803 (2017).

4. T. P. Moffat and D. Josell, J. Electrochem. Soc., 159, D208–D216 (2012).

5. V. Hoang and K. Kondo, J. Electrochem. Soc., 164, D795–D797 (2017).

6. M. J. Kim et al., J. Electrochem. Soc., 163, D185–D187 (2016).

7. T. Hayashi, K. Kondo, T. Saito, M. Takeuchi, and N. Okamoto, J. Electrochem. Soc., 158, D715–D718 (2011).

## CHAPTER 3: LOW THERMAL EXPANSION ELECTRODEPOSITED COPPER AND ITS CONTRACTION MECHANISM BY ANNEALING

#### 3.1. Introduction

Copper is widely used as a filling material for TSV because of its lowest resistivity, next to silver<sup>1</sup>. Despite the advantages of using copper as the filling material, copper TSV has its drawback due to thermal expansion coefficient (TEC) mismatch between copper and surrounding silicon. Copper has a high thermal expansion coefficient (TEC) of  $17x10^{-6/\circ}$ C, while the TEC of silicon is only  $2x10^{-6/\circ}$ C. During the SiO<sub>2</sub> formation in via middle process, copper TSV is exposed to a high temperature between 400°C and 600°C. Due to the large thermal expansion coefficient (TEC) mismatch between the silicon substrate and copper, copper expands much more than silicon, causing high thermal stresses in all directions during the manufacturing process. These thermal stresses inside copper TSV cause copper pumping, voiding, cracking, and delamination. Copper pumping can destroy the wiring above the copper TSV and lead to the failure of electronic device. Moreover, the induced thermal stress, which caused by the TEC mismatch between copper and silicon, changes the electrical resistivity and mobility of silicon around the TSV. Technically, KOZ is defined as the area around a TSV where the transistors cannot be located to prevent device failure. Copper pumping and KOZ are serious reliability problems that need to be resolved.

No one to date think or attempt to reduce the TEC of pure electrodeposited copper, thus this research is very original. In this chapter, I have found out low TEC copper electrodeposited in a solution containing 2-Mercapto-5-benzimidazolesulfonic acid sodium salt dihydrate (2M5S or Lev A) additive by measuring the thermal expansion of a copper pipe with the

thermal expansion meter. In addition, the contraction mechanism of low TEC copper has been proposed based on the detailed observations of electrodeposited copper when annealing.

#### 3.2 Experimental

The base electrolytes for the copper electrodeposition were  $CuSO_4.5H_2O$  and  $H_2SO_4$ . The additives used in this study consisted of a leveler, accelerator, inhibitor,  $Cl^-$ , and 2-Mercapto-5-benzimidazolesulfonic acid sodium salt dihydrate (Lev A)<sup>2</sup>.

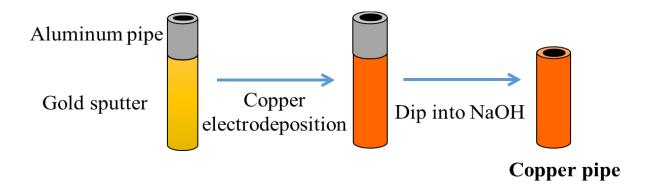

Copper pipes were made for measuring the TEC of the electrodeposits. Figure 25 shows the procedure used to form a copper pipe. An aluminum pipe was used as the cathode. First, gold was sputtered on the aluminum pipe. Copper was electrodeposited on the gold then the pipe was immersed in a sodium hydroxide solution to dissolve the aluminum and form the copper pipe.

Figure 25. Procedure to form the copper pipe.

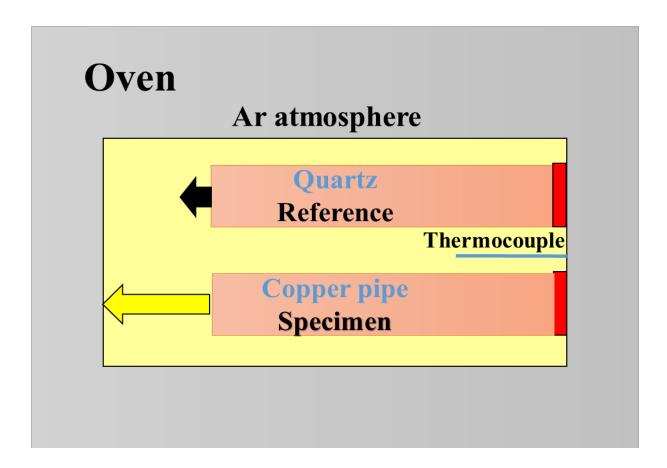

Figure 26 is a schematic illustration of the thermal expansion meter (TD5020SA, NETZSCH). The copper pipe was heated in an argon atmosphere with quartz as the reference. The copper pipe expansion lengths were measured.

Figure 26. Schematic illustration of the thermal expansion meter.

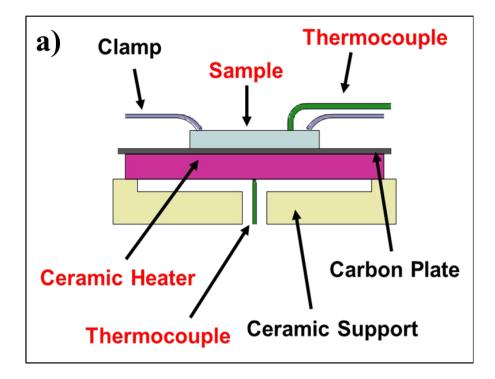

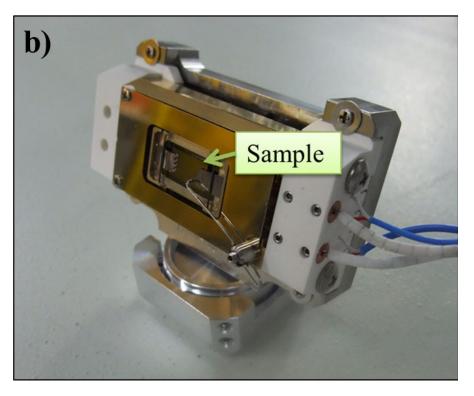

Figure 27 is the in-situ SEM heating stage (HSEA-500, TSL solutions). (a) is a cross sectional illustration and (b) is the digital camera image. The sample was heated by a ceramic heater.

Field Emission Auger Electron Spectroscopy (FE-AES) was carried out using a Model 680(Ulvac-phi) operated at 10kV acceleration voltage and 10nA specimen current. X-ray diffraction (XRD) profiles were measured by a Ringaku SmartLab X-Ray Diffractometer using Cu K $\alpha$  radiation ( $\lambda = 1.5406$  Å) operated at 45 kV, 200 mA and a scanning speed of 5°/min. The carbon contents were measured by combustion method using a model CS LS600 (LECO Japan).

Figure 27. In-situ SEM heating stage (TSL solutions, HSEA-5000)a) Cross sectional illustrationb) Digital image.

#### 3.3. Results and Discussion

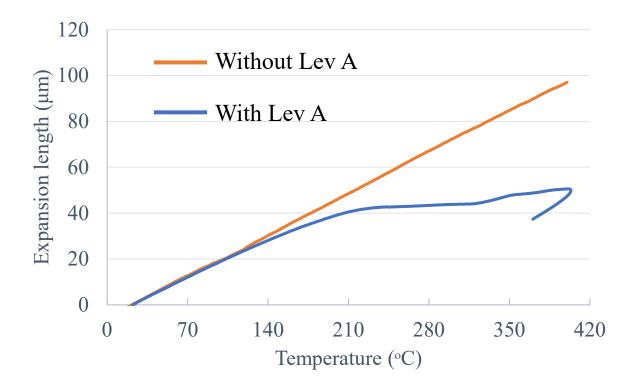

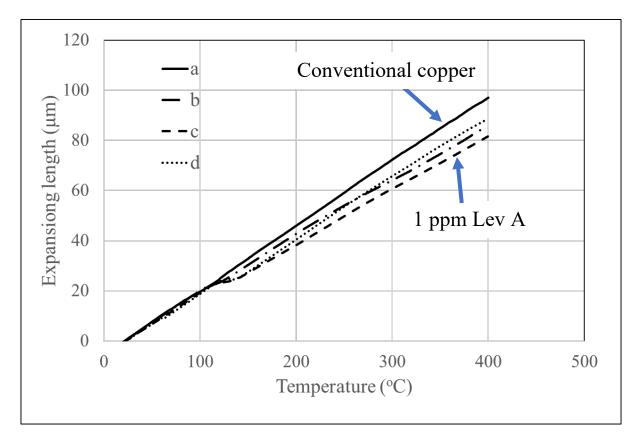

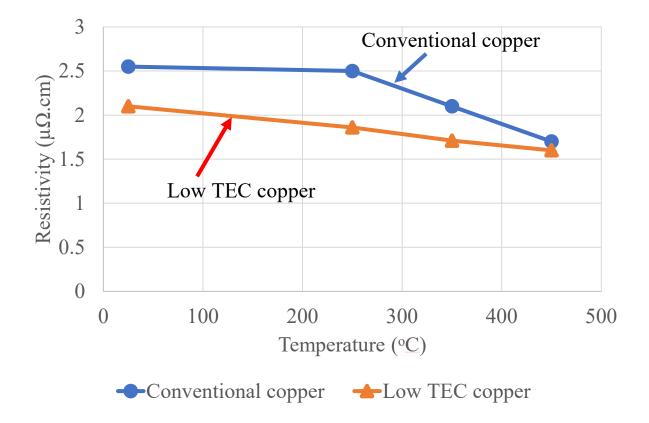

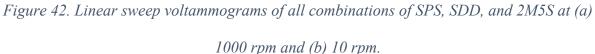

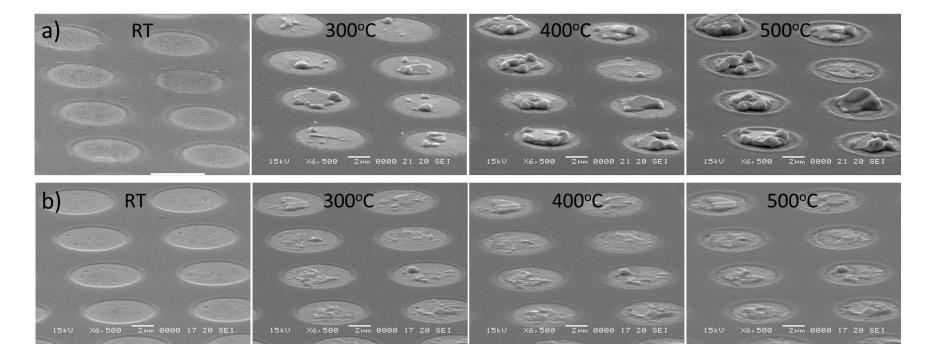

Figure 28 shows the thermal expansions of the conventional copper and

electrodeposited copper with the low TEC additive. For the conventional copper, the expansion length linearly increased with the temperature (red line). The thermal expansion coefficient, or the slope, is constant with the temperature. With the low TEC additive, the electrodeposited copper starts to contract at 120°C (blue curve). The difference between red line and blue curve increases in the range temperature from 203°C to 310°C. This difference becomes much greater at about 47µm at 400°C.

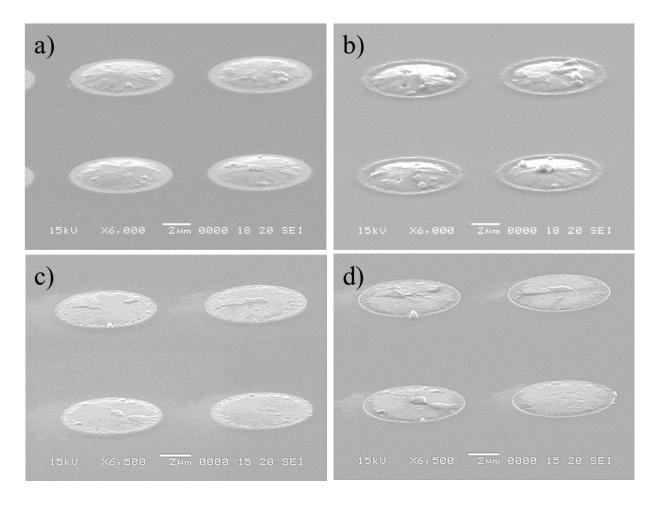

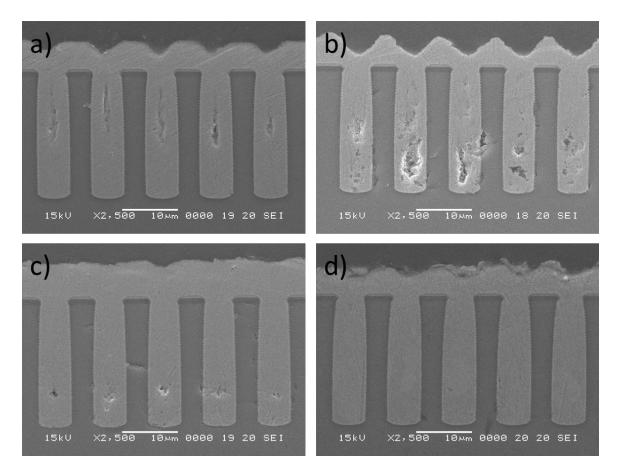

Figure 28. Thermal expansions of electrodeposited copper with and without low TEC additive (Lev A).

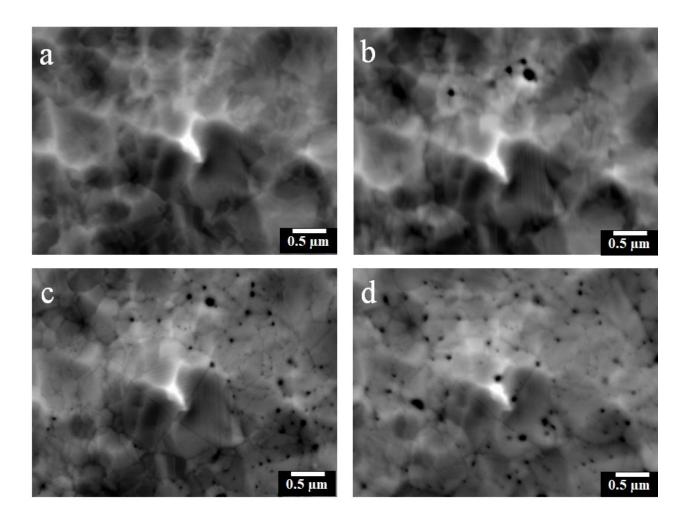

Figure 29 shows the in-situ SEM micrographs of the electrodeposited copper at the different annealing temperatures. Micrograph a is 203°C, b is 310°C, c is 350°C and d is 450°C. Micrographs are obtained at the high temperatures using an in-situ SEM heating stage (Figure 27). In Figure 29a, about 1 µm of electrodeposited copper grains are observed. No dark spot is observed at 203°C. Several 100 nm dark spots start emerging when the annealing temperature

was 310°C (Figure 29b). These dark spots form at the grain boundaries and at the triple grain points. The number of dark spots increased with the increase in the temperature as shown in Figure 29c at 350°C and Figure 29d at 450°C.

Figure 29. SEM micrographs of the electrodeposits with annealing a)203°C, b) 310°C, c)350°C, d)450°C.

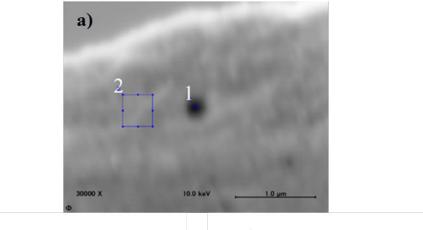

Figure 30. FE-AES analysis.

Figure 30 is the FE-AES analysis of several 100 nm dark spots and other portions of the electrodeposit. Area 1 is a 100 nm dark spot and area 2 is the other portion of the electrodeposit. The two below figures are quantitative FE-AES results of area 1 at the dark spot (Figure 30b) and area 2 at the other electrodeposited portion (Figure 30c). In Figure 30b, the intensity of the copper peak at 910eV is very low (as indicated by the red arrow). However, the intensity for the carbon at 280eV is very high. Hence, the 100 nm dark spot is a carbon precipitate. For area 2, both the copper intensity at 910eV and carbon intensity at 280eV are high. Moreover, the other Cu peaks at 778eV and 850eV are clearly visible. It is known that FE-AES detects a metal's outermost surface. On the metal's outermost surface, atmospheric carbon is adsorbed very easily. This is the reason of for the high carbon intensity in area 2.

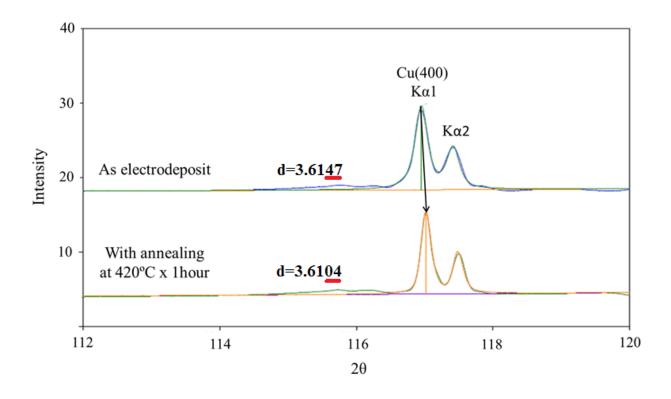

*Figure 31. X-ray diffractions of electrodeposited copper with and without annealing.*

Figure 31 shows the X-ray diffraction results of the electrodeposited copper with the low TEC additive as a deposit and after annealing at 420°C for 1 hour. Cu (4 0 0)  $_{K\alpha 1}$  and Cu (4 0 0)  $_{K\alpha 2}$  are selected at the high 2 $\theta$  in order to indicate the significant difference in the 2 $\theta$ . The position of the (4 0 0)  $_{K\alpha 1}$  peak is shifted to a higher 2 $\theta$  value from 116.950° for the electrodeposited copper to 117.180° after annealing at 420°C for 1 hour. This shift in the 2 $\theta$  value corresponds to a change in the lattice constants from d= 3.61<u>47</u>Å for the electrodeposited copper to d= 3.61<u>04</u>Å after annealing at 420°C for 1 hour. The decrease from 47 to 04 in third and fourth decimal places indicates that the copper lattices contract due to the annealing at 420°C for 1 hour.

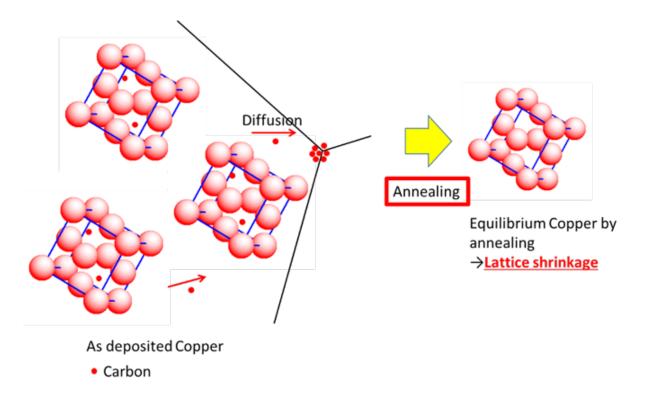

Figure 32. Mechanism of copper lattice shrinkage by annealing.

Figure 32 is the mechanism for the lattice contraction by annealing. As shown in Figure 32, the electrodeposited copper has carbon inclusion within the copper lattice. This carbon inclusion lattice is the non-equilibrium phase and the lattice constant is greater than the equilibrium

lattice constant. During annealing, carbon diffuses out of the lattice and the non-equilibrium lattice transforms into the equilibrium lattice with no carbon inclusion. The carbon diffuses to the triple grain points and form about several 100nm dark spot precipitates (Figure 29b, c, d). The non-equilibrium to equilibrium lattice transformation occurs during annealing and lattice constant contracts. This is the mechanism for the low TEC copper electrodeposition.

The as-deposited copper with the low TEC additive has 0.018wt% carbon compared to 0.004wt% without the additive. About five times more carbon is contained in the electrodeposit with the low TEC additive when compared to the electrodeposit without the low TEC additive. Furthermore, the TEC measurement and x-ray diffraction are consistent. The ratio of the expansion length between room temperature and after annealing at 400oC and the copper pipe original length is 47/15000, since the copper pipe's original length is 15000 µm. The ratio of the lattice constant difference at room temperature and after annealing at 420°C and as deposit lattice constant is 0.0043/3.6147. The order of magnitude of these two ratios are in good agreement. It is well-known that X-ray diffraction is non-destructive, without enforcing the force to the sample.

#### 3.4. Conclusions

The effect of 2-Mercapto-5-benzimidazolesulfonic acid sodium salt dihydrate (Lev A) on reduction of thermal expansion of electrodeposited copper were studied by scanning electron microscopy (SEM), FE Auger, and X-ray diffraction. The results obtained are summarized as follows.

(1) With the low TEC additive, the electrodeposited copper starts to contract at  $120^{\circ}$ C. The difference in expansion length between conventional copper and copper electrodeposited with the low TEC additive becomes greater with annealing. This difference is about  $47\mu$ m at  $400^{\circ}$ C.

52

(2) Dark spots exist in the SEM micrograph at 310°C and their number increases with the increasing annealing temperature.

(3) Based on the FE-AES analysis, several 100nm dark spots are carbon precipitates.

(4) Based on the X-ray diffraction, the lattice constant contracts by annealing at 420°C for 1 hour.

(5) The as-deposited copper has carbon inclusions in the lattice. The carbon diffuses out at high temperature, hence contracting the lattice constant. This non-equilibrium to equilibrium transformation by annealing causes copper contraction during the annealing.

#### 3.5. References

1. T. S. Choi and D. W. Hess, ECS J. Solid State Sci. Technol., 4, N3084–N3093 (2014).

2. Kazuo Kondo, PCT/JP2016/084499.

# CHAPTER 4: THERMAL STRES REDUCTION OF COPPER THROUGH SILICON VIA (TSV) WITH ANNEALING.

#### 4.1. Introduction

Three-dimensional (3D) packaging is a novel technique for obtaining improved packaging density, reduced signal delay, and reduced power consumption. 3D packaging is manufactured by vertically stacking the silicon wafers. Transistors are formed on only one side, not both sides of a silicon wafer. Therefore, through silicon via (TSV) is necessary to connect the upper transistors to lower transistor in the shortest distance. Copper is widely used for TSV filling due to its low resistivity.

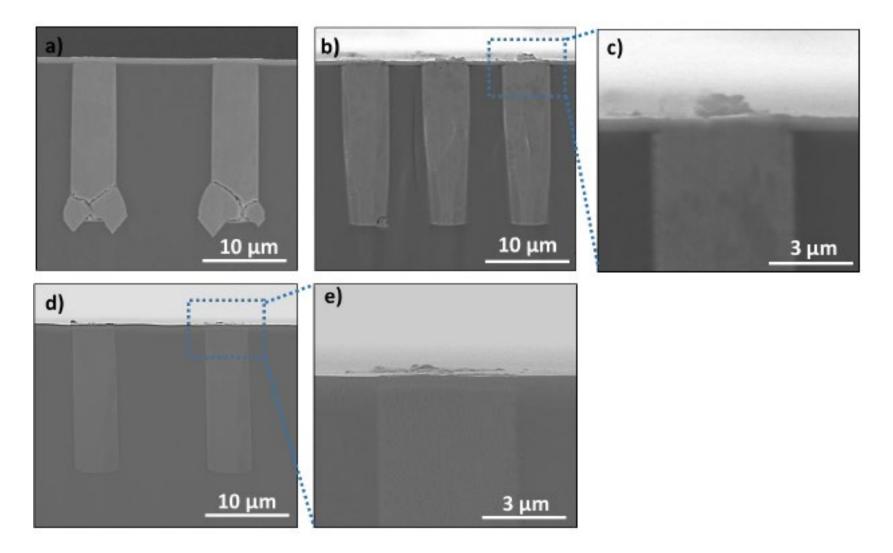

However, in the TSV manufacturing process, copper TSV encounters the thermal stress problem. Via middle process is currently a most adopted process for 3D packaging. During wiring step in via middle process, dielectric layer SiO<sub>2</sub> is form by thermal chemical vapor deposition (CVD) under a high range of temperature between 400°C and 600°C. Hence, copper TSV also is exposed this high temperature. Unfortunately, the thermal expansion coefficient (TEC) of copper is  $17x10^{-6/°}$ C, nearly nine times greater than that of silicon ( $2x10^{-6/°}$ C). That large mismatch in TEC between copper and silicon generates the thermal stress inside and surround the copper TSV. A part of thermal stress in the upper region of copper TSV is released by the copper pumping. However, the copper pumping destroys the overlying wires above the copper TSV and causes the devices failure.

In chapter 3, I found out the low TEC copper and its contraction mechanism with annealing. Thereafter, I tried to use this low TEC copper to fill the TSV with atmospheric pressure chemical vapor deposition (APCVD) SiO<sub>2</sub> liner in this chapter. Copper pumping in low TEC copper TSV at different annealing temperatures is measured by using the in-situ heating SEM stage. Furthermore, the resistivity of low TEC copper before and after annealing is also measured and compared with conventional electrodeposited copper.

#### 4.2. Experimental

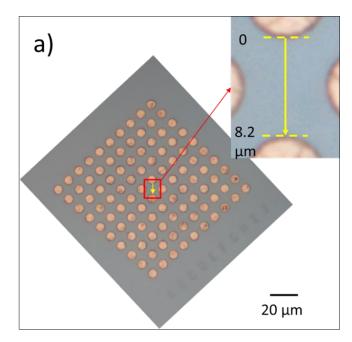

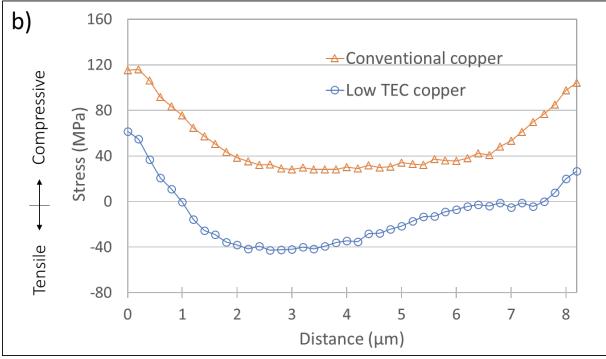

The basic electrolyte contained CuSO<sub>4</sub>.5H<sub>2</sub>O, H<sub>2</sub>SO<sub>4</sub>, and Cl<sup>-</sup> ion from HCl form. An accelerator bis-3-sulfopropyl disulfide (SPS), a inhibitor polyethylene glycol (PEG, average molecular weight of 10000) and two levelers namely: sulfonated diallyl dimethyl ammonium chloride copolymer (SDDACC) and 2-Mercapto-5-benzimidazolesulfonic acid sodium salt dihydrate (Lev A) were added into the basic electrolyte. In this study, two combinations of additives were used. The first combination consisted of basic electrolyte, SPS, PEG, SDDAC, and it was called a conventional bath is widely used in the industry. The other bath was a low TEC bath consisting of basic electrolyte, SPS, SDDAC and Lev A.