# Energy-Efficient On-Chip Cache Architectures and Deep Neural Network Accelerators Considering the Cost of Data Movement

Hongjie Xu

March 3, 2021

# Acknowledgments

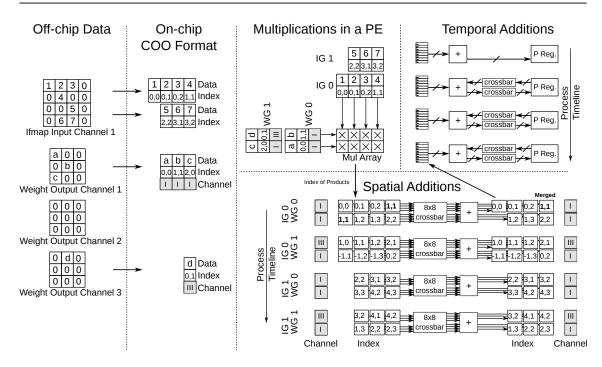

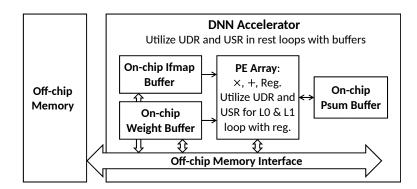

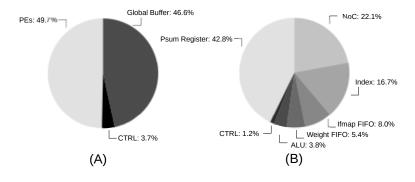

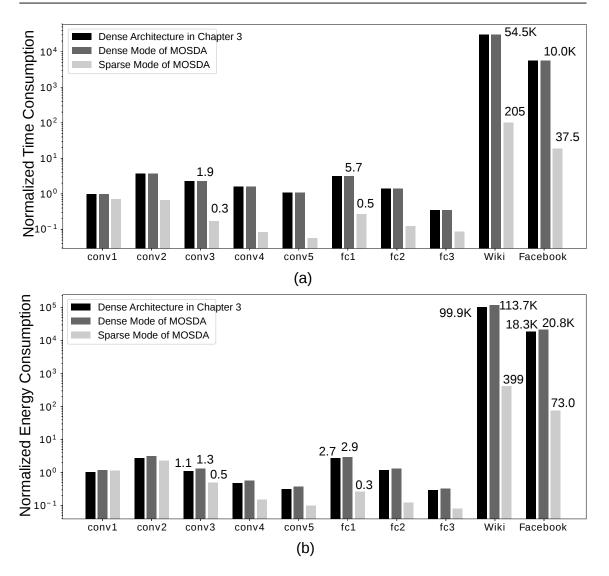

I would first like to thank my thesis advisor Prof. Hidetoshi Onodera. The door to Prof. Onodera office was always open whenever I ran into a trouble spot or had a question about my research or writing. Prof. Onodera consistently allowed this thesis to be my own work, but steered me in the right direction whenever he thought I needed it.

I would like to thank Profs. Takashi Sato, Eiji Oki, and Sadao Kurohashi for valuable comments that greatly improved the manuscript.

I wish to express my sincere appreciation to my supervisor, Prof. Tohru Ishihara, who convincingly guided and encouraged me to be professional and do the right thing even when the road got tough during my master course. Without his persistent help, the goal of this PhD thesis would not have been realized.

I would also like to thank Shiomi sensei who was involved in the validation survey for this research project for introducing me to the topic as well for the support on the way. Without their passionate participation and input, the validation survey could not have been successfully conducted.

The physical and technical contribution of "WISE Program, Innovation of Advanced Photonic and Electronic Devices" is truly appreciated. Through the program, I have learned a lot about research methodology and various interdisciplinary knowledge. Without their financial support and funding, I would not have been able to graduate in time.

Finally, I must express my very profound gratitude to my parents and to my labmates for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them. Thank you.

> Hongjie Xu in Kyoto March 3, 2021

ii

# Abstract

Energy-Efficient Cache Architectures and Deep Neural Network Accelerators Considering the Cost of Data Movement

by

Hongjie Xu Doctor of Philosophy in Informatics Kyoto University Professor Hidetoshi Onodera, Chair

In data processing, the cost of data movement often dominates the hardware performance. Based on factors that affect the prediction capability of the cost of data movement, this thesis investigates representative types of processing tasks as general-purpose processing and special-purpose processing such as Deep Neural Network. This thesis discusses data properties that influence data movement in each processing task. Taking advantage of the proposed properties, this thesis designs four hardware designs to reduce the cost of data movement for various processing tasks.

For general-purpose processing which has a completely unpredictable data access pattern, this thesis proposes an energy-efficient hybrid cache memory system to exploit the non-linear relationship between the cache miss rate and the cache capacity. As the cache capacity increases from 0, the cache miss rate decreases rapidly as the capacity rises because there is no enough space to store all the data that is expected to be accessed in the near future by CPU. When the cache capacity exceeds a certain capacity, the cache miss rate decreases at a slower rate. According to the non-linear relationship, a hybrid 2-level on-chip cache architecture is first introduced as a replacement of a normal SRAM cache architecture to save the energy consumption. This thesis then discusses a method for finding the best mix of Standard-Cell Memory and SRAM, which minimizes the energy consumption of the hybrid cache under a cache area constraint. The simulation result

shows a hybrid 2-level cache architecture by our method reduces the energy consumption by 68% in our case study of an instruction memory subsystem without increasing the die area.

In Deep Neural Network, which has a large data scale but a regular access pattern, this thesis introduces hardware properties to describe the precise cost of data movement in each memory hierarchy. Based on hardware properties, this thesis proposes a DNN accelerator for large-scale processing with a regular access pattern in DNN and a set of evaluation metrics that are able to evaluate the number of memory accesses and the required memory capacity according to a specialized processing dataflow. Proposed metrics are able to analytically predict the energy, the throughput, and the area of a hardware design without a detailed implementation. Once the processing dataflow and constraints of hardware resources are determined, the proposed evaluation metrics quickly quantify expected hardware benefits, thereby reducing design time.

In a sparse Deep Neural Network, an irregular data access pattern caused by sparsity brings great challenges to efficient processing accelerators. Focusing on the indexmatching property in Deep Neural Network, this thesis aims to decompose sparse Deep Neural Network into easy-to-handle processing tasks to maintain the utilization of processing elements. According to the proposed sparse processing dataflow, this thesis proposes an efficient hardware accelerator called MOSDA to deal with the irregular data access pattern in sparse DNN. MOSDA can be effectively applied for operations of convolutional layers, fully-connected layers, and matrix multiplications. Compared to state-of-the-art neural network accelerators, MOSDA achieves 1.1× better throughput and 2.1× better energy efficiency than Eyeriss v2 in sparse Alexnet in our case study.

Focusing on the relationship between the memory capacity and the number of required memory accesses in Binary Neural Network which has a small data scale and a regular access pattern, this thesis utilizes a hybrid memory system to reduce energy consumption. According to the proposed processing dataflow, this thesis proposes an efficient hardware accelerator for small-scale processing with a regular access pattern in BNN processing. The proposed BNN accelerator can be effectively applied for operations of convolutional layers, and fully-connected layers. Compared to state-of-the-art binary convolutional accelerators, the proposed architecture achieves 1.4× better energy efficiency than ChewBaccaNN in Alexnet in our case study.

# Contents

| Ac | Acknowledgments |                                                      |                                                                |     |  |  |

|----|-----------------|------------------------------------------------------|----------------------------------------------------------------|-----|--|--|

| Ał | ostrac          | t                                                    |                                                                | iii |  |  |

| 1  | Intr            | oductio                                              | n                                                              | 1   |  |  |

|    | 1.1             | Backg                                                | round                                                          | 1   |  |  |

|    |                 | 1.1.1                                                | Energy-efficient Hardware Design                               | 1   |  |  |

|    |                 | 1.1.2                                                | The Cost of Data Movement                                      | 1   |  |  |

|    |                 | 1.1.3                                                | Memory Hierarchy Design                                        | 2   |  |  |

|    |                 | 1.1.4                                                | Processing Task Classification for Data Movement Evaluation    | 3   |  |  |

|    | 1.2             | Motiva                                               | ation                                                          | 4   |  |  |

|    |                 | 1.2.1                                                | Multi-Level Cache Architectures for General-Purpose Processing | 4   |  |  |

|    |                 | 1.2.2                                                | Hardware Designs for Special Purpose Processing                | 5   |  |  |

|    | 1.3             | Thesis                                               | Contribution                                                   | 7   |  |  |

|    | 1.4             | Thesis                                               | Organization                                                   | 8   |  |  |

| 2  | Hyb             | rid Cac                                              | the Memory for General-Purpose Processing                      | 9   |  |  |

|    | 2.1             | Introdu                                              | uction                                                         | 9   |  |  |

|    | 2.2             | On-chip Memory System for Ultra Low Energy Computing |                                                                |     |  |  |

|    |                 | 2.2.1                                                | Related Work                                                   | 11  |  |  |

|    |                 | 2.2.2                                                | Standard-Cell Memory                                           | 12  |  |  |

|    |                 | 2.2.3                                                | Relationship between Miss Rate and Cache Capacity              | 13  |  |  |

|    |                 | 2.2.4                                                | Motivational Example                                           | 13  |  |  |

|    | 2.3             | Energy                                               | y-Efficient Hybrid Cache System                                | 14  |  |  |

|    |                 | 2.3.1                                                | 2-Level Hybrid Cache System                                    | 14  |  |  |

|    |                 | 2.3.2                                                | Problem Definition                                             | 16  |  |  |

|    | 2.4             | Verific                                              | ation of Hybrid Cache for 65nm RISC-V Processors               | 17  |  |  |

|    |                 | 2.4.1                                                | Evaluation Setup                                               | 18  |  |  |

|   |                                                                        | 2.4.2                                     | Experimental Results                                       | 20 |  |  |  |  |  |

|---|------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------|----|--|--|--|--|--|

|   |                                                                        | 2.4.3                                     | Applicable Range Analysis                                  | 24 |  |  |  |  |  |

|   | 2.5                                                                    | Summ                                      | ary                                                        | 27 |  |  |  |  |  |

| 3 | DNN Accelerator Designs for Large-Scale Processing with Regular Access |                                           |                                                            |    |  |  |  |  |  |

|   | Patt                                                                   | ern                                       |                                                            | 29 |  |  |  |  |  |

|   | 3.1                                                                    | Introd                                    | uction                                                     | 29 |  |  |  |  |  |

|   | 3.2                                                                    | Backg                                     | round                                                      | 31 |  |  |  |  |  |

|   |                                                                        | 3.2.1                                     | DNN Processing                                             | 31 |  |  |  |  |  |

|   |                                                                        | 3.2.2                                     | Data Reuse in DNN                                          | 33 |  |  |  |  |  |

|   |                                                                        | 3.2.3                                     | Subtasks in DNN Processing                                 | 34 |  |  |  |  |  |

|   |                                                                        | 3.2.4                                     | Motivational Example                                       | 36 |  |  |  |  |  |

|   |                                                                        | 3.2.5                                     | Design Space Exploration for DNN Accelerators              | 38 |  |  |  |  |  |

|   | 3.3                                                                    | DNN I                                     | Dataflow to Reduce the Cost of Data Movement               | 39 |  |  |  |  |  |

|   |                                                                        | 3.3.1                                     | Properties for the Cost of Data Movement in DNN Processing | 39 |  |  |  |  |  |

|   |                                                                        | 3.3.2                                     | Related Work                                               | 41 |  |  |  |  |  |

|   |                                                                        | 3.3.3                                     | Proposed Dataflow                                          | 43 |  |  |  |  |  |

|   | 3.4                                                                    | Experi                                    | imental Results for the Proposed Dataflow                  | 48 |  |  |  |  |  |

|   | 3.5                                                                    | Analy                                     | tical Hardware Evaluation Model                            | 54 |  |  |  |  |  |

|   | 3.6                                                                    | Datafle                                   | ow Comparison                                              | 58 |  |  |  |  |  |

|   |                                                                        | 3.6.1                                     | Dataflow for Convolutions                                  | 58 |  |  |  |  |  |

|   |                                                                        | 3.6.2                                     | Dataflow for Matrix Multiplications                        | 60 |  |  |  |  |  |

|   | 3.7                                                                    | Hardw                                     | vare Design Evaluation                                     | 62 |  |  |  |  |  |

|   | 3.8                                                                    | Summ                                      | ary                                                        | 66 |  |  |  |  |  |

| 4 | Spa                                                                    | rse DNI                                   | N Accelerator for Irregular Data Access Pattern            | 71 |  |  |  |  |  |

|   | 4.1                                                                    | Introd                                    | uction                                                     | 71 |  |  |  |  |  |

|   | 4.2                                                                    | Backg                                     | round                                                      | 72 |  |  |  |  |  |

|   |                                                                        | 4.2.1                                     | Sparse DNN Processing                                      | 72 |  |  |  |  |  |

|   |                                                                        | 4.2.2                                     | Motivational Example                                       | 73 |  |  |  |  |  |

|   |                                                                        | 4.2.3                                     | Processing Dependency in DNN                               | 74 |  |  |  |  |  |

|   |                                                                        | 4.2.4                                     | Related Work                                               | 76 |  |  |  |  |  |

|   | 4.3                                                                    | Sparse                                    | DNN Processing Dataflow                                    | 77 |  |  |  |  |  |

|   | 4.4                                                                    | MOSDA Architecture Based on Matching Type |                                                            |    |  |  |  |  |  |

|   | 4.5                                                                    | Experimental Results                      |                                                            |    |  |  |  |  |  |

|   | 4.6                                                                    | Summ                                      | ary                                                        | 91 |  |  |  |  |  |

| 5   | BNN    | Accelerator for Small-Scale Processing with Regular Access Pattern | 93  |

|-----|--------|--------------------------------------------------------------------|-----|

|     | 5.1    | Introduction                                                       | 93  |

|     | 5.2    | Background                                                         | 95  |

|     |        | 5.2.1 BNN Processing                                               | 95  |

|     |        | 5.2.2 Motivational Example                                         | 95  |

|     |        | 5.2.3 Related Work                                                 | 97  |

|     | 5.3    | Proposed Architecture                                              | 98  |

|     |        | 5.3.1 Processing Dataflows                                         | 98  |

|     |        | 5.3.2 Hardware Architecture                                        | 99  |

|     | 5.4    | Experimental Results                                               | 101 |

|     | 5.5    | Summary                                                            | 106 |

| 6   | Cone   | clusion                                                            | 107 |

|     | 6.1    | Summary of This Thesis                                             | 107 |

|     | 6.2    | Future Work                                                        | 108 |

| Bil | bliogr | aphy                                                               | 109 |

| Pu  | blicat | ion List                                                           | 121 |

# Chapter 1

# Introduction

## 1.1 Background

### **1.1.1 Energy-efficient Hardware Design**

### **1.1.2** The Cost of Data Movement

In Big Data Era, with ever-increasing demands for Internet-of-Things (IoTs) endpoint devices, energy-efficient System-on-Chips (SoCs) are highly required [1]. Those endpoint devices, or sometimes called edge devices, are interconnected with each other, enabling autonomous processing and communication of gathered data from the target. Endpoint devices employ not only multiple sensors, but also a small processor, which is mainly used for processing near-sensor data gathered by sensors. Since most endpoint devices are battery-powered, edge devices with an energy-efficient processor are highly required.

Inside a processor, the energy of data movement between memories is expected to be two orders of magnitude higher than the energy of double-precision floating-point operations [2]. As a result, the cost of data movement often dominates the energy consumption of an entire digital hardware processing system [2, 3]. The cost of data movement describes the energy consumption of data transmission between memories. The cost of data movement in a hardware architecture is determined by two factors: the number of memory accesses and the access energy to memories. In memory designs, the access cost is directly related to the memory capacity. We can evaluate the cost of data movement required to execute a processing task, once the target processing task and the corresponding hardware structure are determined. Considering a specified processing task such as a Deep Neural Network (DNN) processing, Ref. [4] proposes a property called *data reuse* to expose the precise number of memory accesses, which is to describe the

number of accesses to the same data during the processing. Based on data reuse, previous works [5–9] build evaluation models to estimate the cost of data movement. However, data reuse is difficult to describe another important factor for data movement, which is the required memory capacity. As a result, data reuse is difficult to help design accelerators to reduce the cost of data movement.

### **1.1.3** Memory Hierarchy Design

In order to estimate the cost of data movement, this thesis investigates the memory architecture at first. In a modern processing architecture, the memory hierarchy separates a memory system into a hierarchy. The memory hierarchy uses a memory storage layer based on different access speed to memory data [10]. For the memory hierarchy in high-performance computers, the highly requested data is stored in a high-speed memory, allowing a central processing unit (CPU) core for faster access. The traditional memory hierarchy design is to accelerate operations by exploiting the locality of reference [11] to reduce the cost of data movement. An on-chip memory hierarchy acts as the buffer between CPU and main memory, which is used to hold parts of data which are expected to be accessed by CPU in a near future. As a result, many researchers have designed a memory architecture for CPU acceleration based on the locality of reference to reduce the number of accesses to time-consuming memories.

The dynamic energy consumption of a memory is also directly proportional to the number of memory accesses. If we focus on improving the energy efficiency of a single access at a memory level with a high number of accesses, we can also expect to reduce overall energy consumption at a low cost.

The energy of data movement can be deduced from the memory capacity and the number of memory accesses in a memory hierarchy. However, the target processing task sometimes makes it difficult to accurately evaluate the number of memory accesses and the memory capacity in a memory hierarchy. First, an irregular data access pattern makes it difficult to make an accurate assessment of the required memory accesses. Second, the data scale of a processing target affects the difficulty of the reduction for data movement on-chip. If the data scale is small enough that all data can be stored on-chip, we can reduce the movement for all data during processing. If the data size is too large, there will be an inability for on-chip memories to keep all data. Therefore we may be forced to make trade-offs and can only partially reduce the cost of on-chip data movement. This leads to different hardware processing strategies for small-scale processing and large-scale processing.

### **1.1.4** Processing Task Classification for Data Movement Evaluation

If we know precisely the memory capacity and the required number of memory accesses at each memory level for the target processing, we can estimate the cost of data movement required accurately and design the energy-efficient hardware. However, the difficulty and feasibility of predicting the cost of data movement vary in different processing tasks.

The data access pattern determines the feasibility of the evaluation of the cost of data movement in a target processing task. If the data access pattern is regular and fixed, we accurately evaluate the cost of data movement. If the data access pattern within the task is unpredictable, we can hardly make an accurate evaluation for the required number of memory accesses.

A hardware architecture is considered to handle an unpredictable data access pattern of processing tasks if it is designed to be a general-purpose processing hardware architecture. In this case, we are able to obtain performance gains to exploit the locality of reference which is a statistical property to describe that the processing unit tends to access the same memory location repetitively in a short time.

If the hardware architecture is designed to execute a particular type of processing task such as DNN processing, energy-efficient hardware designs could be designed to exploit a processing property inherent to a regular data access pattern. This thesis proposes DNN accelerators to exploit data properties in DNN processing. Since the access pattern is fixed and regular, we can build an evaluation model to accurately calculate the cost of data movement under different hardware structures. However, due to the large data size of DNN processing, it is often difficult to design a hardware architecture that stores all data to reduce the cost of data movement on-chip. Therefore, we need to design an evaluation model to guide us to make the trade-off between the reduction of the on-chip memory capacity and the reduction of off-chip memory accesses.

Different from dense DNN, sparse DNN has an irregular data access pattern due to its data sparsity. Previous DNN acceleration structures often need to skip zero-related operations in order to efficiently exploit the data sparsity to save energy. The unpredictable zero position leads to an irregular data access pattern. Fortunately, the irregular access pattern of sparse DNN is not completely unpredictable as in the case of general-purpose processing. We can decompose a sparse processing task into small tasks with a regular access pattern by a well-designed processing dataflow. As a result, we can design an energy-efficient hardware accelerator based on its data movement evaluation model.

Binary Neural Network (BNN) is with a regular access pattern and also a small data scale. For BNN processing, it is possible to design an energy-efficient memory hierarchy

to reduce the cost of data movement, since all data can be stored on-chip [12]. As a result, we have an opportunity to design an energy-efficient memory hierarchy design that matches processing properties.

## **1.2** Motivation

This section introduces motivation in this thesis. Section 1.2.1 introduces motivation in Chapter 2, which targets data movement reduction in general-purpose processing. The first part of section 1.2.2 introduces motivation in Chapter 3, which targets data movement reduction in accelerators in DNN processing. The second part of section 1.2.2 introduces motivation in Chapter 4, which targets data movement reduction in sparse DNN processing. The third part of Section 1.2.2 introduces the motivation of Chapter 5, which focuses on data movement reduction of accelerators in BNN processing.

## 1.2.1 Multi-Level Cache Architectures for General-Purpose Processing

In general-purpose processing, since there is no way to know what a task to be processed will be, the data access pattern for processing will be unpredictable. Considering an irregular data access pattern, employing caches in hardware designs is one of the most effective approaches to improve both energy efficiency and performance [13–15]. Therefore, a cache architecture is implemented into most commercial processors. The on-chip cache architecture is a major component in edge processors that dominates the entire energy consumption and performance. Ref. [3] shows that a memory hierarchy including caches consumes half of the total energy consumption of embedded processors. While these nominal on-chip caches significantly improve processing performance, they also occupy a large portion of chip area [16, 17]. Therefore, achieving cache architectures with high energy and area efficiency is a must.

A key insight is that the relationship between the cache miss rate and the capacity is non-linear, which means that when a cache capacity increases, the miss rate usually drops sharply first and then converges. The implication is that the energy consumption in an overall memory hierarchy can be reduced by replacing a high-density memory with a low-density yet more energy-efficient memory under a given area constraint. Replacing the entire memory with an energy-efficient low-density memory will result in a significant loss of the cache capacity, which is due to an unacceptable miss rate of the on-chip cache. Therefore, we consider inserting a small Level 0 (L0) cache between the CPU and the Level

1 (L1) cache. Since a small cache has a short critical path, related works utilize the L0 cache to achieve high-speed processing [18–21]. Different from previous works, this thesis attempts to reduce the overall energy consumption of memory access by implementing the energy-efficient memory in a small but frequently accessed L0 cache.

### **1.2.2 Hardware Designs for Special Purpose Processing**

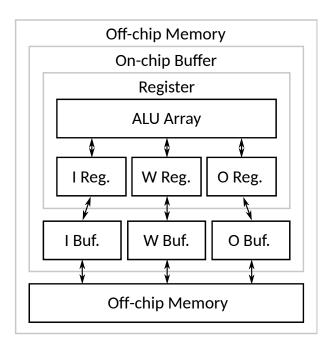

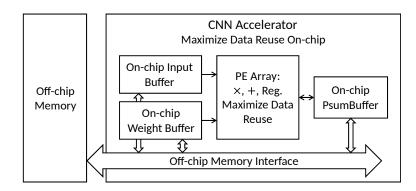

In general-purpose processing, it is often difficult to specify the access patterns for each data. This unpredictability makes it difficult to design an energy-efficient hardware which reduces the cost of data movement. The data access pattern in a special-purpose processing task is often explicit. As a representative example of special-purpose processing, the processing hardware of DNN typically uses massively parallel processing to increase the throughput of DNN accelerators. Massively parallel data movement poses two challenges for hardware designs. First, large-scale data movement in DNN processing would pose a significant energy challenge. In order to adapt to a battery-powered terminal processing environment, we should utilize data properties to minimize the cost of data movement. Second, large-scale parallel processing will also bring challenges to the scheduling of parallel data transmission. It poses a challenge for control logics of cache designs to decide where each data will be distributed in parallel at which time. As a result, many DNN accelerators abandon the use of cache designs in favor of scratchpad memories for data movement in DNN processing [22–35].

Considering the factors that affect the prediction capability for the data movement, DNN processing tasks can be further classified into several tasks. First, the data access pattern is considered to determine the feasibility of an evaluation of the cost of data movement in the target DNN. If the data access pattern is regular and fixed such as dense DNN processing, the cost of data movement can be accurately evaluated. If the data access pattern within a parallel processing task is irregular such as sparse DNN, it is hard to estimate the required number of memory accesses accurately. Second, the data scale of a processing task is considered to affect the evaluation of the number of memory accesses and the memory capacity. If the data scale of a target program such as BNN processing is small enough that all data can be stored on-chip, the memory structure required for data processing is usually simple and clear. If the data size of a target program is larger than an on-chip memory storage capability, the data movement is more complex and difficult to be precisely evaluated. As a result, this thesis divides DNN processing tasks into dense DNN, sparse DNN, and BNN for a more accurate estimation of data movement.

DNN Accelerator for Large-Scale Processing with Regular Access Pattern

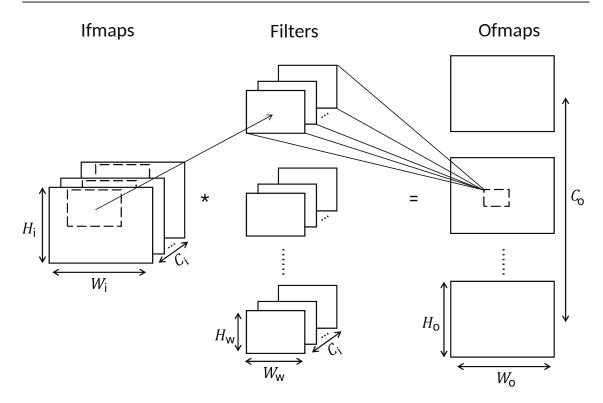

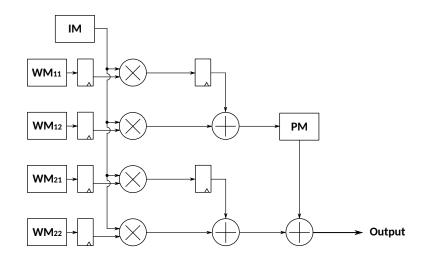

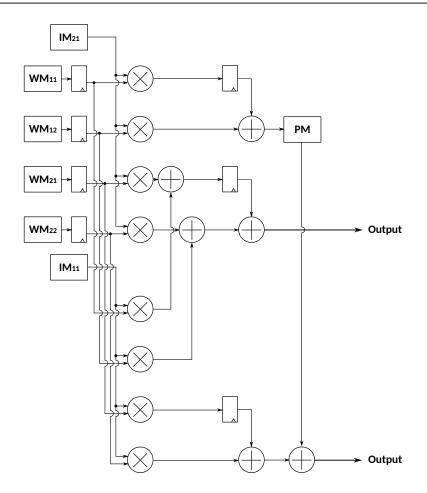

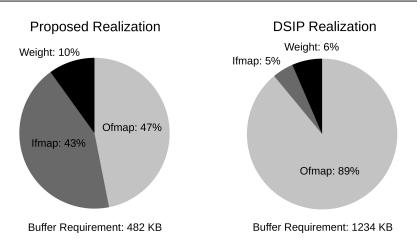

A DNN hardware accelerator relies on parallel processing of multiplications and additions for throughput enhancement. In order to evaluate the precise data movement during DNN processing, Ref. [27] introduces a detailed concept of data reuse of input feature maps (ifmaps), weights, and output feature maps (ofmaps). The number of data reuse is defined as "the number of multiply-and-accumulations (MACs) that use the same piece of data". More specifically, the data reuse of an ifmap pixel is defined by the number of occurrences of the same ifmap pixel in DNN processing. The data reuse of a weight is defined similarly. The number of data reuse of an ofmap pixel is defined as the number of product terms in one ofmap pixel in DNN processing [4]. However, since data reuse describes the number of memory accesses but not the access cost to each memory hierarchy, it is difficult for data reuse to directly compare the cost of data movement in different hardware architectures. This thesis proposes properties that can be used to describe the number of memory accesses and the memory capacity in DNN processing that can accurately describe the memory hierarchy.

#### **Sparse DNN Accelerator for Irregular Data Access Pattern**

The sparsity of weights and ifmaps can be utilized by gating or skipping operations, thereby improving energy efficiency. In order to further enhance throughput by sparsity, a complex control logic is usually inevitable according to the irregularity of weights and ifmaps in sparse DNN. For achieving high Processing Element (PE) utilization, we will propose a method that aims to directly infer the number of operations from the number of loaded non-zero ifmap pixels and the number of loaded non-zero weights so that we can easily arrange weights and ifmap pixels required for massively parallel processing. We should fetch just the right amount of input data, thereby maximizing PE utilization with a simple control logic. This thesis focuses on data dependency between ifmaps and weights to evaluate its impact on the number of required operations for sparse DNN.

#### **BNN Accelerator for Small-Scale Processing with Regular Access Pattern**

By reducing a 32-bit floating-point arithmetic to a binary arithmetic, BNNs achieve significant energy reduction and performance improvements over traditional Convolution Neural Networks (CNNs). Unlike general-purpose processing, data access patterns in BNNs are regular. The data scale in BNN is also usually small enough that all data can be stored on-chip. Therefore, this thesis proposes a hardware design of an energy-efficient on-chip memory system for data in BNNs.

This thesis adopts the Near-Threshold (NT) memory structure [18], which is more energy-efficient than SRAM, as one level of an on-chip memory hierarchy to reduce the overall energy consumption. Considering the area overhead of an NT memory, we integrate a larger SRAM-based buffer, which is more area-efficient, to store all data for BNN processing.

### **1.3 Thesis Contribution**

This thesis aims to propose energy-efficient cache architectures and DNN accelerators by reducing the cost of data movement in various processing tasks. This thesis selects two representative processing tasks, which consist of general-purpose processing and DNN processing. This thesis discusses the processing properties that may affect the cost of data movement in each situation. Considering the cost of the data movement, this thesis designs four energy-efficient hardware designs to explore the effectiveness of data processing properties to guide the direction of future hardware designs.

In general-purpose processing, an energy-efficient hybrid cache architecture design is proposed to exploit the nonlinear relationship between the cache miss rate and the capacity. The simulation result shows that the Standard-Cell Memory (SCM) based design has an energy advantage over an SRAM-based design. Using SCM as the L0 cache, a 2-stage hybrid cache architecture exhibits better energy consumption than a conventional SRAM-based cache architecture in simulations.

In DNN processing, the data movement between memory and processing elements consumes most of time, energy, and area. At the same time, the number of operations in DNN processing is usually much larger than the scale of hardware resources. The key idea is that a whole processing task can be divided into easy-to-handle small tasks to meet the hardware sizes. Next, we focus on the small tasks for a fine-grained evaluation of the cost of data movement. In this thesis, two hardware properties are investigated to describe the required number of memory accesses and the memory capacity in each memory hierarchy. Based on the two properties, this thesis proposes a DNN accelerator for large-scale processing with a regular access pattern in DNN and a new set of hardware metrics to analytically estimate energy, throughput, and area from processing dataflows. Based on the analytical evaluation of various processing dataflows and various processing environments, the proposed evaluation metrics can effectively evaluate processing dataflows without a hardware implementation. Designers are able to use the proposed evaluation metrics to significantly reduce hardware design effort.

This thesis also addresses a PE utilization problem in sparse DNN processing and sparse DNN properties. The key idea is to directly infer the number of operations from the number of loaded non-zero ifmap pixels and the number of loaded non-zero weights. This thesis proposes an efficient hardware accelerator called MOSDA for an irregular data access pattern in sparse DNN. MOSDA does not require complex control logic in sparse DNN processing and speeds up the processing by skipping zero data. According to the case study, MOSDA outperforms state-of-the-art CNN accelerators in sparse Alexnet.

This thesis further proposes a hybrid memory system with an energy-efficient memory architecture for small-scale processing with a regular access pattern in BNN processing. Based on dedicated dataflows for matrix multiplication and convolution, the proposed hardware achieves energy-efficient processing in DNN processing without crossbar logic for accumulating partial sums. The proposed architecture outperforms state-of-the-art DNN accelerators in the case study of this thesis.

## 1.4 Thesis Organization

The rest of this thesis is organized as follows. Chapter 2 presents an energy-efficient cache architecture design based on properties that affect the hardware performance for general-purpose processing. Chapter 3 discusses properties that determine the cost of data movement in DNN processing. Based on the proposed properties, this thesis presents a dense DNN accelerator and an analytical evaluation model. Chapter 4 discusses the property that helps enhance the utilization of processing elements in sparse DNN processing. This thesis further presents a sparse DNN accelerator handling irregularity. Chapter 5 discusses the memory hierarchy which is efficient for BNN processing. Based on the proposed memory hierarchy, this thesis presents an energy-efficient BNN accelerator. Chapter 6 concludes this thesis.

# Chapter 2

# Hybrid Cache Memory for General-Purpose Processing

### 2.1 Introduction

In general-purpose processing, the data access pattern in a processing task is random. However, there is still a statistical feature to describe the cost of data movement. The principle of locality [11] is a property to describe that a processing unit tends to access one same memory location repetitively in a short time. The cache design is one of the most successful techniques to exploit the principle of locality. The hardware cache is a small memory close to the processor that is used to store recently referenced data or instructions to reduce the number of accesses to the external memory. CPU accesses the cache directly. External memory is accessed only when the CPU accesses the cache and data or instructions do not exist in the cache. The failed attempt to find data in the cache is called a cache miss.

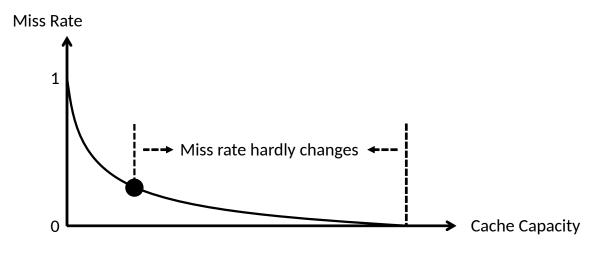

Fig. 2.1 introduces the relationship between the cache capacity and the miss rate. When the cache capacity is increased from 0, the cache miss rate decreases rapidly since there is still no enough space to store all data which is expected to be accessed in the near future. When the cache capacity comes above a certain capacity, then the cache miss rate decreases slower [13]. As a result, the relationship between the cache capacity and the miss rate is non-linear [36, 37].

In a cache design, Level-0 (L0) caches have been proposed to improve performance [18–21]. A tiny L0 cache architecture is placed between the Level-1 (L1) cache and the CPU core. Since a small cache have a better access energy and an operating speed than a large cache, the performance of the entire system can be improved. Since the CPU core firstly accesses the L0 cache, the number of accesses for the energy-consuming L1

Figure 2.1: The relationship between the cache capacity and the miss rate.

cache can be effectively reduced with an acceptable area overhead [20].

The access cost of the L0 cache has a decisive impact on the performance of an entire memory system. Therefore, we should not only reduce the L0 cache capacity, but also reduce the access energy of the L0 cache by adopting more energy-efficient memory macros to replace conventional SRAM-based cache. Recently, the concept of Near-Threshold Computing (NTC) has been emerged [18]. It downscales the supply voltage from a nominal to a near-threshold voltage of MOSFETs. The dynamic energy consumption can be quadratically reduced by a scaling technique. A traditional 6 Transistor (6T) SRAM has a limitation to reduce energy since 6T-SRAM is hard to work at a nearthreshold voltage. In order to maintain the robustness in the Near-Threshold Voltage (NTV) environment, memory macros usually use more complex peripheral circuits, or larger-sized transistors, or auxiliary power supplies for read and write operations [37–42]. Standard-Cell Memory (SCM) is a representative which has low processing speed and low area density, but inherent energy efficiency. Using SCM-based L0 cache can further reduce the overall power consumption of the cache architecture. The large area overhead is one major obstacle that prevents us from applying SCM to on-chip L0 memory. The result is that the SCM-based design has a lower cache capacity due to lower area density, and better energy performance with the same area constraint.

This chapter proposes a hybrid cache architecture which employs an energy-efficient SCM-L0 cache and an area-efficient SRAM-L1 cache. Based on the trade-off between cache capacity and energy efficiency, this chapter proposes a hybrid cache system with a filter cache architecture which employs an energy-efficient low-voltage memory and a conventional 6T-SRAM into the L0 cache and the L1 cache, respectively. Since the CPU core frequently accesses the energy-efficient L0 cache, the energy consumption can be

effectively reduced. Since the L1 cache memory consists of 6T-SRAM with high areadensity, it reduces the number of accesses for an energy-consuming off-chip memory. Compared with existing approaches on hybrid cache designs, the contribution of this chapter is summarized as follows:

- This chapter proposes a hybrid cache hierarchy where energy-efficient Near-Threshold memory and area-efficient 6T-SRAM are utilized as the L0 cache and the L1 cache, respectively.

- This chapter contributes a framework for selecting an appropriate cache architecture under given design constraints such as time and area constraints.

- For the first time, this chapter proposes an SCM-based L0 filter cache. This chapter shows that the SCM-based L0 cache achieves 68% less energy consumption compared with the SRAM-based L0 cache at near-threshold supply voltage in the simulation case of this chapter. Although NT-SCM has a better energy efficiency than NT-SRAM, NT-SCM is several times larger than NT-SRAM. However, due to the non-linear relationship between the miss rate and the cache capacity, the total energy consumption can be efficiently reduced by utilizing NT-SCM as the L0 cache. Applicable environments for the proposed hybrid cache are also analyzed.

The rest of this chapter is organized as follows. Section 2.2 presents a simple motivational example for the proposed hybrid memory structure. Section 2.3 presents a detailed architecture of the proposed hybrid cache hierarchy. Section 2.4 analyzes applicable environments for the proposed hybrid cache. Section 2.5 concludes this chapter.

# 2.2 On-chip Memory System for Ultra Low Energy Computing

### 2.2.1 Related Work

Several researchers focus on the low-power design of the L0 cache [18–21]. Ref. [21] uses a "victim" cache to reduce conflict misses and to further reduce the energy consumption. Its strategy is to insert a fully-associative cache between direct-mapped L1 cache and lower-level cache. In Ref. [20], a 128-byte cache is utilized as a filter cache in order to reduce the energy consumption at the cost of degrading the performance. Based on [21] and [20], Ref. [18] proposes a reconfigurable energy-efficient cache architecture

for a near-threshold operation. The proposed architecture is a multi-way cache where an NT-SRAM and conventional 6T-SRAMs are utilized for one way and then the other ways, respectively. By swapping most frequently-accessed codes into a way composed of NT-SRAM, they obtain the energy reduction and maintain the performance at the same time.

At the same time, a number of researches on an NT-tolerant memory reduce energy by scaling a supply voltage down to a sub-threshold voltage [37, 38]. Some designs focus on improving SRAM read and write stability. A single-ended 6T-SRAM can operate stably below 200 mV at the cost of the area in comparison with the conventional 6T-SRAM [38]. A threshold-voltage ( $V_{th}$ ) optimized SRAM which isolates a read path and a write path operate stably at a 300 mV supply voltage with an acceptable area overhead [39, 43]. In addition to enhancing the robustness of SRAM, many researchers also look for alternative memory structures to SRAM: Spin-Transfer Torque Magnetic Random-Access Memory (STT-RAM) demonstrates a possibility of replacing SRAM on Last Level Cache (LLC) in multi-core systems [40]. For convenience, this chapter calls 6T-SRAM and 10T-SRAM as 6T and 10T in the following, respectively.

### 2.2.2 Standard-Cell Memory

Nowadays, in order to guarantee a stable operation in the near-threshold region, SCM has been studied as an alternative to SRAM. SCM, which consists of standard cells only, operates even in sub-threshold regions [37, 41, 42]. The SCM has a fully digital structure utilizing latch cells as storage elements. Fully digital structures are implemented in read and write circuitry.

Inherently, SCM has a better dynamic energy efficiency than SRAM. A bit-line-based read operation with a strong sense amplifier in SRAM results in a large effective capacitance on bit-line in each readout/write operation. Since read operation is accompanied by charging and discharging the bitline in every cycle, SRAM energy consumption is larger than SCM without a bit-line structure. As a result, SCM exhibits better energy-efficiency even than 10T-SRAM. However, the SCM area is about 3 × larger than that of full-custom SRAM [37, 42].

Based on related researches above, this chapter uses a more energy-efficient but less area-efficient SCM structure than NT-SRAM as the L0 filter cache to reduce the energy consumption at a cost of slightly increasing a miss rate. This chapter focuses on the non-linear relationship between the capacity and the miss rate to further reduce the energy consumption of a total memory system.

### 2.2.3 Relationship between Miss Rate and Cache Capacity

An important point for this approach is that the relationship between the cache capacity and the miss rate is non-linear [36]. Therefore, the energy composition can be reduced by replacing SRAM with NT-SCM under a fixed area constraint even if the L0 capacity decreases to one third.

If we simply replace all on-chip memories with NT-SCM, designers suffer from a huge loss of the cache capacity. As a result, the processor has to access an energy-consuming off-chip memory more often. As a trade-off, this chapter places a small NT-SCM-based L0-filter cache between the L1 cache and the CPU. The purpose of the placement is to divide the on-chip cache architecture into two parts, so that we can optimize them separately: a) The cache energy efficiency per access from CPU; b) Reduction in the total amount of off-chip memory accesses.

### 2.2.4 Motivational Example

A filter cache structure [20] is used as the research target in this motivational example. To simplify the point of view, we assume that the total energy consumption of a cache system only consists of the dynamic energy for on-chip caches in the example. All miss penalties are set at 1 clock cycle to bring data into the on-chip cache.

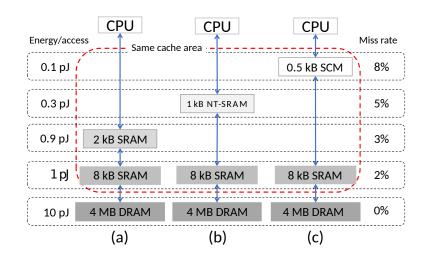

Fig. 2.2 shows an example of three different memory configurations with a 6T-based L0 cache, a 10T-based L0 cache, and an SCM-based L0 cache system as (a), (b), and (c), respectively. The energy consumption per access and corresponding miss rate is also written in the figure. It should be mentioned all cache systems occupy the same on-chip area.

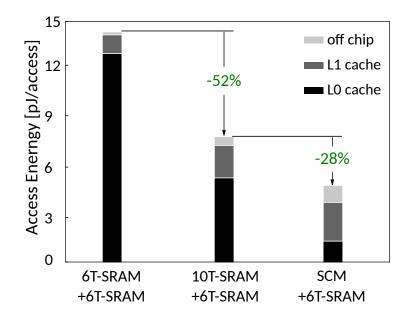

Since a 6T-based cache consumes more energy than low-voltage memories, this chapter replaces 6T with an NT memory in the L0 filter cache. When we replace 6T with a lower-area-density NT memory, the capacity is decreased, hence, the miss rate increases at the same time. If we can make good use of the non-linear relationship between capacity and miss rate, the energy overhead caused by the increase of the miss rate can be less than the energy reduction caused by implementing the NT-tolerant memory to the L0 cache. Here is a motivational example to explain the idea. The energy efficiency of the 10T-based L0 cache is  $3 \times$  better than that of the 6T-based L0 cache. At the same time, with the replacement of 6T with 10T, the L0 cache miss rate is only increased by 2% with the regress of the cache capacity. As a result, the 10T-based L0 cache has a larger energy reduction than the 6T-based one on the left in Fig. 2.3. As a result, the 10T-based L0 cache system achieves 52% less energy consumption than the 6T-based L0 cache. Following the

Figure 2.2: Three different cache architecture in the same on-chip area: (a) a 6T-based L0 cache, (b) a 10T-based L0 cache, (c) an SCM-based L0 cache.

same idea, using SCM instead of 10T, the miss rate is only increased by 3% but achieves  $3 \times$  more energy reduction than the 10T-based L0 cache. By replacing 10T with SCM, 28% total energy reduction is achieved compared with the 10T-based L0 cache.

## 2.3 Energy-Efficient Hybrid Cache System

In this section, we propose a hybrid cache structure to reduce the overall power consumption of the memory system under a given area constraint.

### 2.3.1 2-Level Hybrid Cache System

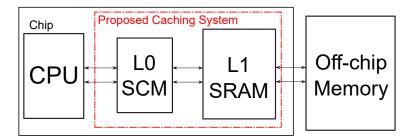

A hybrid 2-level on-chip cache system is proposed which is shown in Fig 2.4. Since the L0 cache has the highest access frequency and dominates the energy efficiency of the entire memory system, the L0 cache is built up of SCM which shows better energy efficiency than 10T SRAM. The L1 cache requires a larger capacity than the L0 cache to limit the energy-consuming off-chip memory access. Therefore, the L1 cache is built up of 6T-SRAM which shows better area efficiency than SCM. The rest of this chapter is to find an energy-efficient combination of SCM and 6T-SRAM capacities that minimizes the energy consumption of the entire cache system under various combinations of constraints.

Minimizing the L0 penalty enables a further energy reduction since it reduces the number of L1 read cycles and L0 write cycles when the L0 cache misses. Therefore, this chapter limits L0 cache penalty to 1 by an early restart technology [18], where a requested code is sent to the L0 cache and CPU simultaneously when the L0 cache misses.

Figure 2.3: Access energy comparison of an example architecture.

Figure 2.4: Proposed hybrid 2-level cache system consisting of an SCM-based L0 cache.

Since it only requires 1 cycle cache access, it has little penalty on energy consumption. The optimization of set associativity and block size is beyond the scope of this chapter. Therefore, this chapter specifies the caches discussed in Tab. 2.1. The associativity of the L0 cache and the L1 cache is 2-way. The line sizes of the L0 cache and the L1 cache are 16 words/line and 64 words/line, respectively.

| Table 2.1. Cache setup for vermeation in RISC-V processor. |                         |          |              |  |  |

|------------------------------------------------------------|-------------------------|----------|--------------|--|--|

| Cache location.                                            | Associativity Line size |          | Miss penalty |  |  |

| LO                                                         | 2-way                   | 16 words | 1 clock      |  |  |

| L1                                                         | 2-way                   | 64 words | 64 clocks    |  |  |

Table 2.1: Cache setup for verification in RISC-V processor.

### 2.3.2 **Problem Definition**

The energy consumption of a cache system can be modeled using the write and the read energy of a target memory. If a cache hit has occurred in the L0 cache, only read energy for one L0 cache access is consumed. If a cache miss has occurred for the L0 cache access, write energy in the L0 cache is consumed to write correct values back to the L0 cache. Moreover, the cache system accesses the higher-level cache (i.e. L1 cache) to request corresponding codes, which leads to extra energy overhead. In the same way, the energy consumption of the entire cache system can be iteratively defined in accordance with miss results of the L0/L1 cache and the off-chip memory access. The energy consumption per access of the whole cache system ( $E_{total}$ ) can be expressed as follows:

$$E_{\text{total}} = E_{\text{read}} + E_{\text{write}} + E_{\text{leak}},\tag{2.1}$$

where  $E_{\text{read}}$ ,  $E_{\text{write}}$  and  $E_{\text{leak}}$  are energy consumption per access of the read energy, the write energy, and the leakage energy, respectively.  $E_{\text{read}}$  is expressed as follows:

$$E_{\text{read}} = R_{\text{L0}} + R_{\text{L1}} \cdot M_{\text{L0}} \cdot P_{\text{L0}} + R_{\text{off}} \cdot M_{\text{L0}} \cdot M_{\text{L1}} \cdot P_{\text{L1}}, \qquad (2.2)$$

where  $R_{L0}$ ,  $R_{L1}$ ,  $R_{off}$ ,  $M_{L0}$ ,  $M_{L1}$ ,  $P_{L0}$  and  $P_{L1}$  are L0 cache read energy per access, L1 cache read energy per access, off-chip memory read energy per access, L0 miss rate, L1 miss rate, L0 miss penalty and L1 miss penalty, respectively. The miss penalty is the number of extra clock cycles introduced by the cache miss. For example, if the L0 cache in Fig. 2.4 does not have instruction codes requested by CPU, a miss in the L0 cache occurs. When the L0 cache copies instruction codes from the higher level cache (i.e., L1 cache) due to the L0 cache miss, CPU suspends its pipeline, which leads to extra clock cycles introduced by the same way, the miss penalty for the L1 cache is defined as the number of clock cycles in which the L1 cache copies instruction codes from the off-chip memory due to the L1 cache miss.

$E_{\text{write}}$  is expressed as follows:

$$E_{\text{write}} = W_{\text{L0}} \cdot M_{\text{L0}} \cdot P_{\text{L0}} + W_{\text{L1}} \cdot M_{\text{L0}} \cdot M_{\text{L1}} \cdot P_{\text{L1}}, \qquad (2.3)$$

where  $W_{L0}$  and  $W_{L0}$  are L0 write energy per access and L1 write energy, respectively.

$$E_{\text{leak}} = E_{\text{leak}_{\text{L0}}} + E_{\text{leak}_{\text{L1}}} + E_{\text{leak}_{\text{off}}},\tag{2.4}$$

where  $E_{\text{leak}_{L0}}$ ,  $E_{\text{leak}_{L1}}$ ,  $E_{\text{leak}_{off}}$  are L0 cache leakage energy consumption per access, L1 cache leakage energy consumption per access and off-chip memory leakage energy consumption per access.

The total access time is shown in Eq. (2.5):

$$T = (I + M_{L0} \cdot P_{L0} + M_{L1} \cdot P_{L1})/F \le T_{\text{constraint}},$$

(2.5)

where I, F and  $T_{\text{constraint}}$  are the total number of instruction cycles, frequency and time constraint, respectively. Since the access time of NT memory is dominant in the proposed cache system, this chapter assumes that F is the same as the operating speed of the L0 cache.

We assume that the total area of the cache system can be expressed as Eq. (2.6).

$$A_{\text{total}} = A_{\text{L0}} + A_{\text{L1}} \le A_{\text{constraint}},\tag{2.6}$$

where  $A_{\text{total}}$ ,  $A_{\text{L0}}$ ,  $A_{\text{L1}}$  and  $A_{\text{constraint}}$  are the total area of the cache system, L0 cache area, L1 cache area and area constraint, respectively. This chapter assumes that the area of each cache is proportional to its capacity.

Under specific combination constraints, this chapter evaluates the energy consumption of the hybrid 2-level cache system with combined NT memory and 6T-SRAM. We utilize the analytical performance models Eq. (2.1) (2.5) (2.6) to find an energy-efficient combination of the L0 cache capacity, its  $V_{DD}$ , and the L1 cache capacity. In order to reduce the leakage energy consumption, the body bias  $(V_{BB})$  is also tuned in this chapter.

# 2.4 Verification of Hybrid Cache for 65nm RISC-V Processors

This section evaluates a multi-level hybrid cache system implemented into a RISC-V processor [44].

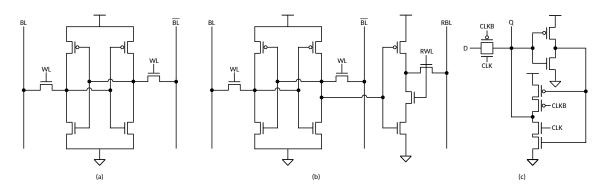

Figure 2.5: Candidate cells: (a) Differential 6T-SRAM, (b) 10T-SRAM and (c) Standard-Cell Memory.

### 2.4.1 Evaluation Setup

In order to verify the proposed hybrid cache system, a 2-level instruction hybrid cache memory is designed using a 65-nm process technology as a case study. This chapter selects a conventional 6T-SRAM, a 10T-SRAM, and an SCM-based L0 cache architecture.

Fig. 2.5 (a) shows a differential 6T-SRAM bit cell. As many papers point out, a stable operation in readout and write can no longer be guaranteed in the NTV region [39][43][45]. 10T-SRAM isolates read and write paths by providing two additional transistors in order to guarantee a stable operation in the NTV region [43]. 10T makes separate optimization available through isolating read and write operations. The specific method of isolation is to add two NMOS transistors in Fig.2.5 (b) dedicated to read operations, which are controlled by read word and read bit-line respectively to implement a single-ended read. This read circuity determines the read stability of the 10T cell. Since read and write operations are separated, we can independently improve the robustness of the write operation regardless of read operations to make it stable at the NT voltage region.

However, the robustness of read and write are accompanied by penalties of area. Since the read operation is single-ended, without differential sense amplifiers, 10T cells suffer from a larger delay. Therefore, the size of the NMOS transistor on the read path must be increased to mitigate delay penalties caused by the single-ended read operation. As a result, NT-tolerant 10T has at least 66% area penalty compared to conventional 6T [43]. This chapter considers differential 10T-SRAM as a representative of NT-tolerant SRAMs. Latch cells depicted in Fig. 2.5 (c) are implemented into SCM. Since SCM employs digital structures only, it can stably operate in the NTV region. At the same time, SCM consumes several larger area than SRAM due to its large readout logic.

Tab. 2.2 summarizes the comparison between three types of memory designs. When the supply voltage is near the threshold voltage, leakage powers of 10T and SCM are

| 1 kB mem.                              | 6T-SRAM [15] | 10T-SRAM [43] | SCM [42]  |

|----------------------------------------|--------------|---------------|-----------|

| Basis of results                       | 65 nm model  | 65 nm AM      | 65 nm PLS |

| Supply voltage [V]                     | 0.8          | 0.4           | 0.4       |

| Freq.                                  | 1.3 GHz      | 586 kHz       | 30.6 MHz  |

| Leak [pW/bit]                          | 2.4          | 2.81          | 13        |

| Dyn. Energy* [fJ/bit]                  | 101          | 25.8          | 10.9      |

| Cell area [ $\mu$ m <sup>2</sup> /bit] | 1.6          | 2.9           | 8.0       |

| Energy × Area                          | 161.6        | 74.8          | 87.2      |

Companies a batware (T SD AM 10T SD AM and SCM

\*: Average energy consumption (read and write operations). AM: ASIC measurement. PLS: Post-layout simulation.

greatly increased. The area overhead of 10T and SCM over 6T are 64% and 500%, respectively. The energy-area product is also listed in the table as a reference here.

To guarantee a stable signal transmission from the CPU core operating in the NTV region to the nominal-voltage 6T-SRAM, level shifters are implemented into corresponding data paths. This chapter considers the effect introduced by the level shifter. The evaluation is based on the level shifter proposed in [46]. The area of one level shifter is evaluated based on the actual layout in the 65-nm process technology. The result shows that the area of the level shifter is 6  $\mu$ m<sup>2</sup>. Since the supply voltage for the CPU core is tuned depending on a frequency constraint, this chapter evaluates the energy consumption and the delay of the level shifter with HSPICE under various voltage conditions. For example, if the input and the output voltages are 0.4 V and 0.8 V, respectively, the energy consumption and the delay of the level shifter are 5 fJ and 1.8 ns, respectively. The overhead introduced by level shifters is added to the performance models presented from Eq. (2.1) to Eq. (2.6). For example, the area overhead of level shifters implemented into the L1 cache memory is included in  $A_{L1}$  in (2.6).

As a summary, the following memories are used in the experiments:

- SCM: An SCM proposed in Ref. [42] is used as a representative of SCM. Area, energy, and operating speed are evaluated through a post-layout gate-level simulation in the commercial 65-nm process technology. The supply voltage is scaled from 0.4 V to 1.2 V. Body bias is scaled from -0.8 V to 0.4 V.

- 10T-SRAM: A 10T-SRAM model is used [43]. Supply voltage is scaled from 0.4 V to 1.0 V. Body bias is fixed at 0 V.

- 6T-SRAM: The low power SRAM model in CACTI Ver. 7.0 is used to estimate the

performance of SRAMs [15]. Supply voltage is fixed at 0.8 V. Body bias is fixed at 0 V.

• Off-chip memory : Main memory mode in CACTI Ver. 7.0 is utilized [15].

Since the energy consumption of 6T-SRAM, 10T SRAM, and SCM are evaluated by the CACTI model, the ASIC measurement, and the post-layout simulation, respectively, the delay and the energy consumption caused by the wiring capacity of the data line and the selector are also included in the simulation of this chapter. In general, the performance of a memory depends on its capacity. However, Ref. [43] presents measurement results for a 32 kB capacity only. In order to estimate the delay and the energy consumption of 10T SRAM with various capacities, we utilize the capacity dependency of the 6T CACTI model [15]. For example, let us consider a case where the capacity of 6T-SRAM is reduced from 32 kB to 16 kB. Suppose the read energy determined by the 6T CACTI model is reduced by 28% through the capacity reduction. This chapter assumes that the read energy of 10T SRAM is also reduced by 28% if its capacity is reduced from 32 kB to 16 kB.

A code tracing log is firstly generated through a Register-Transfer-Level (RTL) simulation for a RISC-V processor running benchmark programs. Note that the processor has no cache memories in the log generation. Based on the code tracing log, the following cache activity is calculated assuming that the processor employs the corresponding cache system:

- The number of cache misses/hits,

- the number of cache read operations, and

- the number of cache write operations.

Combining the cache activity and the physical performance data for 6T-SRAM and NTtolerant memories, this chapter evaluates the entire performance (i.e., delay, energy consumption, and area) of the target cache system. Note that this chapter does not consider the effect of control logic circuits, and a tag memory assuming that the performance of the NT-tolerant memory and the 6T-SRAM is a dominant source that determines the performance of the entire cache system.

### 2.4.2 Experimental Results

This chapter focuses on the environment such as sensor networks where several dedicated applications are executed on the chips. Therefore, this chapter utilizes several

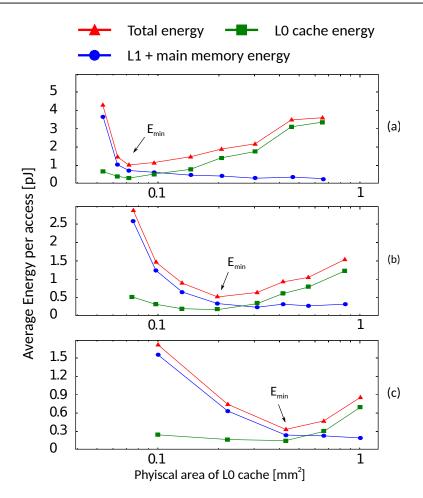

Figure 2.6: Three energy consumption per access of the memory system against the L0 cache capacity of DCT program: (a) Hybrid cache system with 6T-based L0 cache, (b) Hybrid cache system with 10T-based L0 cache, (c) Hybrid cache system with SCM-based L0 cache.

commonly used four typical programs for wireless communications, including Discrete Cosine Transform (DCT), Fast Fourier Transform (FFT), Secure Hash Algorithm 3 (KEC-CAK), Secure Hash Algorithm (SHA), and a mixed program which executes four programs sequentially, to evaluate the hybrid cache energy. This chapter refers to the mixed program hereafter as MIX. This chapter follows the methodology discussed in Section 2.3.2 to find an energy-efficient hybrid cache solution under different constraints. This chapter targets to find an energy-efficient hybrid cache system under a given area and frequency constraint. This chapter adjusts capacities of the L0 cache and the L1 cache to meet the area constraint. Therefore, by scaling  $V_{DD}$  of the NT-L0 cache, this chapter minimizes the total energy consumption of the cache system under the given time constraint.

The minimum energy point  $E_{\min}$  can be found by considering the energy consumption of the current level cache and the next level cache. If we utilize more energy-efficient but low-density memory, the value of  $E_{min}$  should be smaller. At the same time, the required area to achieve  $E_{min}$  of the NT memory is also larger than  $E_{min}$  of 6T at the same time. This chapter evaluates the energy consumption in DCT to illustrate the claim in Fig. 2.6. The capacities of the L1 cache and the off-chip main memory are set as 16 kB and 4 MB, respectively. When the area of the L0 cache is greater than 0.1 mm<sup>2</sup>, the miss rate tends to be convergent. Therefore, when using the 6T-based cache to execute the program, the capacity of the L0 cache reaches 4 kB when the area is less than 0.1mm<sup>2</sup>. The reason is that the 6T's area density is the largest among the three candidates. The total energy consumption of the 6T-based cache system reaches  $E_{min}$  which has a value of 1.07 pJ/access, with the area of 0.1mm<sup>2</sup>. The 6T-based L0 cache achieves minimum energy consumption at the same time. Moreover, the 10T-based cache achieves  $E_{min}$ , which is 0.64 pJ/access. At this moment, the 10T-based L0 cache consumes 0.2 mm<sup>2</sup> due to the relatively worse area density than the 6T cache.

The SCM-based hybrid cache system, which is more energy-efficient but low-density, achieves the smallest  $E_{min}$  among three candidates. However, where the area constraint is particularly tight, the SCM-based hybrid cache system can no longer reduce the energy consumption due to a sharply increased miss rate of the L0 cache. When we use the proposed SCM-based cache system, the SCM-based cache reaches  $E_{min}$  in the area of 0.4 mm<sup>2</sup> due to its low area density. However, since SCM has better energy efficiency than both 6T-SRAM and 10T-SRAM,  $E_{min}$  is reduced to 0.48 pJ/access, which indicates the total energy consumption of the SCM-based cache is 39% of the 6T-based cache system. Also, compared to two SRAM-based L0 caches, the proposed cache still exhibits smaller energy consumption when the area constraint is not less than 0.1 mm<sup>2</sup>.

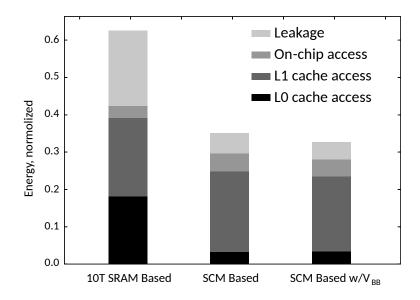

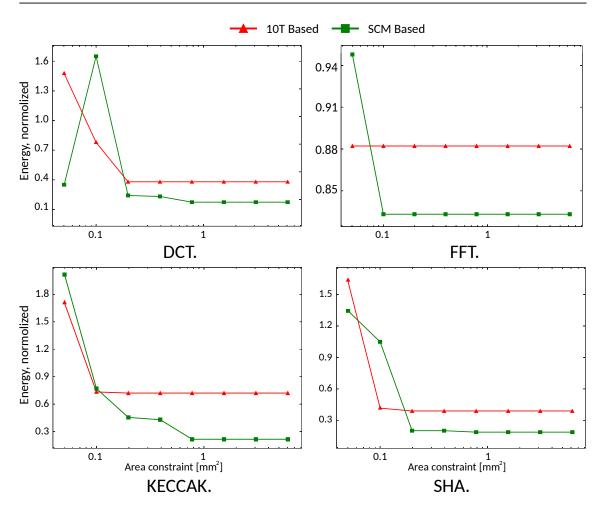

Figs. 2.7, 2.8 show the energy consumption under loose constraints (Area < 0.4 mm<sup>2</sup>, Freq. > 1 MHz) of the proposed cache system when the processor executes benchmarks. The results are summarized in Tab. 2.4.2. Since the 10T cache has a higher area density than the 6T one, under the same area constraint, the 10T-based L0 capacity is twice as large as the SCM-based L0 one. However, because of SCM's better energy consumption than 10T SRAM, the total energy of the SCM-based hybrid cache system achieves 4.59  $\mu$ J while the 10T-based cache achieves the 9.26  $\mu$ J energy consumption. By applying a body biasing technique [47], the leakage energy can be reduced at the cost of degrading the operating speed of the cache system. Up to 1% energy consumption is reduced by the body biasing technique. This implies that the optimum body bias voltage is around the zero bias condition. The evaluation results for the rest programs are shown in Fig. 2.8. The total number of clock cycles required to execute the mixed program is around one million. In Fig. 2.8, the energy consumption is normalized by the energy of the 6T-based

Figure 2.7: Energy consumption normalized by 6T-based cache system of MIX program under Area  $< 0.4 \text{ mm}^2$ , Freq. > 1 MHz.

Table 2.3: Hybrid cache system parameters of the energy-efficient combination of MIX program under Area  $< 0.4 \text{ mm}^2$ , Freq. > 1 MHz.

|                                |         | ,            | 1        |          |         |

|--------------------------------|---------|--------------|----------|----------|---------|

| Cache Type                     | Energy  | $V_{\rm DD}$ | $C_f L0$ | $C_{L1}$ | Freq.   |

| 10T-based                      | 9.26 μJ | 0.5 V        | 4 kB     | 8 kB     | 3.6 MHz |

| SCM-based                      | 4.59 μJ | 0.4 V        | 2 kB     | 8 kB     | 22 MHz  |

| SCM-based w/ V <sub>BB</sub> * | 4.55 μJ | 0.4 V        | 2 kB     | 8 kB     | 4.9 MHz |

$V_{\text{DD}}$  and  $V_{\text{BB}}$  are supply voltage and body bias for the L0 cache, respectively.  $C_{\text{L0}}$  and  $C_{\text{L1}}$  are the capacities of two caches, respectively

\*:  $V_{\text{BB}}$  is set as -0.7 V.

#### cache.

For the 2-level SRAM-based cache system, the miss rate is considerably low since the area efficiency of SRAM is high. The proposed hybrid system, on the other hand, exploits the high energy-efficiency of SCM and high area-efficiency of SRAM. As a result, if we target a 0.4 mm<sup>2</sup> area constraint, the proposed system achieves 51% better energy efficiency than the 2-level 10T-based cache system when processing the MIX program. The proposed cache can achieve 68% less energy consumption than the conventional 6T-based cache system when processing the MIX program.

The proposed SCM-based hybrid cache system achieves further energy reduction exploiting a trade-off between energy feature and area-density feature of the L0 cache. Utilizing the non-linear relationship between capacity and miss rate, this chapter replaces the conventional near-threshold 10T-based L0 cache with a more energy-efficient but low

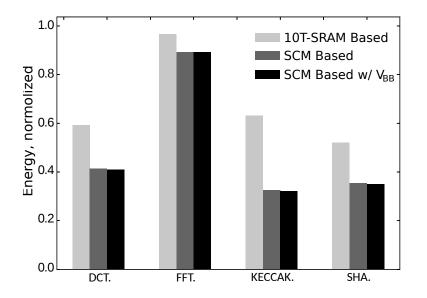

Figure 2.8: Energy consumption normalized by 6T-based cache system of DCT, FFT, KECCAK, SHA under Area  $< 0.4 \text{ mm}^2$ , Freq. > 1 MHz.

area-density SCM one. As a result, more than half of energy consumption can be reduced.

### 2.4.3 Applicable Range Analysis

In the previous section, this chapter got the conclusion that the proposed cache system is more energy-efficient than the 10T-based cache system. However, if area constraints are too tight, the SCM-based hybrid cache suffers from the energy penalty introduced by its poor capacity. At the same time, the application such as IoT only requires a moderate operating speed. Analysis of the relationship between energy consumption and operating frequency can guide us in practical applications. Therefore, this section will further analyze the energy consumption of the proposed hybrid cache under different area and time constraints.

Figure 2.9 shows the energy consumptions of the 2-level caches with 10T-L0 and SCM-L0 as functions of area constraints. The energy consumption is normalized by the 2-level cache with SRAM-L0 under the same area constraint. Time constraints are not considered. Note that area constraints "0.1 mm<sup>2</sup>" and "0.8 mm<sup>2</sup>" in the X axis of Fig. 2.9, correspond to the area of SRAM 8 kB and SRAM 64 kB, respectively. Although the SCM area density is lower than that of the 6T-SRAM, the proposed SCM-based 2-level hybrid cache system has a large advantage due to its energy efficiency for speed-insensitive processing.

When an ultra low-energy oriented application is targeted, CPU requires near-threshold operation where 6T-SRAM cannot operate correctly due to its vulnerability against noise

Figure 2.9: Normalized energy comparisons among three 2-level caches against 6T-based cache system under a loose freq. constraint towards the mixed program.

and process variability. Therefore, with a 6T-only configuration for the cache, we cannot lower the energy consumption of CPU sufficiently even if the performance required for a target application is very low. Compared to a 10T-based hybrid cache design, although SCM has a lower area density, in the cases when area constraints are not lower than 0.1 mm<sup>2</sup> from the simulation results, the SCM-based 2-level cache has an energy reduction due to energy feature advantages.

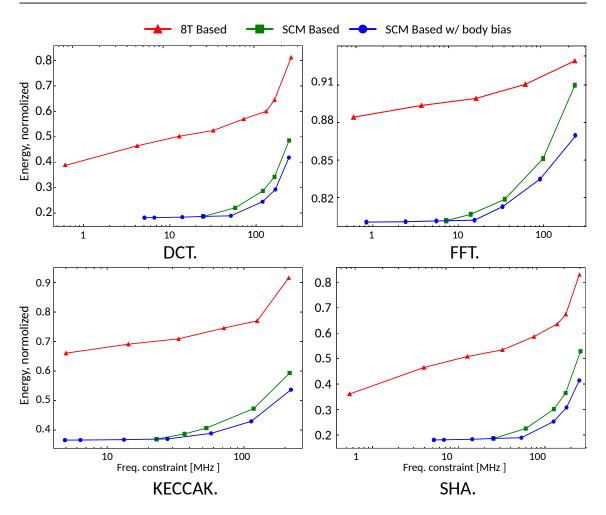

Fig. 2.10 shows evaluation results under a loose area constraint. Note that frequency constraints are tuned unlike Fig. 2.9. The X axis represents a frequency constraint. The Y axis is the normalized energy consumption against the 2-level hybrid cache system with the 6T-based L0 cache under the same area constraint, which is the same as Fig. 2.9. Area constraints are not considered here. When frequency constraint is tightened, the NT-tolerant cache system must raise the L0 cache V<sub>DD</sub>, which leads to the energy overhead. When the target frequency is higher than 100 MHz, the entire cache system will not work

Figure 2.10: Normalized energy comparisons of 2-level hybrid caches against 6T-based cache system under a loose area constraint towards the mixed program.

properly because NT-L0 cannot meet the frequency requirement. However, if we relax the timing constraint, the proposed cache exhibits 64% better energy efficiency than the 2-level 10T-based cache at the best case shown in Fig. 2.10.

The reduction in energy consumption introduced by body bias optimization is no more than 1% when the target frequency is less than tens of MHz. As described before, this is because the optimum body bias condition for the SCM is around the zero bias condition. However, if the frequency constraint becomes more than tens of MHz, the situation becomes different. In order to boost up the operating speed of the SCM, the supply voltage is typically boosted up, which leads to an increase of the dynamic energy consumption. By applying forward body biasing, the supply voltage can be reduced without violating the frequency constraint. As a result, the energy consumption of the proposed SCM-based cache can be reduced by up to 26% by applying forward body biasing.

In summary, when the area constraint is not less than 0.1mm<sup>2</sup> and the frequency constraint is not more than 100 MHz, SCM-based L0 cache achieves total energy reduction by a trade-off between energy efficiency improvement but area feature reduction.

The essence of trade-off is to exploit the nonlinear relationship between capacity and miss rate. When the area constraint is loose, the cache capacity is large enough hence the descrease of cache capacity will not severely increase the miss rate. In such a situation, energy reduction is expected with the replacement of a more energy-efficient but low-capacity SCM-based cache. However, when the area constraint is too small, the corresponding cache capacity will be small. Therefore, a slight cache capacity reduction will also lead to a rapid increase in the cache miss rate, making this trade-off no longer energy-efficient.

### 2.5 Summary

Based on the non-linear relation between cache miss rate and capacity, a case study is discussed to show SCM-based design has an energy advantage than 10T-based design. SCM has a low processing speed, a low area density but an inherent energy efficiency. Utilizing SCM as the L0 filter cache, the 2-level hybrid cache system exhibits 68% better energy consumption than a conventional 6T-based cache system in the simulation on average. When an ultra-low-power oriented application is targeted, the CPU requires near-threshold operation where 6T cannot operate correctly due to its vulnerability against noise and process variability. If we utilize 10T for near-threshold operation, due to the SRAM read operation by a strong sense amplifier, it is still not energy-efficient enough. In contrast, if the CPU is under a near-threshold operation, the SCM operates very well with the same supply voltage as the CPU logic. Based on this work, this chapter found that in an ULP working environment, the energy efficiency of a lower-level cache is far more important.

## Chapter 3

# **DNN Accelerator Designs for Large-Scale Processing with Regular Access Pattern**

## 3.1 Introduction

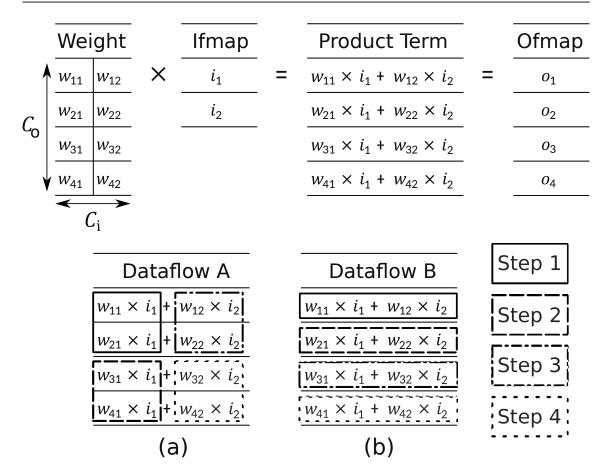

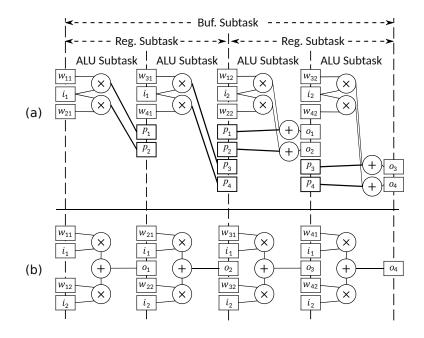

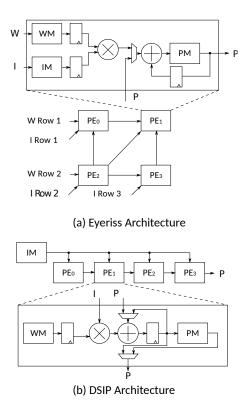

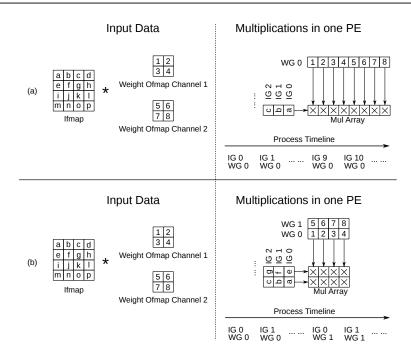

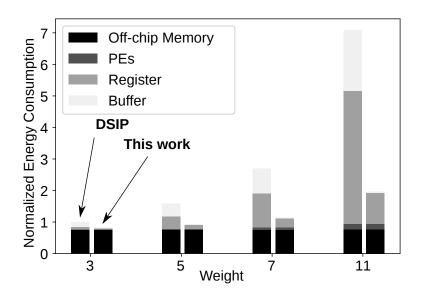

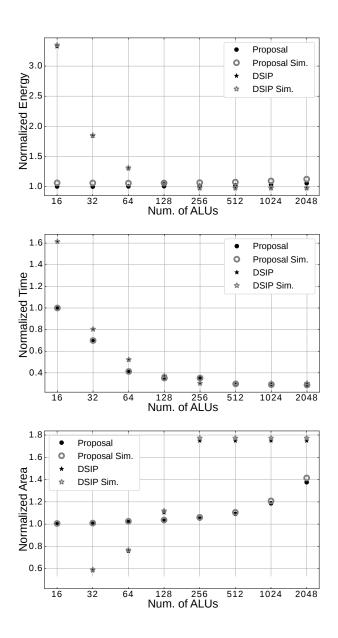

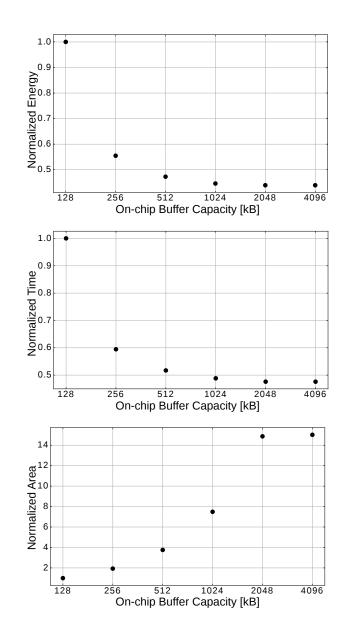

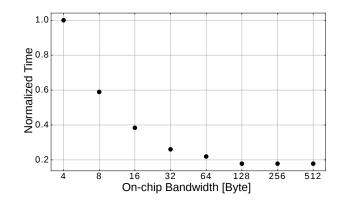

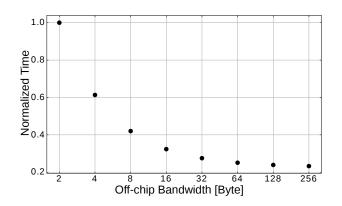

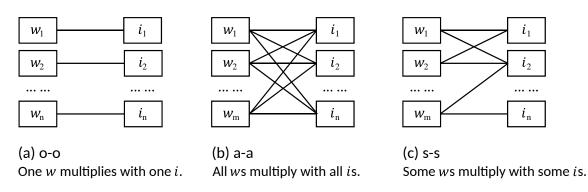

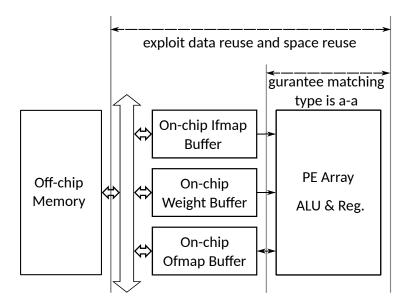

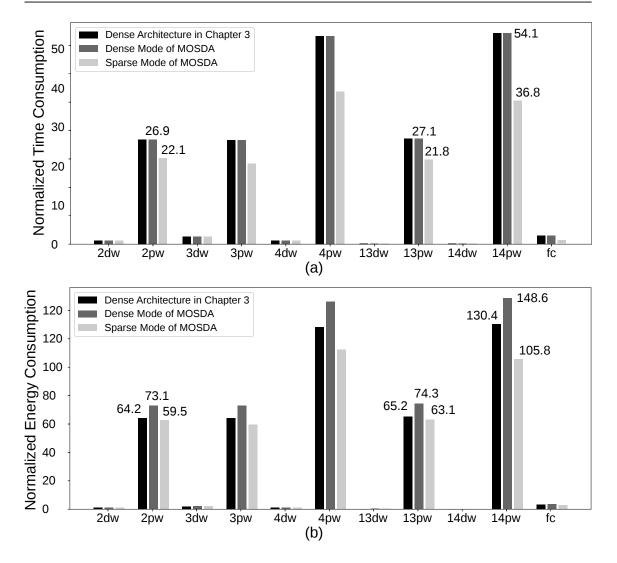

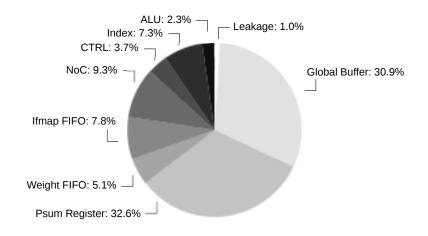

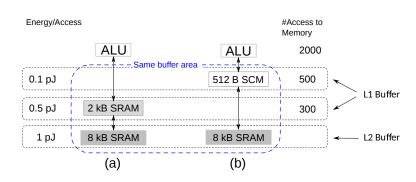

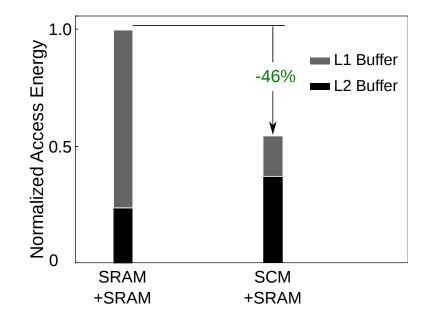

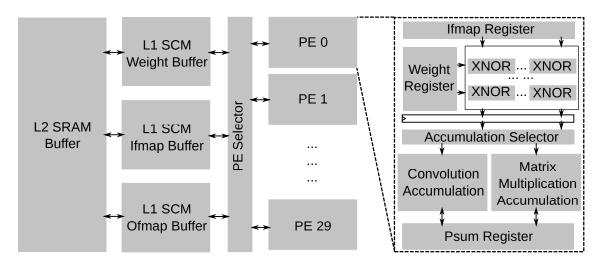

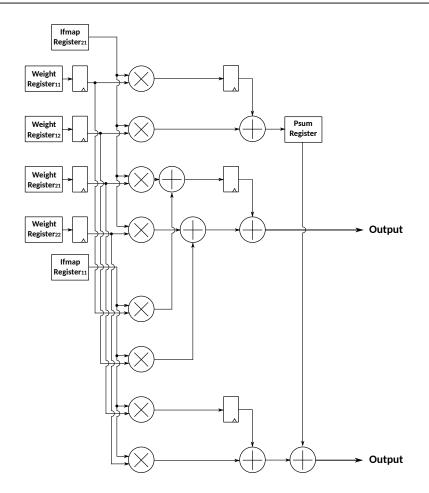

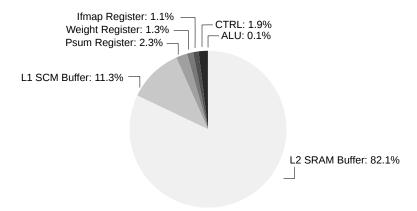

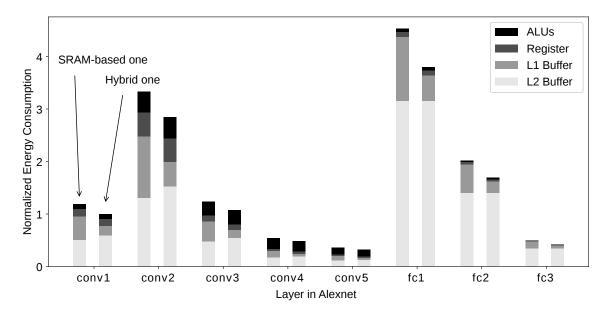

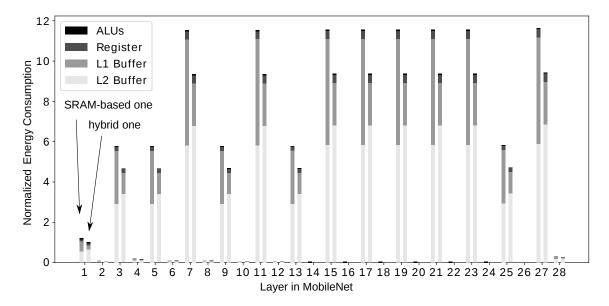

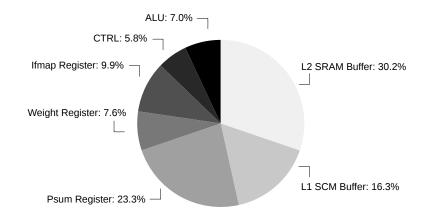

In recent years, the prediction accuracy of Deep Neural Network (DNN) has been steadily increasing with the improvement of network structure [48]. As a result, DNN has been widely used in all aspects of life such as image processing and language modeling. Therefore, many endpoint terminals integrate Application-Specific Integrated Circuits (ASICs) to perform local real-time inference [49–51]. However, the high-precision prediction is often accompanied by an increase in computational complexity [52, 53].