# Dominant Model-Parameter Determination for the Analysis of Current Imbalance Across Paralleled Power Transistors

Yohei Nakamura<sup>®</sup>, *Student Member, IEEE*, Michihiro Shintani<sup>®</sup>, *Senior Member, IEEE*, and Takashi Sato<sup>®</sup>, *Senior Member, IEEE*

Abstract-In this article, we propose a new sensitivity-based analytical equation, the *n*-devices forward propagation of variance (NFPV). Using the proposed NFPV equation, the dominant device model parameters- essential for accurate analysis of energy-loss variation due to the current imbalance across paralleled power transistors from statistical parameter variations-are efficiently determined. The proposed method with the NFPV equation is faster than conventional methods that use Monte Carlo simulation. We conducted experimental validation using the measured currentvoltage characteristics of commercially available 100 silicon MOS-FETs and 300 silicon carbide MOSFETs. The results show that the proposed NFPV-based method efficiently finds the dominant device model parameters, which are sufficient and necessary to reproduce the energy-loss variation, regardless of the number of parallel transistors. The results also show that the determined dominant device model parameters are valid under practical situations, such as uneven parasitic inductances and device temperature imbalance among paralleled transistors. The proposed method determines the dominant device model parameters  $9.33 \times$  faster than the conventional method while maintaining the same accuracy. Additionally, we demonstrate that, compared with the conventional method, an increase in the number of candidate statistical model parameters increases the efficiency of the proposed method.

*Index Terms*—Current imbalance, device modeling, Monte Carlo (MC) simulation, power transistors, sensitivity analysis, silicon carbide (SiC) MOSFET.

#### I. INTRODUCTION

**P**OWER transistors are key components in power electronics. Among them, silicon carbide (SiC) MOSFETS have been attracting attention due to their excellent properties, such as low

Manuscript received 8 July 2022; revised 11 November 2022; accepted 13 December 2022. Date of publication 29 December 2022; date of current version 14 February 2023. This work was supported by JST-OPERA Program, Japan, under Grant JPMJOP1841. This work was presented at IEEE ENERGY CON-VERSION CONGRESS AND EXPOSITION, Vancouver, BC, Canada, Oct. 10, 2021 [DOI: 10.1109/ECCE47101.2021.9595345]. Recommended for publication by Associate Editor F. Luo. (*Corresponding author: Yohei Nakamura.*)

Yohei Nakamura is with the ROHM Co., Ltd., Kyoto 615-8585, Japan, and also with the Graduate School of Informatics, Kyoto University, Kyoto 606-8501, Japan (e-mail: yohei.nakamura@dsn.rohm.co.jp).

Michihiro Shintani is with the Department of Electronics, Kyoto Institute of Technology, Kyoto 606-8585, Japan (e-mail: shintani@kit.ac.jp).

Takashi Sato is with the Graduate School of Informatics, Kyoto University, Kyoto 606-8501, Japan (e-mail: takashi@i.kyoto-u.ac.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2022.3231894.

Digital Object Identifier 10.1109/TPEL.2022.3231894

ON-state resistance, high breakdown voltage, and fast switching speed [2], [3], [4], [5]. Due to these excellent characteristics, SiC MOSFETs can operate at higher switching frequencies, with lower switching losses and a wider range of operating temperatures than conventional power transistors. Particularly, their high-speed switching operation reduces the volume and weight of power converters, improving the energy efficiency of applications in electric and hybrid-electric vehicles, such as three-phase traction inverters, boost converters, and on-board chargers (OBCs) [6], [7], [8], [9].

Despite these advantages, the maximum current rating of a single SiC MOSFET may be insufficient for ultrahigh power applications [10], [11], [12], [13]. To manage this high power, investigators have considered the parallel operation of SiC MOS-FETs formed into a power module [10], [11], [12], [13], [14], [15], [16], [17]. However, in such paralleled device connections, variations in device performance must be treated cautiously because the variations may cause a current imbalance across the paralleled devices. Even devices fabricated on the same wafer can exhibit significantly different characteristics [18]. Once the current imbalance occurs, the energy-loss variation among the paralleled devices may cause some to become thermally overstressed, inducing the deterioration of the reliability of the power module. To estimate and control the current imbalance in advance, circuit simulations considering variations in the device parameters must be conducted [17], [19], [20].

Many studies have tackled the current imbalance in paralleled devices [16], [17], [19], [20], [21], [22], [23]. Experimental analyses were reported in [16], [19], and [21], but these works focused more on the impact of variations in parasitic circuit inductances than on variations in the device characteristics. In contrast, the influence of variations in device characteristics was studied experimentally in [17], [22], and [23]. Unfortunately, only a few devices were considered in these studies. In [20], statistical simulations were conducted to study the influence of variations in device characteristics on energy loss and junction temperature. However, the device model used in this work only considered the variation of two pre-determined model parameters: threshold voltage and current gain factor. However, depending on the circuit design and device model used, different model parameters may need to be treated as statistically variable parameters. Pre-determined model parameters may not

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

be suitable for reproducing the variations in an actual circuit operation.

Recent device models used in practical circuit designs contain many model parameters [24], [25], [26], [27], [28]. Due to computational costs and the necessary modeling effort, statistical circuit designs can only consider the statistical variations of a few model parameters. Simultaneously, the statistical properties of the circuit of interest need to be represented accurately [29]. To the best of our knowledge, no prior study has discussed using a limited number of statistical model parameters to analyze the current imbalance of paralleled power devices efficiently and accurately.

Recently, device modeling methods using machine learning, such as neural networks, have been proposed [30], [31]. These methods could accurately reproduce the electrical and thermal behavior of devices. However, they have all been applied to nonstatistical modeling, which requires less training data. Generally, machine learning-based methods require large training data, considerably lengthening training time. Data shortage may lead to a statistically low-precision model. From a time-efficiency perspective, establishing an analytical method that does not require training data is essential.

This work proposes a method for efficiently determining the dominant model parameters of a device, which are necessary for performing an accurate statistical analysis of the current imbalance of parallel-connected power transistors. The proposed method uses a sensitivity-based analytical equation that considers the correlations among the model parameters of nparalleled devices. The proposed equation can be considered a generalization of the equation for the forward propagation of variance (FPV) [32], [33], which estimates the influence of process variations on circuit performance in CMOS devices. Hereafter, we refer to the proposed equation as the n-devices FPV, or NFPV for short. The NFPV equation enables us to quantitatively evaluate the dominant parameters in the energy-loss variation of each device. To validate this approach experimentally, we used the measured drain current versus drain-source voltage  $(I_d-V_{ds})$  characteristics of commercially available silicon (Si) and SiC MOSFETs with their models that accurately reproduce the statistical variations of the switching operation [28], [34].

The main contributions of this article are as follows.

- We derived the NFPV equation for analyzing the current imbalance across paralleled power transistors. It is a general equation and can be employed to quickly evaluate the influence of statistical variations in the model parameters on the current imbalance, considering the interdependence among the paralleled devices.

- 2) We validated the NFPV-based parameter-determination method using actual SiC MOSFETs. The validation shows that the proposed method for determining the dominant model parameters is several orders of magnitude faster than the conventional method and works accurately in practical situations.

- 3) We validated the dominant model parameters under the practical situations, considering uneven parasitic inductances and device temperature imbalance among the paralleled devices in the power module.

The rest of this article is organized as follows. Section II introduces the current imbalance issue in paralleled power transistors. We also review the conventional approaches for determining the dominant model parameters for current imbalance analyses. Section III presents the proposed NFPV-based method for determining the dominant model parameters. In Section IV, we demonstrate that the proposed method can identify the dominant model parameters for various numbers of paralleled devices. We validated the proposed method by comparing its required computation time to that required by the conventional method. Finally, Section V concludes this article.

#### **II. PRELIMINARIES**

#### A. Current Imbalance of Paralleled Power Transistors

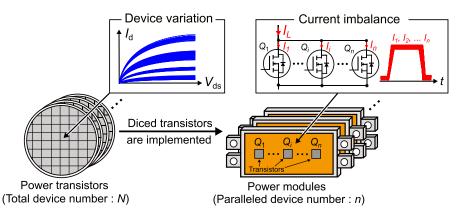

To handle currents exceeding the maximum rating of a power transistor, power transistors are connected in parallel to form a power module, where the load current is shared among the devices [10], [11], [12], [13], [14], [15], [16], [17]. Fig. 1 illustrates the current imbalance of paralleled transistors in power modules due to variations in the transistor characteristics. A total of Ntransistors are collected and used to assemble power modules, each comprising *n*-paralleled transistors. The quantities  $I_L$  and  $I_i$  (i = 1, 2, ..., n), respectively, denote the load and drain currents of each power transistor  $Q_i$  (i = 1, 2, ..., n), where n represents the number of paralleled transistors in the power module. While we expected an equal current distribution-i.e.,  $I_1 = I_2 = \cdots = I_n$ —the currents flow unequally through the paralleled devices because, in practice, the device characteristics of each transistor differ. This phenomenon is called "current imbalance" [19], [20], [21].

The current imbalance leads to variations in the energy losses among the paralleled devices. Consequently, some transistors suffer from excessive thermal stress, which accelerates the degradation of the device. Particularly, SiC MOSFETs have less mature manufacturing processes and MOS interface quality than conventional silicon-based power transistors, resulting in significant variations in device characteristics and severe thermal problems [14]. Therefore, it is essential to understand how variations in the characteristics of paralleled SiC MOSFETs affect the current imbalance. Since it is difficult to determine this effect experimentally—as that requires measuring the current through each device packaged in the power module— a simulation-based statistical analysis is crucial.

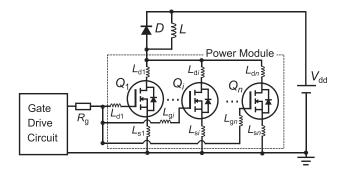

We present here a motivational example for analyzing the current imbalance caused by variations in device characteristics. Let us consider the switching operation of the power module shown in Fig. 2, which has *n*-paralleled transistors in an inductive load-switching circuit. In Fig. 2, the quantities  $V_{dd}$ , L, D, and  $R_g$  denote the secondary supply voltage, the load inductance, a free-wheeling diode, and the gate resistance.  $L_{gi}$ ,  $L_{di}$ , and  $L_{si}$  are the parasitic inductances for each terminal of  $Q_i$  (i = 1, ..., n). We assume that the threshold voltage  $v_{th(i)}$  and the transconductance  $g_{m(i)}$  of the *i*th transistor,  $Q_i$  (i = 1, 2, ..., n), are the model parameters for considering statistical variations. The other model parameters are assumed to be constant and invariant, that is, their values are equal for each transistor. We denote the switching energy loss of transistor  $Q_i$  by  $E_i$

Fig. 1. Current imbalance across paralleled transistors in power modules due to variations in the device characteristics. A total of N transistors are collected and used to assemble power modules. From these, n transistors are selected and connected in parallel to assemble each power module. The quantities  $I_L$  and  $I_i$  (i = 1, 2, ..., n), respectively, denote the load and drain currents of each power transistor  $Q_i$  (i = 1, 2, ..., n) in the power module.

Fig. 2. Inductive load-switching circuit with *n*-paralleled transistors in a power module. The quantities  $V_{dd}$ , L, D, and  $R_g$  denote the secondary supply voltage, the load inductance, a free-wheeling diode, and the gate resistance.  $L_{gi}$ ,  $L_{di}$ , and  $L_{si}$  are the parasitic inductances for each terminal of  $Q_i$  (i = 1, ..., n).

and evaluate how the variations in the device characteristics affect the current distribution imbalance and energy loss. When  $v_{\mathrm{th}(i)}$  is lower than the threshold voltage of the other paralleled devices, a larger current flows through  $Q_i$ , leading to a larger  $E_i$  than in the others. A similar current distribution would be observed if  $g_{\mathrm{m}(i)}$  were higher than the transconductances of the other devices. Meanwhile, if the threshold voltage of another device [e.g.,  $v_{\mathrm{th}(j)}$  ( $i \neq j$ )] happened to be lower than those of the others, a larger current would flow through  $Q_j$  and decrease  $E_i$ . This observation indicates that the current through a device is determined by variations in its model parameters and the changes in the model parameters of other devices. Therefore, we must consider the interactions among all the devices when analyzing the current imbalance of paralleled devices.

In this example, we limited ourselves to considering just the two model parameters  $v_{th(i)}$  and  $g_{m(i)}$  as statistical parameters. However, other model parameters may also require statistical handling. Additionally, the impact of the current imbalance can vary significantly for each parameter. Since the computational costs of statistical simulations drastically increase as the number of statistical parameters and their interactions increase, it is necessary to determine the dominant model parameters that

| Algorithm 1: | MC-Based | Determination | of the | Dominant |

|--------------|----------|---------------|--------|----------|

| Parameters.  |          |               |        |          |

| Re | quire: $P, p, n, L_{\max}, err_{\text{accept}}$                                                                        |

|----|------------------------------------------------------------------------------------------------------------------------|

| 1: | $\sigma_{E_i}^m = \text{MCSIM}(\boldsymbol{P}, \boldsymbol{p}, n, L_{\max})$                                           |

| 2: | for $(m_{\rm r} = 1; m_{\rm r} < m; m_{\rm r}$ ++) do                                                                  |

| 3: | for each $oldsymbol{p}_{m_{	ext{r}}}\inoldsymbol{p}$ do                                                                |

| 4: | $\sigma_{E_i}^{m_{\mathrm{r}}} = \mathrm{MCSIM}(\boldsymbol{P}, \boldsymbol{p}_{m_{\mathrm{r}}}, n, L_{\mathrm{max}})$ |

| 5: | calculate $err\_\sigma_{E_i}$                                                                                          |

| 6: | end for                                                                                                                |

| 7: | end for                                                                                                                |

| 8: | select $p_{m_{\rm r}}$ with the smallest $m_{\rm r}$ , giving $err\_\sigma_{E_i}$                                      |

|    | within $err_{ m accept}$ as $p_{ m dominant}$                                                                          |

| 9: | return <i>p</i> <sub>dominant</sub>                                                                                    |

considered the minimal and indispensable set of model parameters to analyze the current imbalance.

### B. Determination of the Dominant Model Parameters

To determine the dominant model parameters, we assume that N power transistors are available for assembly into power modules (see Fig. 1). Subsequently, n transistors are selected randomly and connected parallelly to construct a power module. The characteristics of each N transistor are represented using a device model consisting of m parameters ( $p = \{p_1, p_2, ..., p_m\}$ ). In other words, we are given the model parameter sets  $P = \{P_1, P_2, ..., P_N\}$ , where each parameter set contains m model parameters.

A straightforward method for determining the dominant model parameters is to employ a Monte Carlo (MC) simulation [20], [35]. The typical flow of an MC-based determination of dominant parameters is shown in Algorithm 1.

In line 1 of Algorithm 1, we first obtained the quantity  $\sigma_{E_i}^m$ using the MC simulation (MCSIM) (see Algorithm 2), where  $\sigma_{E_i}^m$  is the standard deviation of the variation of  $E_i$  obtained by the MCSIM with all the model parameters p treated as statistical parameters. The quantity  $L_{\max}$  in Algorithm 2 denotes the total number of iterations of the MCSIM circuit simulation. We used  $\sigma_{E_i}^m$  as a metric, which is employed as an accuracy reference for

| Algo | Algorithm 2: MCSIM.                                                                   |  |  |  |  |

|------|---------------------------------------------------------------------------------------|--|--|--|--|

| 1:   | function MCSIM $\boldsymbol{P}, \boldsymbol{p}_{m_{\mathrm{r}}}, n, L_{\mathrm{max}}$ |  |  |  |  |

| 2:   | set $oldsymbol{p}_{m_{\mathrm{r}}}$ as statistical parameters                         |  |  |  |  |

| 3:   | for $(L_{\text{iter}} = 0; L_{\text{iter}} < L_{\max}; L_{\text{iter}}++)$ do         |  |  |  |  |

| 4:   | select $n$ parameter sets randomly from $P_1$ to $P_N$                                |  |  |  |  |

| 5:   | assign the selected $n$ parameter sets to each                                        |  |  |  |  |

|      | transistor $Q_1$ to $Q_n$                                                             |  |  |  |  |

| 6:   | perform circuit simulation to obtain $E_i$                                            |  |  |  |  |

| 7:   | end for                                                                               |  |  |  |  |

| 8:   | calculate $\sigma_{E_i}^{m_r}$                                                        |  |  |  |  |

| 9:   | return $\sigma_{E_i}^{m_{ m r}^{-i}}$                                                 |  |  |  |  |

| 10:  | end function                                                                          |  |  |  |  |

the next step. In line 4 of Algorithm 1, we selected  $m_r$  (< m) parameters (the set  $p_{m_r}$ ) from p as statistical parameters and performed the MCSIM again under conditions where only the chosen  $m_r$  parameters vary. Notably, the values of the model parameters not selected as statistical variables are fixed at their respective nominal values. Using the MCSIM, we obtained the standard deviation  $\sigma_{E_i}^{m_r}$  when only  $p_{m_r}$  is varied. In line 5 of Algorithm 1, the error associated with this limited set of statistical model parameters is calculated as follows:

$$err_{\sigma} \sigma_{E_{i}} = \frac{|\sigma_{E_{i}}^{m} - \sigma_{E_{i}}^{m_{r}}|}{\sigma_{E_{i}}^{m}} \times 100 \,[\%].$$

(1)

If the estimated error is small, the selected parameter set  $p_{m_r}$  can represent the total variation and be used as the set of dominant model parameters ( $p_{\text{dominant}}$ ). For all the ways to choose  $m_r$ from m, we repeated the above error calculation in lines 3–6 of Algorithm 1. Overall,  $\sum_{m_r=1}^{m-1} {m \choose m_r}$  possible candidates exist for the set of dominant model parameters. Accordingly, we repeated the error estimation in lines 2–7 exhaustively. As the final step, in line 8 of Algorithm 1, we selected as  $p_{\text{dominant}}$  the set  $p_{m_r}$ with the smallest number of parameters yielding an error lower than the acceptable error threshold  $err_{\text{accept}}$ . For example, the value of  $err_{\text{accept}}$  may be set at 10%.

Unfortunately, the MC-based method described above for determining the dominant parameters requires a long computational time. Lines 2–7 of Algorithm 1, where the estimated errors are evaluated for all the parameter combinations, are the most time-consuming steps. An increase in the considered model parameters increases the execution time exponentially. The time  $T_{\rm conv}$  required to compute the process described above can be estimated as follows:

$$T_{\rm conv} = T_{\rm MC} \cdot \sum_{m_{\rm r}=1}^{m-1} \binom{m}{m_{\rm r}}$$

(2)

where  $T_{\rm MC}$  denotes the computation time for the MCSIM to evaluate the estimated error for a given parameter combination. The value of  $T_{\rm MC}$  typically requires, at least, several minutes because the transient simulation is repeated many times ( $L_{\rm max}$ ), drawing random samples for the model parameters for each combination of model parameter sets to obtain a statistically significant estimate of  $\sigma_{E_i}^{m_r}$ . The number of combinations  $\sum_{m_r=1}^{m-1} {m \choose m_r}$ increases rapidly as *m* increases, making  $T_{\rm conv}$  intractably large.

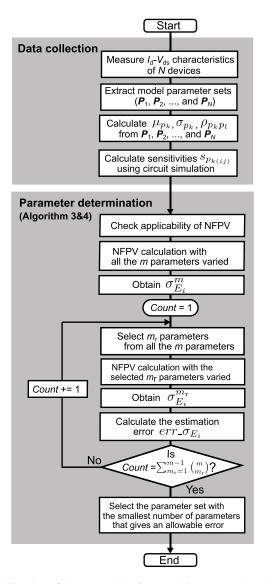

Fig. 3. Flowchart of the proposed dominant model-parameter determination.

As described above, identifying the dominant statistical model parameters has great practical value even if the determination is lengthy. Once the dominant parameter set is determined, statistical circuit simulations are significantly accelerated, allowing us to run high-accuracy simulations quickly due to the limited number of statistical model parameters. Additionally, the computational cost required to extract the statistical model parameters including the correlations between the parameters—is reduced significantly.

# III. PROPOSED METHOD FOR DETERMINING THE DOMINANT PARAMETERS

We present the flowchart of the proposed dominant model parameter determination in Fig. 3. The proposed method consists of two major steps. The first step is extracting  $\sigma_{p_k}$ ,  $\rho_{p_k p_l}$ , and  $s_{p_{k(ij)}}$  for calculating the NFPV equation. The second step is applying the NFPV equation to find the dominant model parameters efficiently. Although the basic outline of

# Algorithm 3: NFPV-Based Determination Of Dominant Parameters.

and  $s_{p_k p_l(ij)}$

| Re | quire: $P, p, n, err_{accept}$                                                               |

|----|----------------------------------------------------------------------------------------------|

| 1: | calculate $\mu_{p_k}, \sigma_{p_k}, \rho_{p_k p_l}, s_{p_k(ij)}$ , and s                     |

|    | check applicability of NFPV equation                                                         |

| 3: | $\sigma_{E_i}^m = \text{NFPV}(\boldsymbol{p}, n, \sigma_{p_k}, \rho_{p_k p_l}, s_{p_k(ij)})$ |

| 4: | for $(m_r = 1; m_r < m; m_r + +)$ do                                                         |

| 5: | for each $\boldsymbol{p}_m \in \boldsymbol{p}$ do                                            |

- 6:  $\sigma_{E_i}^{m_r} = \text{NFPV}(\boldsymbol{p}_{m_r}, n, \sigma_{p_k}, \rho_{p_k p_l}, s_{p_k(ij)})$

- 7: calculate  $err\_\sigma_{E_i}$

- 8: end for

- 9: end for

- 10: select  $p_{m_r}$  with the smallest  $m_r$ , giving  $err\_\sigma_{E_i}$ within  $err_{\text{accept}}$  as  $p_{\text{dominant}}$

- 11: return  $p_{\text{dominant}}$

#### Algorithm 4: NFPV Equation.

| 1:  | function NFPV $p_{m_r}$ , $n$ , $\sigma_{p_k}$ , $\rho_{p_k p_l}$ , $s_{p_k(ij)}$                              |

|-----|----------------------------------------------------------------------------------------------------------------|

| 2:  | initialize $\sigma_{E_i}^{m_r} = 0$                                                                            |

| 3:  | for $(j = 1; j \le n; j++)$ do                                                                                 |

| 4:  | for $(l=1; l \leq m_{\mathrm{r}}; l++)$ do                                                                     |

| 5:  | for $(k = 1; k \le m_{\mathrm{r}}; k++)$ do                                                                    |

| 6:  | $\sigma_{E_i}^{m_{\mathrm{r}}} + = s_{p_k(ij)} s_{p_l(ij)} \rho_{p_k p_l} \sigma_{p_{k(j)}} \sigma_{p_{l(j)}}$ |

| 7:  | end for                                                                                                        |

| 8:  | end for                                                                                                        |

| 9:  | end for                                                                                                        |

| 10: | return $\sigma_{E_i}^{m_r}$                                                                                    |

| 11: | end function                                                                                                   |

the proposed procedure is similar to that of the conventional MC-based method, we employed the NFPV equation in Algorithms 3 and 4 to accelerate the computation. The NFPV equation allows time-consuming transient circuit simulations to be replaced by the evaluation of the analytical equation, enabling quick evaluation of the variance in energy loss for each model parameter combination. Subsequently, we derive the NFPV equation in Section III-A, which is imperative in the proposed method, by accelerating the evaluation of the variance for each parameter combination. We then present the detailed procedure of the proposed method in Section III-B.

#### A. Derivation of the NFPV Equation

We first derived the energy loss variation  $\Delta E_i$  in the *i*th transistor among *n*-paralleled transistors. We defined  $\Delta E_i$  as the difference in the nominal energy loss  $\mu_{E_i}$ , which would be achieved if all the model parameters of the paralleled transistors were equal. Suppose *n*-paralleled devices are chosen randomly from many transistors. As defined in Section II, the characteristics of each transistor are represented using a device model comprising *m* model parameters, although the proposed method can be applied to any device model with any number of parameters.

Using a Taylor-series expansion, we obtained the energy loss variation of the *i*th transistor from small perturbations of the

model parameters as follows:

$$\Delta E_{i} = \frac{1}{1!} \left( \sum_{j=1}^{n} \sum_{k=1}^{m} s_{p_{k}(ij)} \Delta p_{k(j)} \right) + \frac{1}{2!} \left( \sum_{j=1}^{n} \sum_{k=1}^{m} \sum_{l=1}^{m} s_{p_{k}p_{l}(ij)} \Delta p_{k(j)} \Delta p_{l(j)} \right) + \cdots$$

(3)

Here,  $p_{k(j)}$  and  $p_{l(j)}$  denote the kth and lth model parameters of transistor  $Q_j$  (k, l = 1, 2, ..., m and j = 1, 2, ..., n). The quantities  $s_{p_{k(ij)}}$  and  $s_{p_k p_{l(ij)}}$  are the first- and second-order coefficients, or sensitivities, defined as:

$$s_{p_{k(ij)}} = \frac{\partial E_i}{\partial p_{k(j)}}$$

and (4)

$$s_{p_k p_{l(ij)}} = \frac{\partial^2 E_i}{\partial p_{k(j)} \partial p_{l(j)}}.$$

(5)

When  $i \neq j$ ,  $s_{p_{k(ij)}}$  and  $s_{p_k p_{l(ij)}}$  are the sensitivities across different devices,  $Q_i$  and  $Q_j$ , that is, they are cross sensitivities between the paralleled devices. Using (3) and truncating secondand higher order terms, we obtained the variance of  $E_i$ , denoted by  $\sigma_{E_i}^2$ , as:

$$\sigma_{E_i}^2 = V[E_i] = E[(\Delta E_i)^2]$$

$$= E\left[\left(\sum_{j=1}^n \sum_{k=1}^m s_{k(ij)} \Delta p_{k(j)}\right)^2\right]$$

(6)

where  $V[\cdot]$  and  $E[\cdot]$ , respectively, represent the variance and the expectation of their arguments. Expanding (6), we obtained the following equations:

$$\sigma_{E_i}^2 = E\left[\sum_{j'=1}^n \sum_{j=1}^n \sum_{k=1}^m \sum_{l=1}^m s_{k(ij')} s_{l(ij)} \Delta p_{k(j')} \Delta p_{l(j)}\right]$$

(7)

$$= \sum_{j'=1}^{n} \sum_{j=1}^{n} \sum_{k=1}^{m} \sum_{l=1}^{m} s_{k(ij')} s_{l(ij)} \text{Cov}\left[p_{k(j')}, p_{l(j)}\right].$$

(8)

Here,  $\operatorname{Cov}[p_{k(j')}, p_{l(j)}]$  denotes the covariance between  $p_{k(j')}$ and  $p_{l(j)}$ . When  $j \neq j'$ , the term  $\operatorname{Cov}[p_{k(j')}, p_{l(j)}]$  is the covariance of the model parameters between the different transistors  $Q_j$  and  $Q_{j'}$  in a power module. Based on the assumption that  $Q_j$  and  $Q_{j'}$  are randomly sampled, there is no correlation between  $p_{k(j')}$  and  $p_{l(j)}$ . Conversely,  $\operatorname{Cov}[p_{k(j')}, p_{l(j)}]$  is zero when  $j \neq j'$ . Therefore, we can simplify (8) to

$$\sigma_{E_i}^2 = \sum_{j=1}^n \sum_{k=1}^m \sum_{l=1}^m s_{k(ij)} s_{l(ij)} \text{Cov}\left[p_{k(j)}, p_{l(j)}\right].$$

(9)

The term  $\text{Cov}[p_{k(j)}, p_{l(j)}]$  is represented using the standard deviation of each model parameter  $(\sigma_{p_{k(j)}}, \sigma_{p_{l(j)}})$ , and the correlation coefficient  $\rho_{p_{k(j)}p_{l(j)}}$  between the model parameters

$$Cov[p_{k(j)}, p_{l(j)}] = \rho_{p_{k(j)}p_{l(j)}}\sigma_{p_{k(j)}}\sigma_{p_{l(j)}}.$$

(10)

Therefore, (9) can be rewritten as

$$\sigma_{E_i}^2 = \sum_{j=1}^n \sum_{k=1}^m \sum_{l=1}^m s_{k(ij)} s_{l(ij)} \rho_{p_{k(j)}p_{l(j)}} \sigma_{p_{k(j)}} \sigma_{p_{l(j)}}.$$

(11)

Finally, since the standard deviations and the correlation coefficient are independent of the device number j, (11) can further be simplified to

$$\sigma_{E_i}^2 = \sum_{j=1}^n \sum_{k=1}^m \sum_{l=1}^m s_{p_{k(ij)}} s_{p_{l(ij)}} \rho_{p_k p_l} \sigma_{p_k} \sigma_{p_l}.$$

(12)

When j = i, the terms on the right-hand side represent the parameter variations of  $Q_i$ . Alternatively, when  $j \neq i$ , these terms represent the contributions from the parameter variations of another device  $Q_j$  to  $\Delta E_i$ . When n = 1, (12) is termed the FPV, which has been proposed for analyzing process variations of CMOS devices [32], [33]. The FPV cannot consider the interactions among paralleled transistors and, thus, cannot be used to analyze the current imbalance described in Section II-A. To analyze the current imbalance for power transistors, we have extended the concept of the FPV to *n*-paralleled devices. In the extension, we introduced the correlation coefficient  $\rho_{p_k p_l}$  to analyze the interactions among paralleled devices. We refer to (12) as the NFPV equation.

The advantages of the NFPV equation are its computational efficiency and wide applicability. Using the NFPV equation,  $\sigma_{E_i}^2$  can be calculated as the sum of contributions from each model parameter, including interactions among the *n*-paralleled devices. The NFPV equation can be substituted for the MCSIM— which requires numerous transient circuit simulations to obtain the energy loss variance—allowing for an exhaustive search for the dominant model parameters.

Although we used energy loss as a metric for evaluating the current imbalance, the derivation of the NFPV equation is quite general. Therefore, this equation can be applied directly, without modification, for other characteristics, such as the turn-ON or turn-OFF switching time, the surge voltage  $V_{\rm ds}$ , and the peak reverse recovery current. Moreover, we can apply this equation to various device models with different model parameters and circuit topologies.

# *B. Proposed Procedure for Determining the Dominant Parameters*

To apply the proposed NFPV equation to determine the dominant parameters, the contributions of the second-order components in (3) must be sufficiently small compared to the first-order components. Therefore, as the first step of the proposed NFPV-based method in Algorithm 3, we compared them and verified that this condition holds. In line 1 of Algorithm 3, we first extracted the mean  $\mu_{pk}$  and standard deviation  $\sigma_{pk}$  of each model parameter. Additionally, we extracted the correlation coefficients  $\rho_{pkpl}$  between the model parameters from the model parameter sets P. Subsequently, we ran a circuit simulation for the target circuit—such as that shown in Fig. 2—to obtain the values of  $s_{pk(ij)}$  and  $s_{pkpl}(ij)$  for all the model parameters of all the paralleled devices (k, l = 1, 2, ..., m; i, j = 1, 2, ..., n).

Specifically, we calculated the change in  $E_i$  using circuit simulations with fluctuations of  $p_{k(j)}$  and  $p_{l(j)}$  about their mean values  $\mu_{p_k}$  and  $\mu_{p_l}$ . The model parameters other than  $p_k$  and  $p_l$  are assigned their nominal values. The sensitivities  $s_{p_k(ij)}$  and  $s_{p_kp_l(ij)}$ , respectively, are then obtained using the following numerical differentiations:

$$s_{p_{k(ij)}} = \frac{E_i(\mu_{p_{k(j)}} + \Delta p_{k(j)})}{2\Delta p_{k(j)}} - \frac{E_i(\mu_{p_{k(j)}} - \Delta p_{k(j)})}{2\Delta p_{k(j)}}$$

(13)

$$s_{p_k p_l(ij)} = \frac{E_i(\mu_{p_k(j)} + \Delta p_{k(j)}, \mu_{p_l(j)} + \Delta p_{l(j)})}{4\Delta p_{k(j)}\Delta p_{l(j)}} - \frac{E_i(\mu_{p_k(j)} - \Delta p_{k(j)}, \mu_{p_l(j)} + \Delta p_{l(j)})}{4\Delta p_{k(j)}\Delta p_{l(j)}} - \frac{E_i(\mu_{p_k(j)} + \Delta p_{k(j)}, \mu_{p_l(j)} - \Delta p_{l(j)})}{4\Delta p_{k(j)}\Delta p_{l(j)}} + \frac{E_i(\mu_{p_k(j)} - \Delta p_{k(j)}, \mu_{p_l(j)} - \Delta p_{l(j)})}{4\Delta p_{k(j)}\Delta p_{l(j)}}$$

(14)

where  $\Delta p_{k(j)}$  and  $\Delta p_{l(j)}$  are the perturbations of  $p_{k(j)}$  and  $p_{l(j)}$ , respectively, from their nominal values. Since there are n paralleled devices and m model parameters, the total number of sensitivities to be calculated are nm for  $s_{p_{k(ij)}}$  and  $nm^2$  for  $s_{p_kp_l(ij)}$ . Using the extracted sensitivities, the firstand second-order components are calculated as  $s_{p_k(j)}\sigma_{p_k}$  and  $s_{p_kp_l(ij)}\sigma_{p_k}\sigma_{p_l}$ , respectively. After confirming that the absolute values of the second-order components are negligibly small compared to the first-order components in line 2 of Algorithm 3, we proceeded to the next step.

Lines 3–10 of Algorithm 3 are almost identical to the conventional MC-based method, except that we used the NFPV equation instead of the MCSIM. In line 3 of Algorithm 3, we obtained  $\sigma_{E_i}^m$  using the NFPV equation in Algorithm 4, considering the variations of all m model parameters. We used  $\sigma_{E_i}^m$  as an accuracy reference for the next step. In lines 4–9 of Algorithm 3, we evaluated  $err_{-}\sigma_{E_i}$  exhaustively for all combinations of  $p_{m_r}$  to find the set of dominant model parameters. In line 10, we selected as  $p_{\text{dominant}}$  the set  $p_{m_r}$  with the smallest  $m_r$  that gives  $err_{-}\sigma_{E_i}$  within the acceptable error threshold  $err_{\text{accept}}$ . We then used a model where only the dominant model parameters so determined are treated as statistical variables rather than considering all the model parameters as statistical variables.

We summarize the parameters required by the proposed method in Algorithms 3 and 4. The summary statistics,  $\mu_{p_k}$ ,  $\sigma_{p_k}$ ,  $\rho_{p_k p_l}$ , are the values calculated from the model parameter set P. Model parameters p and the number of model parameters m are determined by the device model.  $s_{p_k(ij)}$  and  $s_{p_k p_l(ij)}$  are calculated by (13) and (14). In these equations, the perturbation parameters,  $\Delta p_{k(j)}$  and  $\Delta p_{l(j)}$ , are typically 1% of  $\mu_{p_k(j)}$  and  $\mu_{p_l(j)}$ . Finally,  $err_{\text{accept}}$  determines the accuracy of the proposed method. We use a 10% accuracy as a typical value, but smaller values, such as 5% or 3%, may be used to attain higher accuracy.

TABLE I MODEL PARAMETERS FOR THE DRAIN CURRENT EQUATION IN THE SPICE LEVEL-1-BASED SILICON MOSFET MODEL

| Parameter | Description                                          |  |  |

|-----------|------------------------------------------------------|--|--|

| VTH       | Gate threshold voltage [V]                           |  |  |

| K         | Current gain factor [A/V]                            |  |  |

| RD        | Parasitic resistance at the drain side $[m\Omega]$   |  |  |

| LAMBDA    | Channel length modulation [1/V]                      |  |  |

| THETA     | Channel mobility degradation [1/V]                   |  |  |

| ALPHA     | Starting voltage of channel mobility degradation [V] |  |  |

The total calculation time  $T_{\text{prop}}$  of the proposed method based on the NFPV equation is

$$T_{\rm prop} = T_{\rm NFPV} \cdot \sum_{m_{\rm r}=1}^{m-1} \binom{m}{m_{\rm r}} + T_{\rm sens}$$

(15)

$$T_{\rm sens} = T_{\rm cir} \cdot (2\,nm + 4\,nm^2). \tag{16}$$

Here,  $T_{\rm NFPV}$  denotes the time required to evaluate the NFPV equation as shown in Algorithm 4.  $T_{\rm sens}$  is the calculation time for the first- and second-order sensitivities of all the paralleled devices and model parameters.  $T_{\rm cir}$  is the time for one circuit simulation, and  $(2 nm + 4 nm^2)$  is the total number of circuit simulations required to determine all the first- and second-order sensitivities using (13) and (14). Although  $T_{\rm prop}$  contains the additional term  $T_{\rm sens}$ , the value of  $T_{\rm prop}$  can be smaller than  $T_{\rm conv}$  given by (2) because  $T_{\rm NFPV}$  is only a few milliseconds, while  $T_{\rm MC}$  in (2) is at least several minutes.

#### IV. EXPERIMENTAL VALIDATION

To validate the effectiveness and generality of the proposed method, we applied the proposed procedure to actual transistors with different numbers of paralleled devices. We used commercially available 100 Si MOSFETs and 300 SiC MOSFETs as the population for paralleled devices. We used a SPICE Level-1-based model [20], [34] as the Si MOSFET model and a surface-potentialbased model [28] as the SiC MOSFET model. We implemented the device models in the Verilog-A language. We used a commercial circuit simulator [36] to perform the validation and implemented both the conventional and the proposed methods in the Python programming language. We determined the dominant parameters on a Linux PC with an Intel(R) Core(TM) i9-7980XE CPU running at 2.60 GHz and a 128 GB random access memory, using a single thread.

# A. Device Model

1) Si MOSFET: Table I presents the drain current equation of the Si MOSFET model. Hereafter, we represent the model parameters in boldface. This model is a threshold-voltage-based model comprising three equations representing the cutoff, linear, and saturation regions. The drain current  $I_d$  is represented as function of the gate-source voltage  $V_{gs}$  and  $V_{ds}$  as follows:

$$V_{\rm ds,int} = V_{\rm ds} - \mathbf{R}\mathbf{D} \cdot I_{\rm d} \tag{17}$$

$$I_{\rm d} = \mathbf{K} \cdot \frac{1 + \mathbf{LAMBDA} \cdot V_{\rm ds,int}}{1 + \mathbf{THETA} \cdot V_{\rm gs}} \cdot I_{\rm DD}$$

(18)

TABLE II MAJOR MODEL PARAMETERS FOR THE DRAIN CURRENT EQUATION IN THE SURFACE-POTENTIAL-BASED SIC MOSFET MODEL [28]

| Parameter | Description                                          |  |  |

|-----------|------------------------------------------------------|--|--|

| TOX       | Oxide thickness [nm]                                 |  |  |

| VFBC      | Flat-band voltage of the channel region [V]          |  |  |

| NA        | Acceptor concentration $[cm^{-3}]$                   |  |  |

| K         | Current gain factor [-]                              |  |  |

| RD        | Parasitic resistance at the drain side $[m\Omega]$   |  |  |

| LAMBDA    | Channel length modulation [1/V]                      |  |  |

| THETA     | Channel mobility degradation [1/V]                   |  |  |

| ALPHA     | Starting voltage of channel mobility degradation [V] |  |  |

| DELTA     | Smoothing parameter for gradual transition           |  |  |

|           | between the linear and saturation regions [-]        |  |  |

$$I_{\rm DD} = \begin{cases} 0, \quad (\text{cutoff region} : V_{\rm gs} \leq \mathbf{VTH}) \\ \mathbf{K} \cdot \left\{ (V_{\rm gs} - \mathbf{VTH}) \cdot V_{\rm ds,int} - \frac{1}{2} \cdot V_{\rm ds,int}^2 \right\} \\ (\text{linear region} : V_{\rm ds,int} < V_{\rm gs} - \mathbf{VTH}) \\ \frac{1}{2} \cdot \mathbf{K} \cdot (V_{\rm gs} - \mathbf{VTH})^2 \\ .(\text{saturation region} : V_{\rm ds,int} \geq V_{\rm gs} - \mathbf{VTH}) \end{cases}$$

(19)

Here, **VTH** and **K** are the gate threshold voltage and current gain factor, which are basic parameters for the SPICE Level-1-based model. The parasitic resistance **RD** of the drain electrode is considered in (17). The channel length modulation is incorporated in (18) using **LAMBDA**, and mobility degradation is represented by **THETA** and **ALPHA**.

2) SiC MOSFET: Table II lists the major parameters of the SiC MOSFET model for the drain current equation. In the drain current model, the surface potentials at the source and drain ends of a SiC channel MOSFET,  $\phi_{sS}$  and  $\phi_{sD}$ , are computed by solving a nonlinear equation for the gate–source voltage  $V_{gs}$  and the drain–source voltage  $V_{ds}$ . The  $I_d$  can be computed from  $\phi_{sS}$  and  $\phi_{sD}$  as follows:

$$V_{\rm ds,int} = V_{\rm ds} - \mathbf{R}\mathbf{D} \cdot I_{\rm d} \tag{20}$$

$$I_{\rm d} = \mathbf{K} \cdot \frac{1 + \mathbf{LAMBDA} \cdot V_{\rm ds,int}}{1 + \mathbf{THETA} \cdot V_{\rm gs}} \cdot I_{\rm DD}$$

(21)

$$I_{\rm DD} = C_{\rm ox} (V_{\rm gs} - \mathbf{VFBC} + \phi_{\rm t}) (\phi_{\rm sD} - \phi_{\rm sS}) - \frac{1}{2} C_{\rm ox} (\phi_{\rm sD}^2 - \phi_{\rm sS}^2) - \frac{2}{3} \phi_{\rm t} \gamma \left\{ \left( \frac{\phi_{\rm sD}}{\phi_{\rm t}} - 1 \right)^{3/2} - \left( \frac{\phi_{\rm sS}}{\phi_{\rm t}} - 1 \right)^{3/2} \right\} + \phi_{\rm t} \gamma \left\{ \left( \frac{\phi_{\rm sD}}{\phi_{\rm t}} - 1 \right)^{3/2} - \left( \frac{\phi_{\rm sS}}{\phi_{\rm t}} - 1 \right)^{3/2} \right\}$$

(22)

$$C_{\rm ox} = \varepsilon_{\rm ox} / {\rm TOX}$$

<sup>(23)</sup>

$$\gamma = \sqrt{2\varepsilon_{\rm SiC}kT \cdot \mathbf{NA}} \tag{24}$$

Value

298

0.026

$1.\overline{38 \times 10^{-23}}$

$9.7{\times}8.85{\times}10^{-12}$ Permittivity of SiC [F/m]  $3.9 \times 8.85 \times 10^{-12}$ Permittivity of gate oxide [F/m] 20 V<sub>gs</sub> = 10 V V<sub>gs</sub> = 7 V 15 V<sub>gs</sub> = 6.5 V ≤ 10  $V_{qs} = 6 V$ V<sub>qs</sub> = 5.5 V  $V_{\rm gs}$  = 5 V V<sub>gs</sub> = 4.5 V 10 15  $\overline{20}$ *V*<sub>ds</sub> [V]

TABLE III Physical Constants

Boltzmann's constant [J/K]

Thermal voltage (kT/q) [V]

Absolute temperature [K]

Parameter

k

T

$\phi_t$

$\varepsilon_{\rm SiC}$

$\varepsilon_{\rm ox}$

Description

Fig. 4. Measured  $I_d - V_{ds}$  characteristics of the 100 Si MOSFETs at  $T_a = 25 \text{ °C}$ .

where k, T,  $\phi_t$ ,  $\varepsilon_{SiC}$ , and  $\varepsilon_{ox}$  are Boltzmann's constant, the absolute temperature, the thermal voltage, and the permittivities of SiC and the oxide, respectively. The values of these physical constants are listed in Table III. Here, **VFBC**, **TOX**, and **NA** are the flat-band voltage of the channel region, the thickness of the gate oxide, and the acceptor concentration, respectively. As with the Si MOSFET model, the parameters **K**, **RD**, **LAMBDA**, **THETA**, and **ALPHA** are incorporated in (20) and (21). Furthermore, to provide a smooth transition between the linear and saturation regions of the device model, **DELTA** is introduced as a parameter to compensate for mismatches between the pinch-off voltages of the measurement and the simulation.

The temperature dependence of the transistor characteristics can significantly affect the current imbalance. Using the SiC MOSFETs model, we confirmed that the dominant model parameters determined by the proposed method are valid even when considering the temperature dependence. The following model parameters are made to have a linear temperature dependence [28]:

$$\mathbf{VFBC} = \mathbf{VFBC0} + \mathbf{VFBCS} \cdot (T - T_{\text{ref}})$$

(25)

$$\mathbf{K} = \mathbf{K}\mathbf{0} + \mathbf{K}\mathbf{S} \cdot (T - T_{\text{ref}}) \tag{26}$$

$$\mathbf{RD} = \mathbf{RD0} + \mathbf{RDS} \cdot (T - T_{\text{ref}})$$

(27)

**THETA** = **THETA0** + **THETAS**

$$\cdot$$

( $T - T_{ref}$ ). (28)

Here, VFBC0, K0, RD0, and THETA0 are the parameters at the reference temperature  $T_{ref}$ , set to 25 °C. Furthermore, VFBCS, KS, RDS, and THETAS are the temperature sensitivities of the parameters.

#### B. Parameter Determination Setup

٦

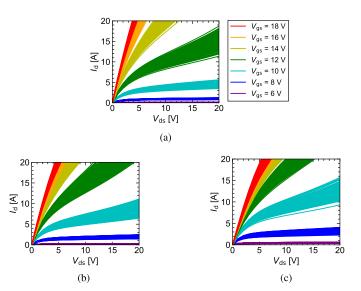

Figs. 4 and 5 show the measured  $I_{\rm d}-V_{\rm ds}$  characteristics of the 100 Si MOSFETs at an ambient temperature ( $T_{\rm a}$ ) of 25 °C and 300 SiC MOSFETs at different temperature conditions ( $T_{\rm a} = 25$ , 75, 125 °C).

Using the Si and SiC MOSFET models, we extracted the parameter sets  $P = \{P_1, P_2, \dots, P_{100}\}$  for Si MOSFETs, and

Fig. 5. Measured  $I_{\rm d}$ - $V_{\rm ds}$  characteristics of the 300 SiC MOSFETs at different temperature conditions. (a)  $T_{\rm a} = 25$  °C. (b)  $T_{\rm a} = 75$  °C. (c)  $T_{\rm a} = 125$  °C.

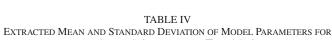

THE SI AND SIC MOSFETS AT  $T_{a} = 25 \text{ °C}$  (a) Si MOSFETS  $p_{k} \qquad \mu_{p_{k}} \qquad \sigma_{p_{k}}$

| $p_k$                 | $\mu_{p_k}$            | $\sigma_{p_k}$        |  |  |  |  |

|-----------------------|------------------------|-----------------------|--|--|--|--|

| VTH [V]               | $4.08 \times 10^{17}$  | $1.47 \times 10^{-2}$ |  |  |  |  |

| <b>K</b> [A/V]        | 7.04                   | 0.309                 |  |  |  |  |

| <b>RD</b> $[m\Omega]$ | $4.65 \times 10^{2}$   | 16.9                  |  |  |  |  |

| LAMBDA [1/V]          | $3.38 \times 10^{-3}$  | $3.54 \times 10^{-4}$ |  |  |  |  |

| <b>THETA</b> [1/V]    | $1.87 \times 10^{-3}$  | $1.89 \times 10^{-4}$ |  |  |  |  |

| ALPHA [V]             | 4.85                   | 0.521                 |  |  |  |  |

|                       |                        |                       |  |  |  |  |

| (0) \                 | (b) SiC MOSFETS        |                       |  |  |  |  |

| $p_k$                 | $\frac{\mu_{p_k}}{50}$ | $\sigma_{p_k}$        |  |  |  |  |

| TOX [nm]              | 50                     | 0                     |  |  |  |  |

| VFBC [V]              | -0.43                  | $7.28 \times 10^{-2}$ |  |  |  |  |

| NA $[cm^{-3}]$        | $1.18 \times 10^{17}$  | $2.23 \times 10^{15}$ |  |  |  |  |

| K [-]                 | $2.88 \times 10^5$     | $1.02 \times 10^{4}$  |  |  |  |  |

| <b>RD</b> $[m\Omega]$ | 1.13                   | 0.564                 |  |  |  |  |

| LAMBDA [1/V]          | $9.22 \times 10^{-2}$  | $2.01 \times 10^{-3}$ |  |  |  |  |

| <b>THETA</b> [1/V]    | $3.04 \times 10^{-2}$  | $1.74 \times 10^{-3}$ |  |  |  |  |

| ALPHA [V]             | 15.1                   | 0.189                 |  |  |  |  |

| DELTA [-]             | 0.596                  | $9.69 \times 10^{-3}$ |  |  |  |  |

$P = \{P_1, P_2, \dots, P_{300}\}$  for SiC MOSFETs from the measured  $I_d-V_{ds}$  characteristics, where N = 100 and 300 for Si and SiC MOSFETs, respectively.

The parameter set  $P_i$  (i = 1, 2, ..., N) for each model comprises the parameters listed in Tables I and II. Following [37], we first extracted initial values for the model parameters and obtained each set of model parameters using simulated annealing (SA) [38]. The root-mean-square error (RMSE) between the measured and simulated  $I_d$  values was minimized at all  $V_{gs}$  and  $V_{ds}$  bias points. The average RMSEs for the 100 Si MOSFETs and 300 SiC MOSFETs at 25 °C were 0.83 A and 0.21 A, respectively.

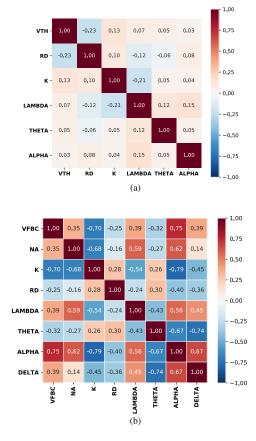

Table IV and Fig. 6 show the  $\mu_{p_k}$ ,  $\sigma_{p_k}$ , and  $\rho_{p_k p_l}$  calculated from the extracted model parameter sets for the Si and SiC MOS-FETs at  $T_a = 25$  °C. For the Si MOSFETs, the number of statistical model parameter candidates in this experiment is m = 6, that

Fig. 6. Correlation coefficient matrix  $\rho_{p_k p_l}$  extracted from the measured  $I_d-V_{ds}$  characteristics. (a) Si MOSFETS. (b) SiC MOSFETS.

is,  $p = \{VTH, K, RD, LAMBDA, THETA, ALPHA\}$ . For the SiC MOSFETs, we assumed TOX to be a constant. Therefore, the number of statistical model parameter candidates is m = 8, that is,  $p = \{VFBC, NA, K, RD, LAMBDA, THETA, ALPHA, DELTA\}$ . Using the extracted parameters in Table IV, the values of  $s_{p_{k(ij)}}$  and  $s_{p_kp_l(ij)}$  for all the model parameters of all the paralleled devices can be calculated for different numbers of paralleled devices.

We used the inductive load switching circuit in Fig. 2 to obtain  $E_i$ , which is calculated as follows:

$$E_{i} = \int_{t_{\text{on_ini}}}^{t_{\text{on_ini}}} I_{\text{d}i}(t) \cdot V_{\text{d}si}(t) \, \mathrm{d}t + \int_{t_{\text{off_ini}}}^{t_{\text{off_ini}}} I_{\text{d}i}(t) \cdot V_{\text{d}si}(t) \, \mathrm{d}t$$

(29)

where  $I_{di}(t)$  and  $V_{dsi}(t)$ , respectively, represent the drain current waveform and the drain-source voltage waveform of  $Q_i$ . In (29),  $t_{on_{ini}}$  is the time when  $V_{gsi}$  changes to 10% of its final value, where  $V_{gsi}$  is the gate-source voltage waveform of  $Q_i$ , and  $t_{on_{fin}}$  is the time  $V_{dsi}$  drops to 10% of its initial value. Similarly,  $t_{off_{ini}}$  denotes the time  $V_{gsi}$  decreases to 90% of its ON-state value, while  $t_{off_{fin}}$  is the instant at which  $V_{dsi}$  increases to 90% of its OFF-state value. Using (13) and (14), we extracted the sensitivities  $s_{p_{k(ij)}}$  and  $s_{p_k p_l(ij)}$  for all the model parameters of the paralleled devices. The values of the circuit elements are summarized in Table V. When determining the dominant model parameters, we assume all the parasitic inductances in Fig. 2

TABLE V CIRCUIT SIMULATION SETTINGS

| Parameter                                        | Value                  |

|--------------------------------------------------|------------------------|

| Paralleled devices (n)                           | 2, 4,, 10 [pcs]        |

| Power supply voltage $(V_{dd})$                  | 600 [V]                |

| Load current $(I_{\rm L})$                       | $10 \cdot n  [A]$      |

| Inductive load $(L)$                             | 1.0 [mH]               |

| Parasitic inductances $(L_{gi}, L_{di}, L_{si})$ | 5.0 [nH]               |

| Gate resistance $(R_g)$                          | 94 / n [Ω]             |

| Gate drive voltage (Si)                          | ON: 10 [V], OFF: 0 [V] |

| Gate drive voltage (SiC)                         | ON: 18 [V], OFF: 0 [V] |

TABLE VI CALCULATED FIRST-ORDER COMPONENTS

|        | $[\mu J]$ |

|--------|-----------|

| VFBC   | -49.3     |

| NA     | -31.6     |

| K      | 15.7      |

| RD     | -0.122    |

| LAMBDA | 8.68      |

| THETA  | -0.173    |

| ALPHA  | 0.176     |

| DELTA  | 0.134     |

TABLE VII CALCULATED SECOND-ORDER COMPONENTS

| [µJ]   | VFBC   | NA     | K      | RD     | LAMBDA | THETA  | АНРНА  | DELTA  |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| VFBC   | -0.013 |        |        |        |        |        |        |        |

| NA     | -0.028 | 0.064  |        |        |        |        |        |        |

| K      | 0.015  | -0.053 | -0.042 |        |        |        |        |        |

| RD     | -0.061 | 0.081  | -0.013 | 0.022  |        |        |        |        |

| LAMBDA | 0.012  | 0.000  | -0.073 | -0.036 | -0.010 |        |        |        |

| THETA  | -0.002 | 0.000  | -0.001 | -0.001 | 0.004  | -0.007 |        |        |

| ALPHA  | -0.024 | 0.012  | -0.012 | -0.004 | 0.077  | 0.000  | -0.024 |        |

| DELTA  | 0.030  | 0.000  | 0.034  | 0.029  | -0.041 | 0.030  | -0.017 | -0.011 |

equal to a nominal value

$$L_{gi} = L_{di} = L_{si} = 5.0 \text{ nH} \ (i = 1, \dots, n).$$

(30)

In extracting the sensitivity parameters, we increased  $I_{\rm L}$  in proportion to n so that the current through each MOSFET ideally becomes 10 A. The value of  $R_{\rm g}$  was set to decrease as n increases so that the switching speed of the paralleled devices is almost constant regardless of n. We used 1.0% of the average values listed in Table IV as perturbations in extracting  $s_{p_k p_l(ij)}$  and  $s_{p_k p_l(ij)}$ . In the experimental validation, we set the acceptable error threshold to  $err_{\rm accept} = 10\%$ .

# C. Results and Discussion

1) Applicability of the Proposed Method: Tables VI and VII list the calculated first- and second-order components for each model parameter of the SiC MOSFETs. We calculated the components for n = 2 and j = i. The absolute values of the second-order components in Table VII are significantly smaller than those of the first-order components in Table VI. By varying n from 4 to 10 with j = i and  $j \neq i$ , we confirmed that the second-order components could be ignored, irrespective of the number of paralleled devices. Therefore, we confirmed that

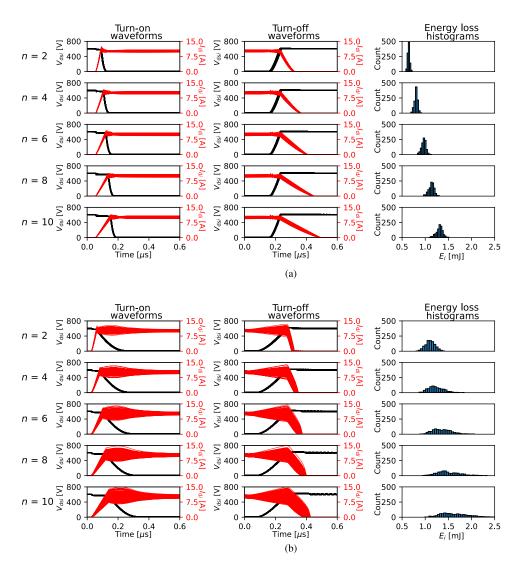

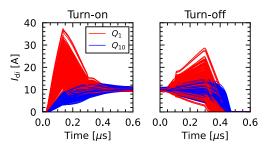

Fig. 7. Simulated  $V_{dsi}$  and  $I_{di}$  waveforms and the energy-loss variation of  $Q_i$  of the Si and SiC MOSFETs at  $T_a = 25$  °C obtained from the MCSIM with different numbers n of paralleled devices. We set  $L_{max} = 1000$  for the MCSIM. An increase in the number of paralleled devices enhances the current imbalance and energy-loss variation. (a) Si MOSFETs. (b) SiC MOSFETs.

the first-order approximation is valid and that the proposed NFPV-based method is applicable to the subsequent analysis. Note that the approximation is also valid for the Si MOSFETS.

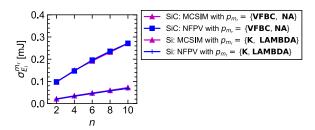

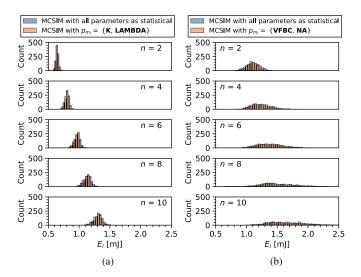

We also verified the accuracy of the NFPV equation by performing an MCSIM using the extracted Si and SiC MOSFET model parameter sets, that is,  $P = \{P_1, P_2 ..., P_{100}\}$  for the Si MOSFETs, and  $P = \{P_1, P_2 ..., P_{300}\}$  for the SiC MOSFETs. We used the circuit-component values given in Table V. Fig. 7 shows the simulated variations of  $V_{dsi}(t)$  and  $I_{di}(t)$  of the Si and SiC MOSFETs, and we obtained the histograms of  $E_i$  from the MCSIM with different numbers n of paralleled devices. Here, we used  $L_{\text{max}} = 1000$  for the MCSIM. The variations in switching waveforms and the energy loss of a MOSFET increase as *n* increases. Particularly, the current imbalance and  $E_i$  variations of the SiC MOSFETs are more significant than those of the Si MOSFETS. Fig. 8 compares the values  $\sigma_{E_i}^m$  of the Si and SiC MOSFETs obtained from the MCSIM with those obtained from the NFPV calculation. We considered all the model parameters as statistical parameters. The NFPV equation reproduced the

Fig. 8. Comparison of the standard deviation of the energy-loss variation calculated using the MCSIM and the NFPV equation. We considered all the model parameters as statistical parameters in the analyses. The NFPV equation always reproduces the MCSIM results adequately.

*n*-dependence of  $\sigma_{E_i}^m$  by the MCSIM excellently, with a maximum error of 2.5%. A possible error factor is that components above the second order are reasonably truncated in the NFPV equation because the maximum error is sufficiently small. Thus, the NFPV calculation can replace the MCSIM while maintaining the accuracy.

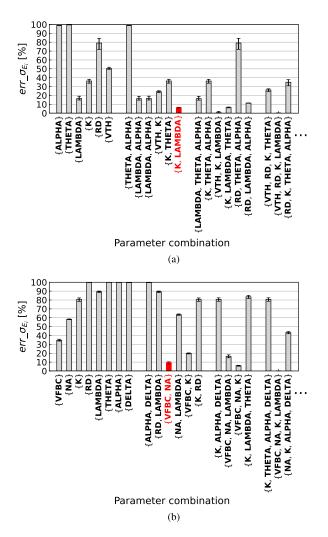

Fig. 9. Subset of the estimated error  $err_{\sigma E_i}$  for different model parameters combinations. The  $err_{\sigma E_i}$  for each model parameter combination is the average of the errors obtained when the number of paralleled devices is varied from n = 2, 4, ..., 10. The error bars above each bar graph show the range when n changes. (a) Si MOSFETS. (b) SiC MOSFETS.

2) Determination of the Dominant Parameters: Using the proposed NFPV-based method in Algorithm 3, we evaluated the estimated energy-loss error for each set of model parameters when a reduced set of model parameters is considered subject to statistical variations. Fig. 9 shows a subset of the estimated error  $err_{\sigma E_i}$  for different combinations of the Si and SiC MOSFET model parameters. Each bar graph shows the average of the errors when the number of paralleled devices is altered to 2, 4, ..., 10. Error bars on top of each bar graph indicate the range when the number of paralleled devices changes.

For the Si MOSFETs, when the number of statistical parameters  $m_r$  is 1, the smallest error of 18% was achieved when we selected **LAMBDA** as the statistical parameter. The error reduced to 6.3% with two statistical parameters {**K**, **LAMBDA**}, satisfying the target error of 10%. Hence, we selected {**K**, **LAMBDA**} as  $p_{\text{dominant}}$  for the Si MOSFETS.

For the SiC MOSFETs, when  $m_r = 1$ , the error is reduced when either {VFBC}, {NA}, {K}, or {LAMBDA} is selected as a member of the statistical parameter set  $p_{m_r}$ . However, the

Fig. 10. Comparison of the energy-loss variations obtained from the MCSIM and the NFPV calculation with  $p_{m_r} = \{K, LAMBDA\}$  for the Si MOSFETs and  $p_{m_r} = \{VFBC, NA\}$  for the SiC MOSFETs, respectively.

Fig. 11. Comparison of the energy-loss variations obtained from the MCSIM with all parameters treated as statistical parameters, the MCSIM with  $p_{m_r} = \{K, LAMBDA\}$  for the Si MOSFETS, and the MCSIM with  $p_{m_r} = \{VFBC, NA\}$  for the SiC MOSFETS, respectively. (a) Si MOSFETS. (b) SiC MOSFETS.

smallest error achievable when  $m_r = 1$  is 35%, which is not sufficiently small. When the number of the statistical parameters is increased to  $m_r = 2$ , the set {**VFBC**, **NA**} achieved a minimal error of 9.5%, which is smaller than  $err_{accept}$  we set. When the number of statistical parameters is increased further to  $m_r = 3$  or 4, either {**VFBC**, **NA**, **K**} or {**VFBC**, **NA**, **K**, **LAMBDA**} were the best combinations, with errors of 5.8% and 0.14%, respectively. When higher accuracy is required, these parameter combinations should be selected. From the dominantparameter determination flow, we selected  $p_{m_r} =$ {**VFBC**, **NA**} as  $p_{dominant}$  for the SiC MOSFETS.

We validated how accurately the selected dominant parameters simulate the energy-loss calculation. Fig. 10 shows  $\sigma_{E_i}^{m_r}$ obtained by the MCSIM and the NFPV calculation with  $p_{m_r} =$ {**K**, **LAMBDA**} for the Si MOSFETs, and  $p_{m_r} =$  {**VFBC**, **NA**} for the SiC MOSFETs, respectively. The calculated energy losses coincide closely with the NPFV calculation deviating from the MCSIM results by a maximum difference of 2.3%. Fig. 11 compares the energy-loss variations obtained from the MCSIM with all parameters treated as statistical parameters, the MCSIM with  $p_{m_r} =$  {**VFBC**, **NA**} for the Si MOSFETs, and the MCSIM with  $p_{m_r} =$  {**VFBC**, **NA**} for the SiC MOSFETs, respectively. Again, all the histograms agree very well, regardless of the

TABLE VIII EXTRACTED MEAN AND STANDARD DEVIATION OF THE TEMPERATURE-DEPENDENT MODEL PARAMETERS OF THE SIC MOSFETS

| $p_k$                | $\mu_{p_k}$            | $\sigma_{p_k}$        |

|----------------------|------------------------|-----------------------|

| VFBCS [V/°C]         | $-9.47 \times 10^{-3}$ | $1.10 \times 10^{-3}$ |

| <b>KS</b> [A/(°C·V)] | $2.13 	imes 10^3$      | $3.38 \times 10^{2}$  |

| <b>RS</b> [mΩ/ °C]   | 1.80                   | 0.130                 |

| THETAS [1/(°C·V)]    | $3.86 \times 10^{-4}$  | $6.16 \times 10^{-5}$ |

TABLE IX CONDITIONS FOR THE COMPUTATION TIME COMPARISON BETWEEN THE CONVENTIONAL AND PROPOSED METHODS

| Parameter                                   | Value                                 |

|---------------------------------------------|---------------------------------------|

| Model parameter number $(m)$                | 8 [-]                                 |

| Paralleled devices (n)                      | 10 [pcs]                              |

| Circuit simulation time $(T_{cir})$         | 5.0 [s]                               |

| Number of iterations of circuit simula-     | 100                                   |

| tion for one MCSIM $(L_{\text{max}})$       |                                       |

| Time required for one MCSIM $(T_{MC})$      | 500 [s] (= $L_{\max} \cdot T_{cir}$ ) |

| Time required for one NFPV $(T_{\rm NFPV})$ | 1.8 [ms]                              |

number of paralleled devices. We conclude that the NFPV equation accurately and efficiently identifies the dominant model parameters. With a simulation using the dominant-parameter set as statistical parameters, the energy-loss variation can be approximated accurately regardless of the number of paralleled devices.

3) Validity of Parameter Determination Under Realistic Conditions: We verified that the dominant model parameters determined by the proposed method are valid under the following realistic scenarios:

- 1) uneven parasitic inductance;

- 2) device-temperature imbalance.

In general, the current paths of the paralleled devices in a power module are designed equally in length. Also, each device should have no significant difference in parasitic inductance. In reality, due to layout constraints, the current paths become unequal, and differences in parasitic inductance are unavoidable [16], [19], affecting the current imbalance and the dominant parameter selection. Additionally, changing the device temperature during the continuous converter operation changes the characteristics of each device, increasing the effect of the current imbalance.

To evaluate these effects, we performed additional simulations. The same circuit given in Table IX with n = 10 is used for SiC MOSFETs with the following uneven parasitic inductances in Fig. 2:

$$L_{gi} = L_{di} = L_{si} = i \, \mathrm{nH} \ (i = 1, \dots, n).$$

(31)

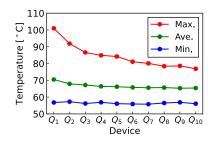

For example, the inductances of  $Q_1$  and  $Q_{10}$  are 1.0 nH and 10 nH, respectively. This imbalance causes the larger current to flow for the devices with smaller numbers. To account for the device temperature imbalance, we assumed that the power module is in a continuous converter operation at the switching frequency of  $f_{sw} = 10$  kHz. We assumed that each paralleled device has a thermal resistance  $R_{thi} = 1.0$  °C/W (i = 1, ..., n). The temperature  $T_i$  of each device  $Q_i$  is given as

Fig. 12. Maximum, mean, and minimum device temperatures obtained by the MCSIM when considering uneven parasitic inductances and temperature imbalance simultaneously.

Fig. 13. Variations of the simulated current waveform of  $Q_1$  and  $Q_{10}$  of the SiC MOSFETs obtained by the MCSIM considering uneven parasitic inductances and temperature imbalance.

follows:

$$T_i = E_i \cdot f_{\rm sw} \cdot R_{\rm th} + T_{\rm a} \quad (i = 1, \dots, n). \tag{32}$$

Here, we set  $T_a = 50$  °C. Temperature dependence of the SiC MOSFET model was considered with the parameters **VF-BCS**, **KS**, **RDS**, and **THETAS** in (25)–(28). We extracted these parameters from  $I_d$ – $V_{ds}$  characteristics of the 300 SiC MOSFETs at  $T_a = 75$  and 125 °C in Fig. 5. We used the SA method for the parameter extraction, and Table VIII presents the mean and standard deviation of the extracted parameters. The measured and modeled  $I_d$ – $V_{ds}$  characteristics agree well for  $T_a = 75$  and 125 °C with an average RMSE of 0.47 A.

As the device temperature changes, the energy loss of the devices changes due to the change in the characteristics. Furthermore, the change in energy loss alters the device temperature. To solve this interdependence accurately, the circuit simulation and the temperature calculation in (32) were repeated alternatively until  $E_i$  and  $T_i$  converged for all the devices.

Fig. 12 shows the maximum, the mean, and the minimum values of device temperature. Expectedly,  $Q_1$  exhibited the highest temperature, and  $Q_{10}$  exhibited the lowest. The difference between the maximum and the minimum temperature is higher than 40 °C in  $Q_1$ . The characteristic variation of the paralleled devices causes a significant temperature imbalance. Fig. 13 shows the simulated current waveforms of  $Q_1$  and  $Q_{10}$ . Due to the uneven parasitic inductances and temperature imbalance, the current imbalance among devices is evident.

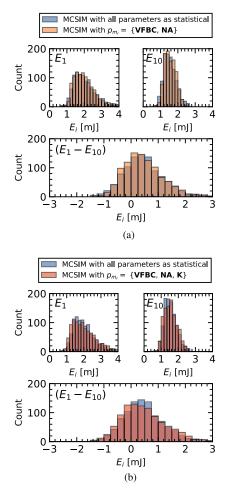

We validated the determined dominant model parameters of the SiC MOSFETs when considering the uneven parasitic inductances and temperature imbalance. Fig. 14(a) shows the histograms of  $E_1$ ,  $E_{10}$ , and  $(E_1 - E_{10})$  obtained by the MCSIM

Fig. 14. Variations of  $E_1$ ,  $E_{10}$ , and  $(E_1 - E_{10})$  obtained by the MCSIM. (a)  $p_{m_r} = \{ VFBC, NA \}$ . (b)  $p_{m_r} = \{ VFBC, NA, K \}$ .

with  $p_{m_r} = \{VFBC, NA\}$ . Here,  $(E_1 - E_{10})$  indicates the energy loss difference of  $Q_1$  and  $Q_{10}$  on the same power module. The determined model parameters reproduced the energy loss adequately.

Compared to the case not considering the nonidealities, the standard deviation errors and the range of energy loss difference  $(E_1 - E_{10})$  increased to 14.8% and 19.4%, respectively. For more accurate estimation, we reselected dominant parameters with a smaller  $err_{accept}$  of 5%. As shown in Fig. 9(b), the parameters {**VFBC**, **NA**, **K**} were selected. Fig. 14(b) shows the results of applying the determined dominant model parameters. The selected model parameters reproduced each energy loss variation well, improving the accuracy of the standard deviation and the range error to 0.82% and 0.91%, respectively.

We conclude that the dominant parameters determined by the proposed method are valid for practical situations when nonideal conditions such as uneven parasitic inductance and temperature imbalance are considered.

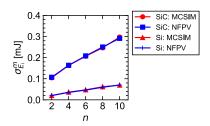

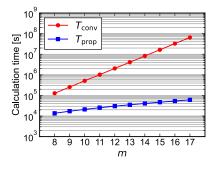

4) Calculation Time: We evaluated the calculation time required to extract the dominant parameters by the conventional and proposed methods using (2) and (15). Table IX summarizes the conditions used in calculating  $T_{\rm conv}$  and  $T_{\rm prop}$ . We set the value of  $T_{\rm cir}$  to be the typical value of the circuit

Fig. 15. Comparison of the calculation times for the conventional MC-based method and the proposed NFPV-based method with varied model parameters m. The quantities  $T_{\rm conv}$  and  $T_{\rm prop}$  are the calculation times for the conventional and proposed methods, respectively.

simulation shown in Fig. 2. We performed each MCSIM circuit simulation for  $L_{\rm max} = 100$  iterations. On average, the time required to calculate the NFPV equation was  $T_{\rm NFPV} = 1.8$  ms. The calculations showed that  $T_{\rm conv} \approx 127,000$  s and  $T_{\rm prop} \approx$ 13,600 s. Within  $T_{\rm prop}$ , the iteration time for calculating the NFPV equation was less than 1.0 s, which was negligibly small. Consequently, the proposed method can extract the dominant model parameters 9.33 times faster than the conventional method.

We compared  $T_{\rm conv}$  and  $T_{\rm prop}$  when different numbers of model parameters were considered. The number of candidate statistical model parameters was eight in the example shown in the previous section. In practice, larger numbers of model parameters are used in device models. For example, there are 17 model parameters for the drain current equation in the surface-potential-based SiC MOSFET model. Therefore, we need to include a larger number of model parameters to determine the dominant parameters comprehensively.

Fig. 15 compares the estimated calculation times for the conventional and the proposed methods when the number m of model parameters varies.  $T_{\text{conv}}$  increases rapidly as m increases, while  $T_{\text{prop}}$  increases slowly and has a reasonable computation time, e.g., within  $1.0 \times 10^5$  s ( $\approx 1$  day). The asymptotic complexity of  $T_{\text{conv}}$  is  $\mathcal{O}(2^m)$  due to the term  $\sum_{m=1}^{m-1} {m \choose m_r}$  [39], and the computation time increases exponentially with m. Although  $T_{\text{prop}}$  has the same asymptotic complexity, its coefficient  $T_{\text{NFPV}}$  is about  $10^5$  times smaller than that in  $T_{\text{conv}}$ . Therefore, for the practical range of m,  $T_{\text{prop}}$  is dominant regarding execution time and grows considerably smaller in the order of  $m^2$ . We conclude that the proposed method is more effective than the conventional method when there are many model parameters.

#### V. CONCLUSION

In this article, we have proposed a quick method for determining the model parameters that contribute significantly to the current imbalance in paralleled power transistors. The proposed NFPV-based method accurately estimates the energyloss variation of paralleled devices. In an experimental validation using measured  $I_d$ - $V_{ds}$  characteristics of commercially available 100 Si MOSFETs and 300 SiC MOSFETs, the proposed method efficiently determined the dominant model parameters, regardless of the device types and number of paralleled devices. We validated the dominant model parameters under the practical situations with uneven parasitic inductances and device temperature imbalance among paralleled devices in the power module. The proposed method determined the dominant model parameters  $9.33 \times$  faster than the conventional method. We also demonstrated that, compared to the conventional method, an increase in the number of candidate statistical model parameters enhances the efficiency of the proposed method.

The proposed method rapidly determines the dominant parameters using the NFPV equation. However, this equation assumes that the second-order sensitivity of the model parameters is insignificant. The proposed method also requires that the correlation between model parameters must be known. Our future work includes dominant parameter determination when the above assumptions do not hold.

#### REFERENCES

- Y. Nakamura, M. Shintani, and T. Sato, "Dominant model parameter extraction for analyzing current imbalance in parallel connected SiC MOS-FETs," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2021, pp. 5622–5628.

- [2] T. Kimoto, "Material science and device physics in SiC technology for high-voltage power devices," *Jpn. J. Appl. Phys.*, vol. 54, no. 4, 2015, Art. no. 040103.

- [3] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications. Hoboken, NJ, USA: Wiley, 2014.

- [4] B. J. Baliga, Fundamentals of Power Semiconductor Devices. Berlin, Germany: Springer, 2008.

- [5] J. Millán, P. Godignon, X. Perpinà, A. Pérez-Tomás, and J. Rebollo, "A survey of wide bandgap power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155–2163, May 2014.

- [6] J. Zhu, H. Kim, and H. Chen, "High efficiency SiC traction inverter for electric vehicle applications," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2018, pp. 1428–1433.

- [7] W. Zhou, Q. Quo, X. Wu, Y. Liu, and K. Sheng, "A 1200 V/100 A all-sic power module for boost converter of EV/HEV's motor driver application," in *Proc. China Int. Forum Solid State Lighting, Int. Forum Wide Bandgap Semicond. China*, 2016, pp. 38–41.

- [8] Z. Liu, B. Li, F. C. Lee, and Q. Li, "High-efficiency high-density critical mode rectifier/inverter for WBG-device-based on-board charger," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 9114–9123, 2017.

- [9] E. Gurpinar et al., "SiC MOSFET-based power module design and analysis for EV traction systems," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2018, pp. 1722–1727.

- [10] D. P. Sadik, J. Colmenares, D. Peftitsis, J. K. Lim, J. Rabkowski, and H. P. Nee, "Experimental investigations of static and transient current sharing of parallel-connected silicon carbide MOSFETs," in *Proc. Eur. Conf. Power Electron. Appl.*, 2013, pp. 1–10.

- [11] C. Hui, Y. Yang, Y. Xue, and Y. Wen, "Research on current sharing method of SiC MOSFET parallel modules," in *Proc. IEEE Int. Conf. Electron Devices Solid State Circuits*, 2018, pp. 1–2.

- [12] G. Wang, J. Mookken, J. Rice, and M. Schupbach, "Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2014, pp. 1478–1483.

- [13] J. Tu, H. Ben, T. Meng, Z. Yao, J. Ning, and H. Yu, "Research on parallel current sharing scheme of 1200 V/100 A SiC MOSFET," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2019, pp. 1–4.

- [14] H. Li et al., "Influences of device and circuit mismatches on paralleling silicon carbide MOSFETs," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 621–634, Jan. 2016.

- [15] R. Horff, T. Bertelshofer, A. Marz, and M. M. Bakran, "Current mismatch in paralleled phases of high power SiC modules due to threshold voltage unsymmetry and different gate-driver concepts," in *Proc. IEEE Eur. Conf. Power Electron. Appl.*, 2016, pp. 1–9.

- [16] J. Hu et al., "Robustness and balancing of parallel-connected power devices: SiC versus CoolMOS," *IEEE Trans. Ind. Electron.*, vol. 63, no. 4, pp. 2092–2102, Apr. 2016.

- [17] M. Riccio et al., "Analysis of device and circuit parameters variability in SiC MOSFETs-based multichip power module," in *Proc. IEEE Eur. Conf. Power Electron. Appl.*, 2018, pp. 1–9.

- [18] K. Shimozato, M. Shintani, and T. Sato, "Adaptive outlier detection for power MOSFETs based on Gaussian process regression," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2022, pp. 1709–1714.

- [19] H. Li, S. Munk-Nielsen, C. Pham, and S. Beczkowski, "Circuit mismatch influence on performance of paralleling silicon carbide MOSFETs," in *Proc. IEEE Eur. Conf. Power Electron. Appl.*, 2014, pp. 1–8.

- [20] A. Borghese et al., "Statistical analysis of the electrothermal imbalances of mismatched parallel SiC power MOSFETs," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 3, pp. 1527–1538, Sep. 2019.

- [21] H. Li et al., "Influence of paralleling dies and paralleling half-bridges on transient current distribution in multichip power modules," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 6483–6487, Aug. 2018.

- [22] J. Muting, N. Schneider, T. Ziemann, R. Stark, and U. Grossner, "Exploring the behavior of parallel connected SiC power MOSFETs influenced by performance spread in circuit simulations," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2018, pp. 280–286.

- [23] Y. Zhang et al., "Current sharing analysis of SiC power modules in parallel operation," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2020, pp. 711– 716.

- [24] G. Gildenblat et al., "PSP: An advanced surface-potential-based MOSFET model for circuit simulation," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 1979–1993, Sep. 2006.

- [25] Y. Oritsuki et al., "HiSIM-HV: A compact model for simulation of highvoltage MOSFET circuits," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2671–2678, Oct. 2010.

- [26] H. Agarwal et al., "BSIM-HV: High-voltage MOSFET model including quasi-saturation and self-heating effect," *IEEE Trans. Electron Devices*, vol. 66, no. 10, pp. 4258–4263, Oct. 2019.

- [27] H. Li, X. Zhao, K. Sun, Z. Zhao, G. Cao, and T. Q. Zheng, "A nonsegmented PSpice model of SiC MOSFET with temperature-dependent parameters," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4603–4612, May 2019.

- [28] M. Shintani, Y. Nakamura, K. Oishi, M. Hiromoto, T. Hikihara, and T. Sato, "Surface-potential-based silicon carbide power MOSFET model for circuit simulation," *IEEE Trans. Power Electron.*, vol. 33, no. 12, pp. 10 774–10 783, Dec. 2018.

- [29] H. Tsukamoto, M. Shintani, and T. Sato, "Statistical extraction of normally and lognormally distributed model parameters for power MOS-FETs," *IEEE Trans. Semicond. Manuf.*, vol. 33, no. 2, pp. 150–158, May 2020.

- [30] D. Chiozzi, M. Bernardoni, N. Delmonte, and P. Cova, "A neural network based approach to simulate electrothermal device interaction in SPICE environment," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4703–4710, May 2019.

- [31] P. Yang, W. Ming, J. Liang, I. Lüdtke, S. Berry, and K. Floros, "Hybrid datadriven modeling methodology for fast and accurate transient simulation of SiC MOSFETs," *IEEE Trans. Power Electron.*, vol. 37, no. 1, pp. 440–451, Jan. 2022.

- [32] C. C. McAndrew, "Statistical modeling for circuit simulation," in *Proc. IEEE Int. Symp. Qual. Electron. Des.*, 2003, pp. 1–6.

- [33] N. Telang and J. M. Higman, "Statistical modeling techniques: FPV vs. BPV," in Proc. Int. Conf. Microelectronic Test Struct., 2003, pp. 71–75.

- [34] T. Sakurai and A. R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," *IEEE J. Solid-State Circuits*, vol. 25, no. 2, pp. 584–594, Apr. 1990.

- [35] Z. Zheng, A. Lenze, D. Levett, K. Mainka, and M. Zhang, "A practical example of hard paralleling SiC MOSFET modules," in *Proc. PCIM Asia*; *Int. Exhib. Conf. Power Electron., Intell. Motion, Renew. Energy Energy Manage.*, 2019, pp. 108–114.

- [36] HSPICE User Guide: Simulation and Analysis, Synopsys, 2014.

- [37] M. Shintani, H. Tsukamoto, and T. Sato, "Parameter extraction procedure for surface-potential-based SiC MOSFET model," in *Proc. IEEE Work*shop Wide Bandgap Power Devices Appl., 2019, pp. 444–448.